一、什么是时序约束

用来描述设计人员对于时序设计的要求,比如时钟频率,输入输出的延时等。设计者需要告诉 EDA 工具,设计中所使用的时钟的频率是多少,然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。一般只用对输入时钟做约束

二、什么时候需要做时序约束

要根据工程复杂度来进行确定,对于功能比较简单,时钟频率比较低(如流水灯,数码管,蜂鸣器等)不用做时序约束,对于网口通信,千兆网通信等时钟要求比较高的工程,则需要进行时序约束;

当工程占用芯片逻辑资源较多的时候,尽管此时时钟频率仍然不是很高,但也要做时钟约束;

当功能出错且是由于时序不满足导致的时候。

三、建立时间与保持时间

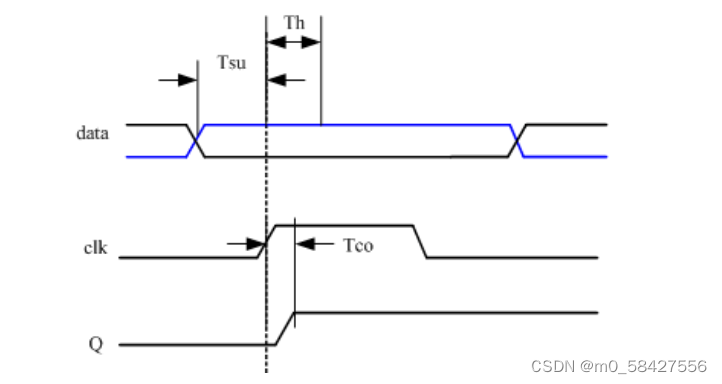

(1)建立时间(Tsu:setup)

假设是时钟上升沿触发,则建立时间是指在时钟上升沿来到之前,数据必须要保持的状态的最低时间,如果建立时间不够,则在时钟上升沿到来时数据不能正常被传输。

(2)保持时间(Th:hold)

同样假设是时钟上升沿触发,保持时间是指在时钟上升沿到来之后,数据必须要保持状态的最低时间,如果保持时间不够,数据同样不能被正确传输。

四、为什么要做时序约束

即使对于同一个时钟输入,由于各器件布局位置不同,导致时钟输入到器件接受有时延,出现竞争冒险。时钟约束则优先保证时延最小来进行布线,但这可能会牺牲一些面积。

五、如何创建时序约束

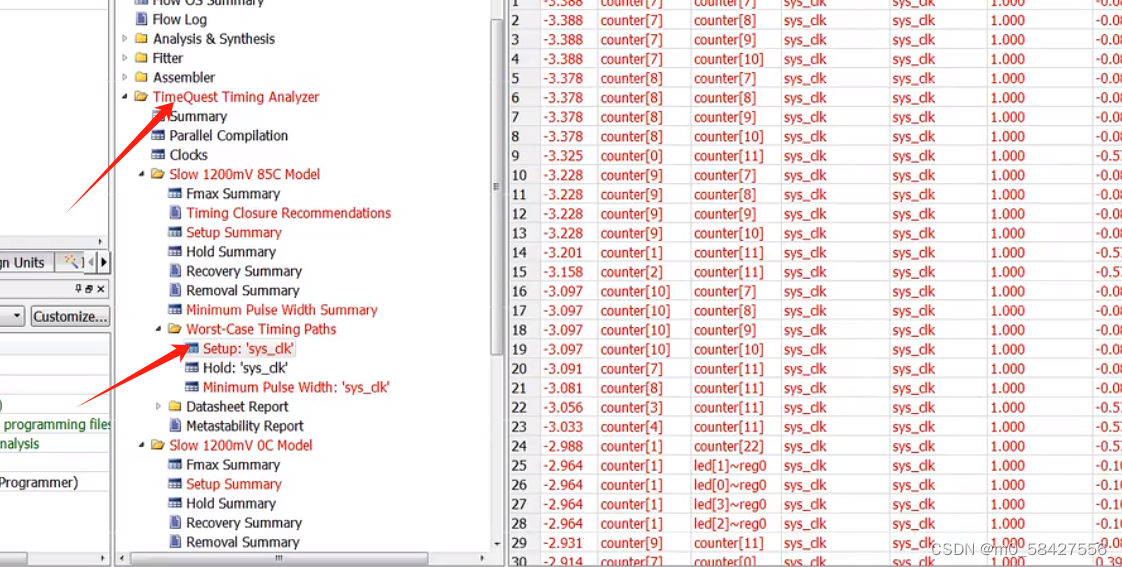

打开工程,点开编译报告

展开Time Analyzer(18.1版本以下见图)红色部分则表示时序不满足,我们这里主要关注sys_clk,

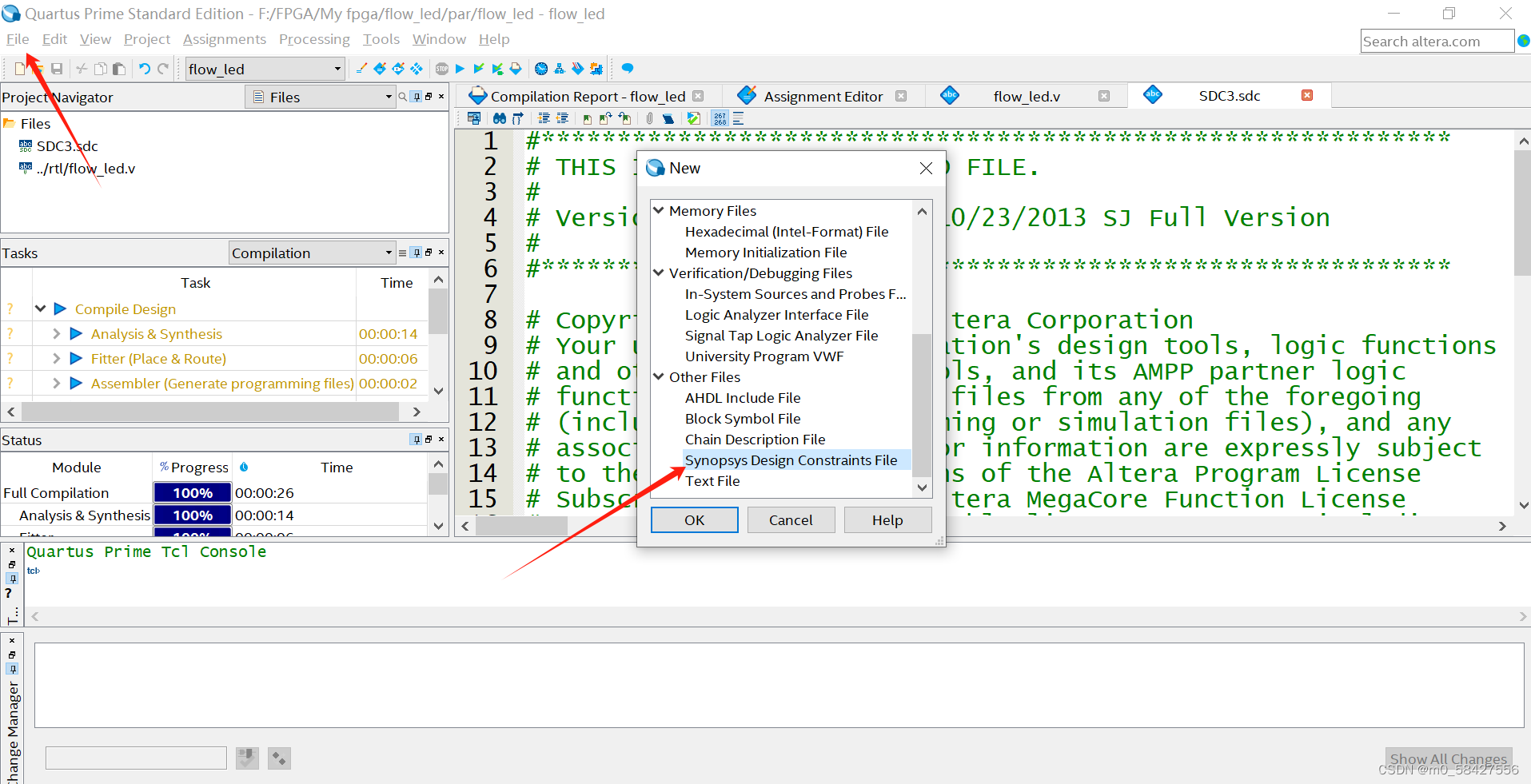

创建时序约束(方法一)

点击file——new, 会出现下面的界面,点击Synopsys Design Constraints Files创建时序约束文件,在文本编辑窗口进行时钟编辑

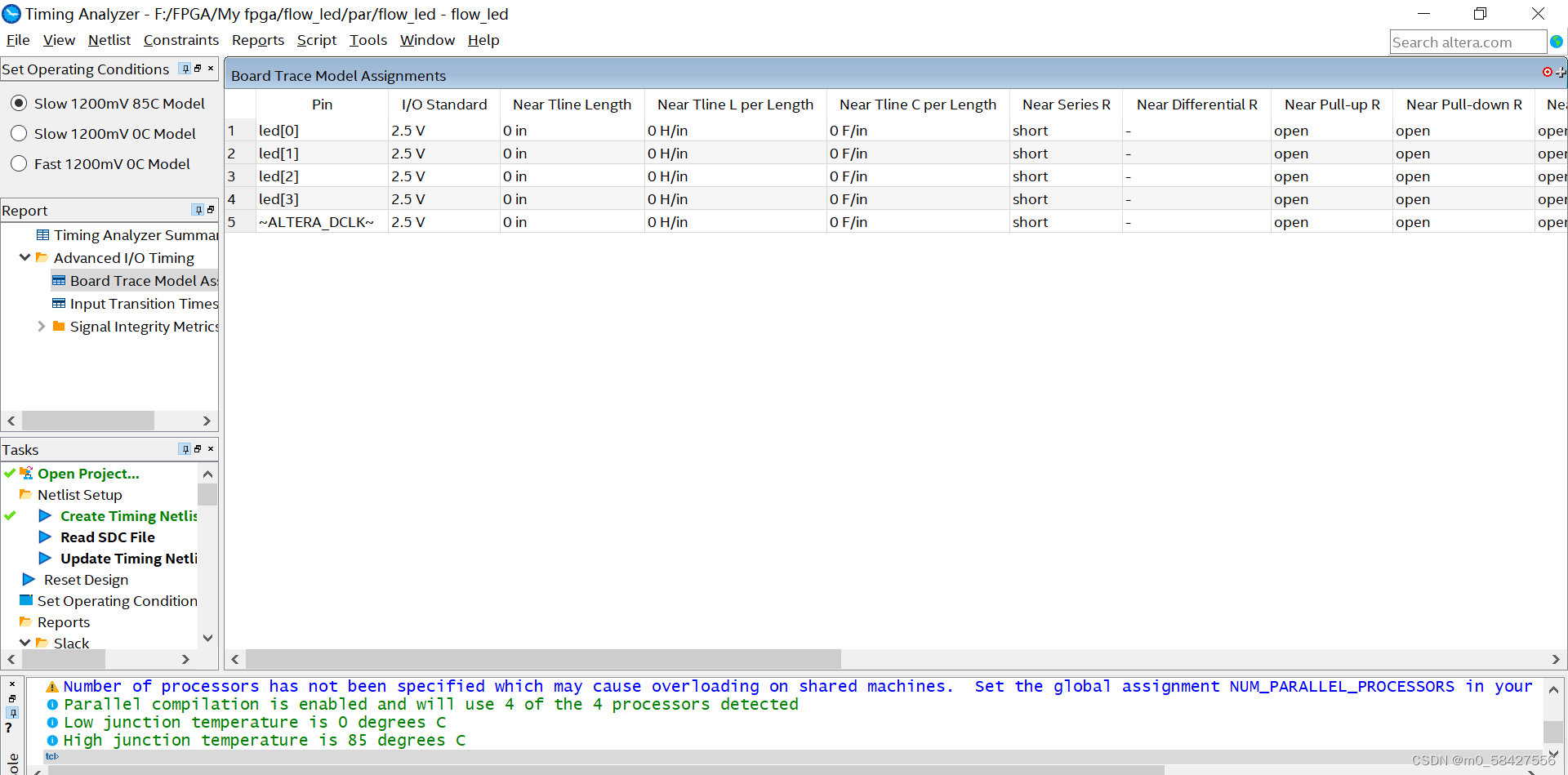

创建时序约束(方法二)

点击Tools, Timing Analyszer,出现以下界面,点击netlist ,Creating timing netlist, 选择post-may ,点击ok

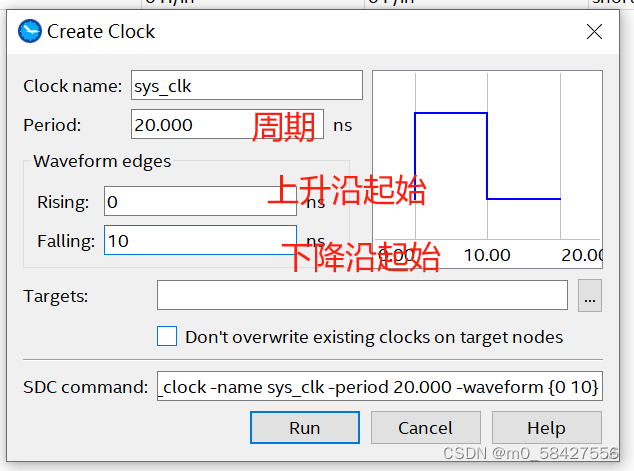

点击Constrains——creat clock,输入各参数

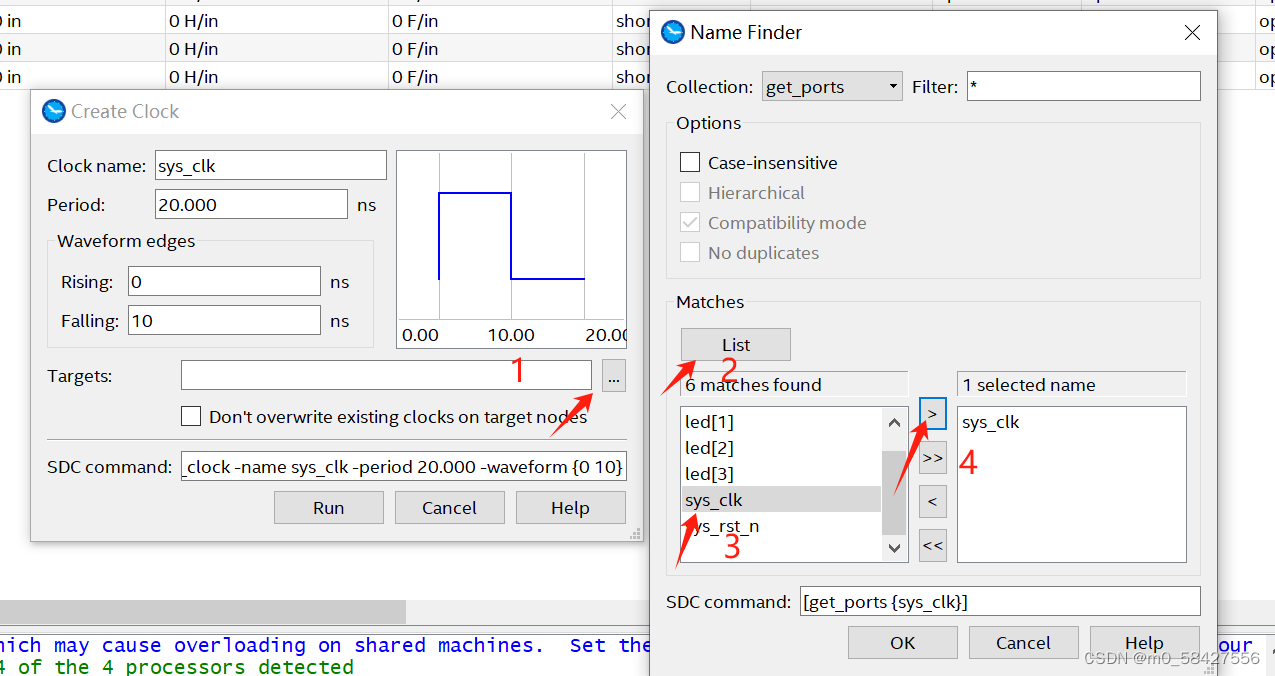

点击时钟目标target,列表,添加需要的端口

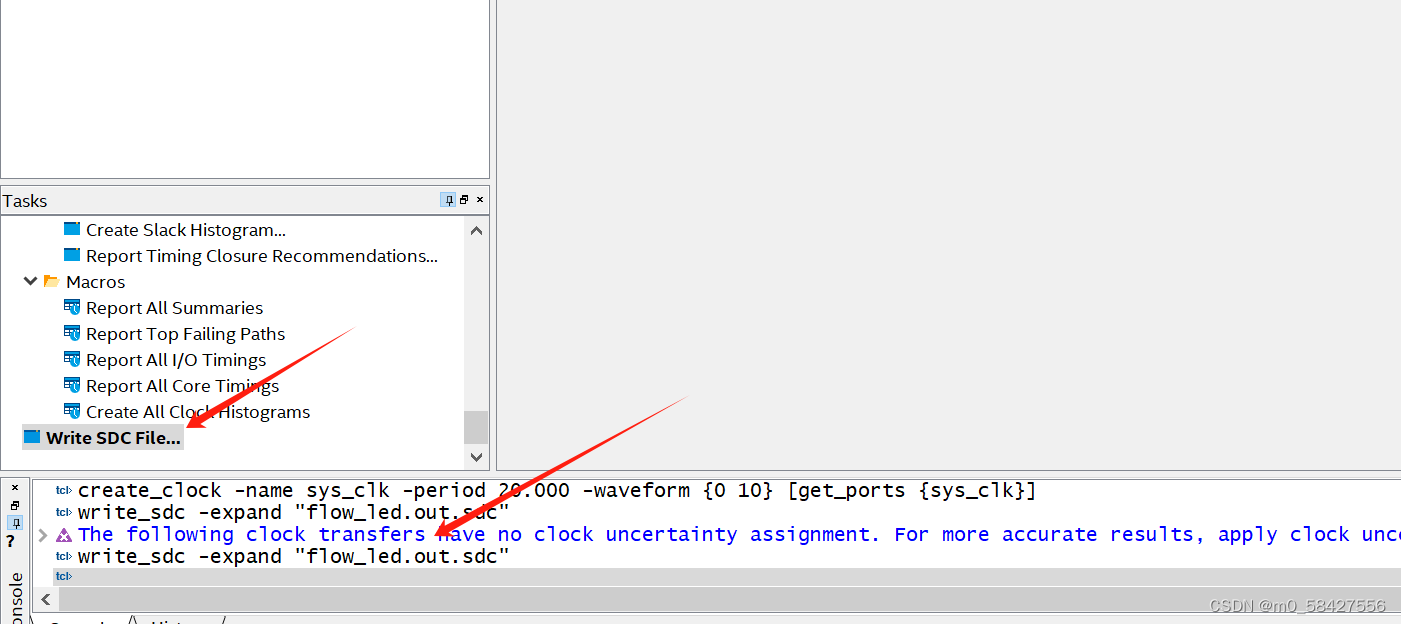

点击run ,双击弹出界面的write sdc file,然后点击OK,这样就生成了SDC文件

##本博客参考正点原子视频,如有侵权,请联系删除

1346

1346

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?