一、CMT(时钟管理单元)

在学习PLL锁相环之前,我们要先了解CMT(clock management tile)

以Xilinx 7系列FPGA 为例(ZYNQ系列中PL端结构与7系列相同)

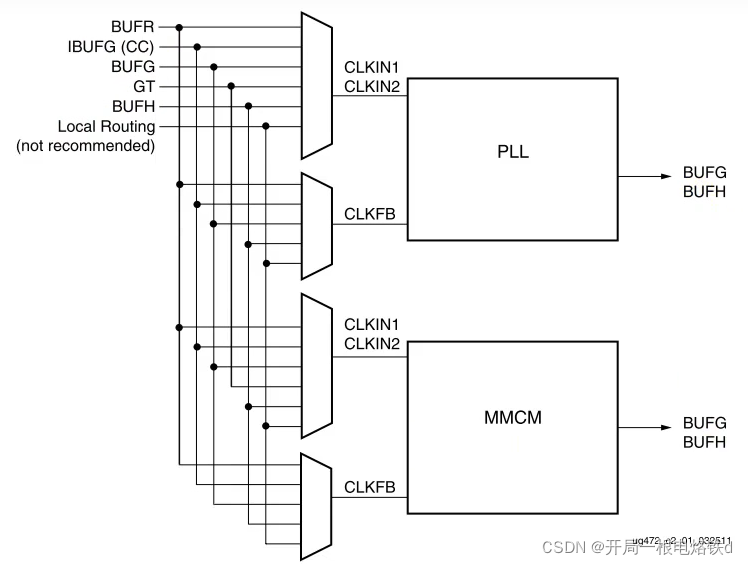

- CMT(时钟管理单元) :内部包含MMCM与PLL

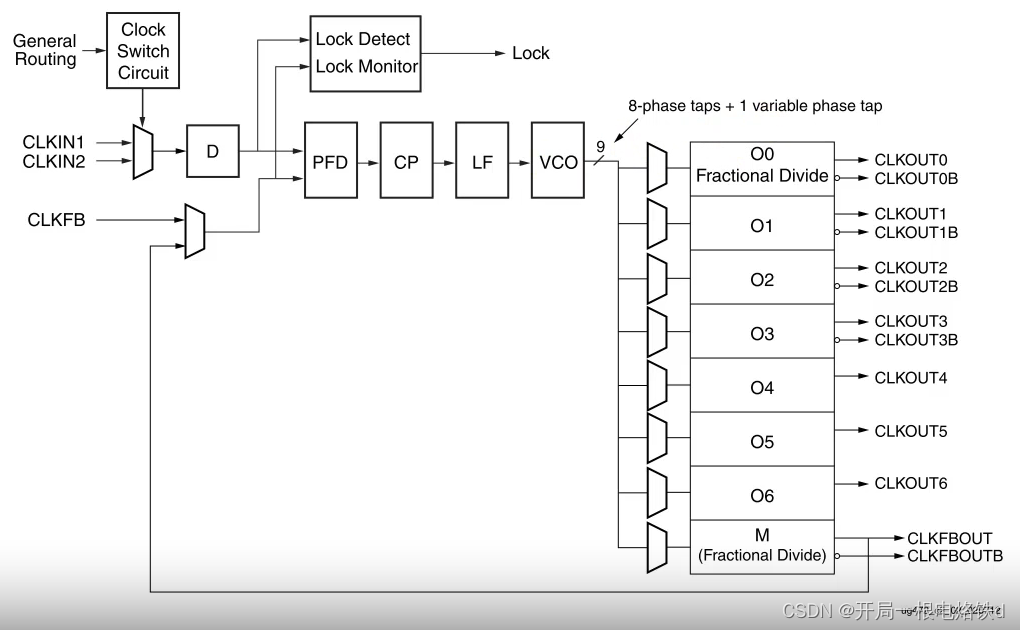

- MMCM(混合时钟管理),相比于PLL,可进行动态相位调整

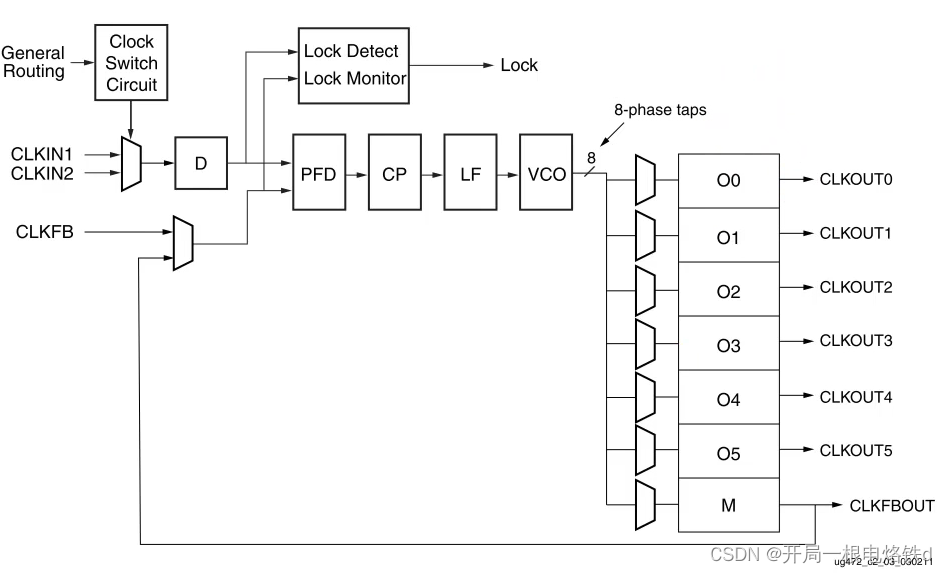

- PLL(锁相环),用于输出更广的频率范围,可看作频率合成器

CMT模块图如下,可以看到其中包含一个MMCM与一个PLL。

MMCM模块图如下,在与给定输入时钟有设定的相位和频率关系时,生成不同的时钟信号。

PLL模块图如下,使用一个PLL可以从一个输入时钟信号生成多个时钟信号。

二、PLL锁相环

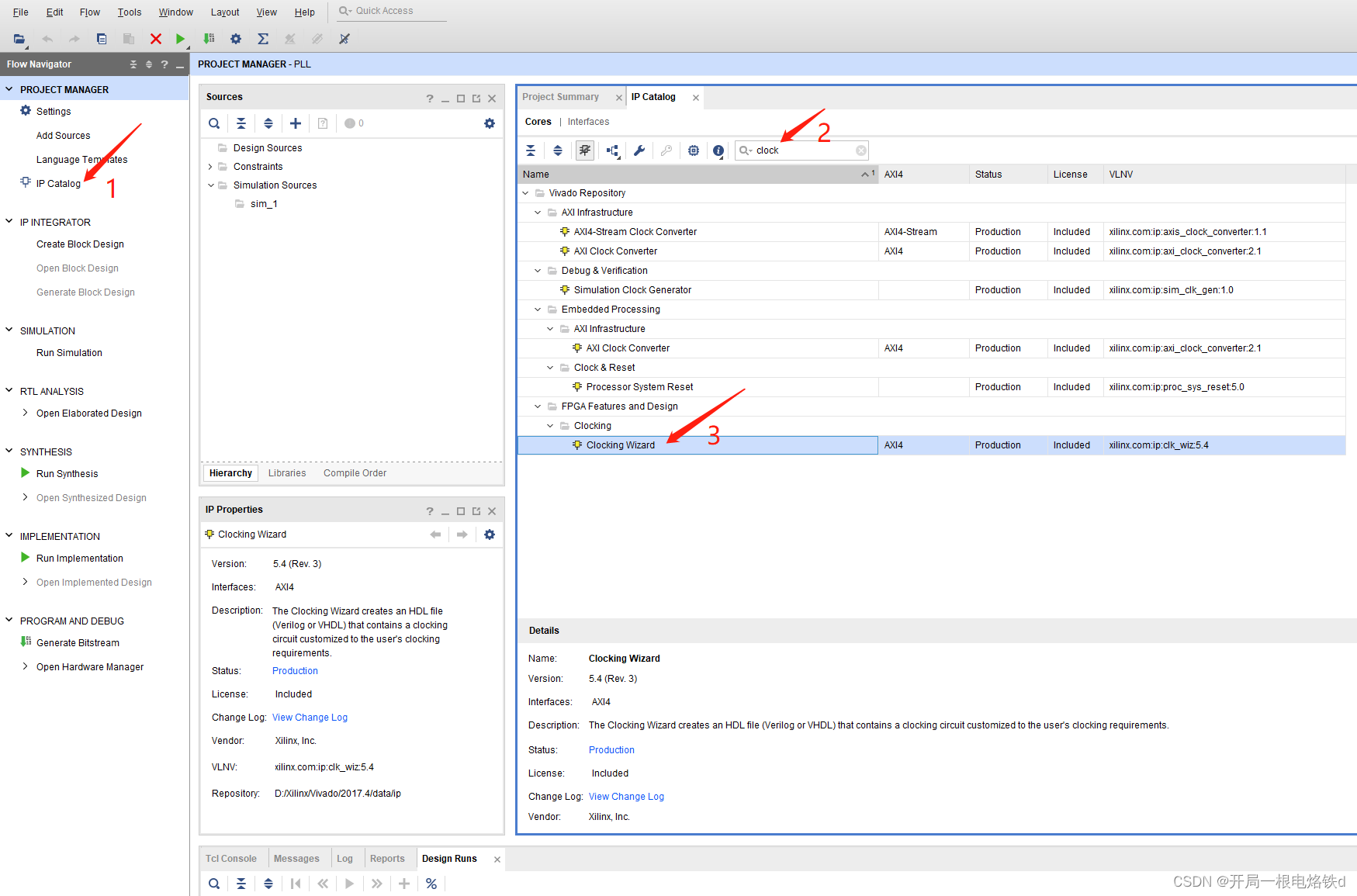

下面介绍在vivado中如何创建PLL锁相环。

- 新建vivado工程,具体过程见链接: vivado入门级指南

- 创建工程后,在项目管理目录下,选择IP Catalog,搜索“clock”:

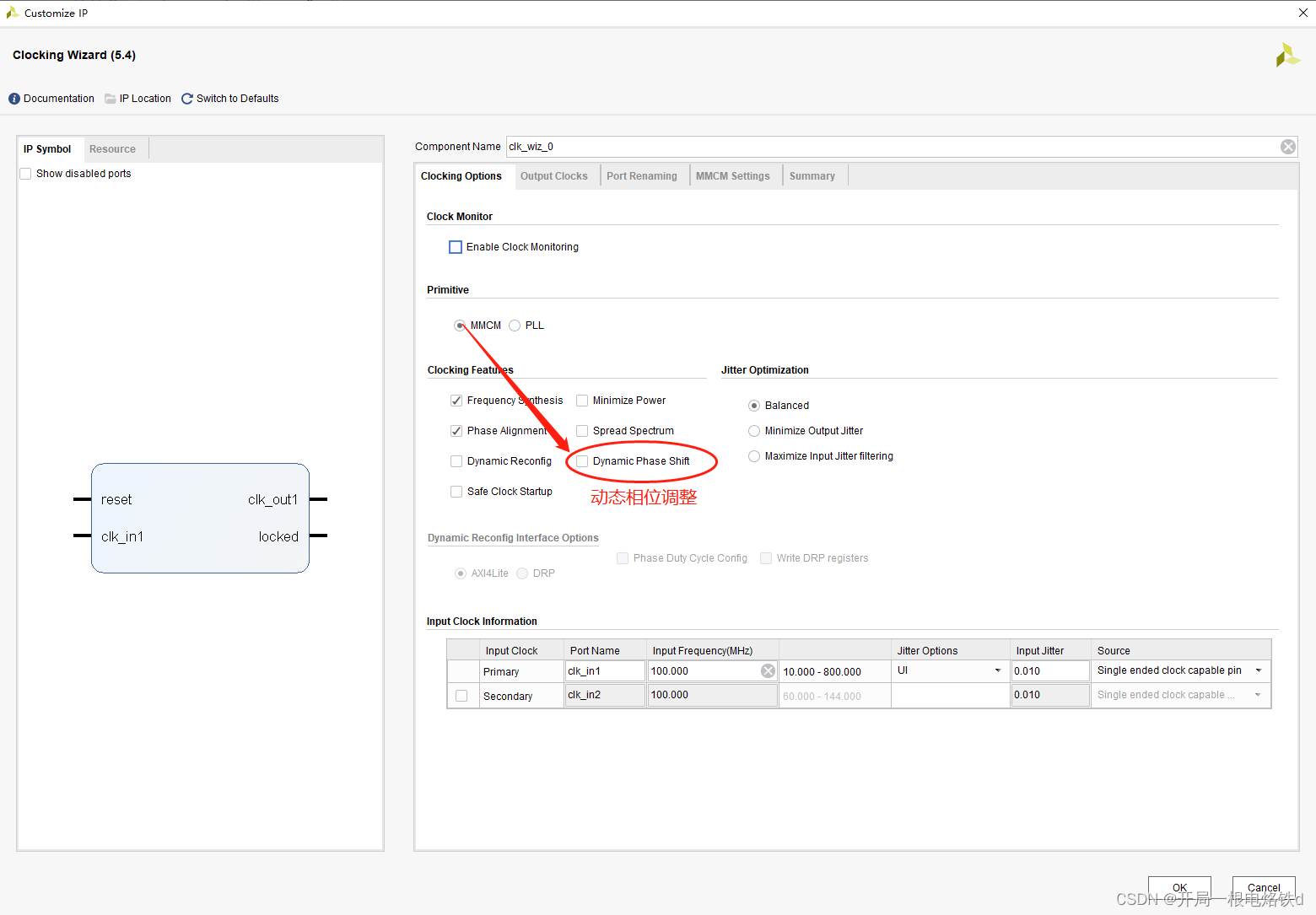

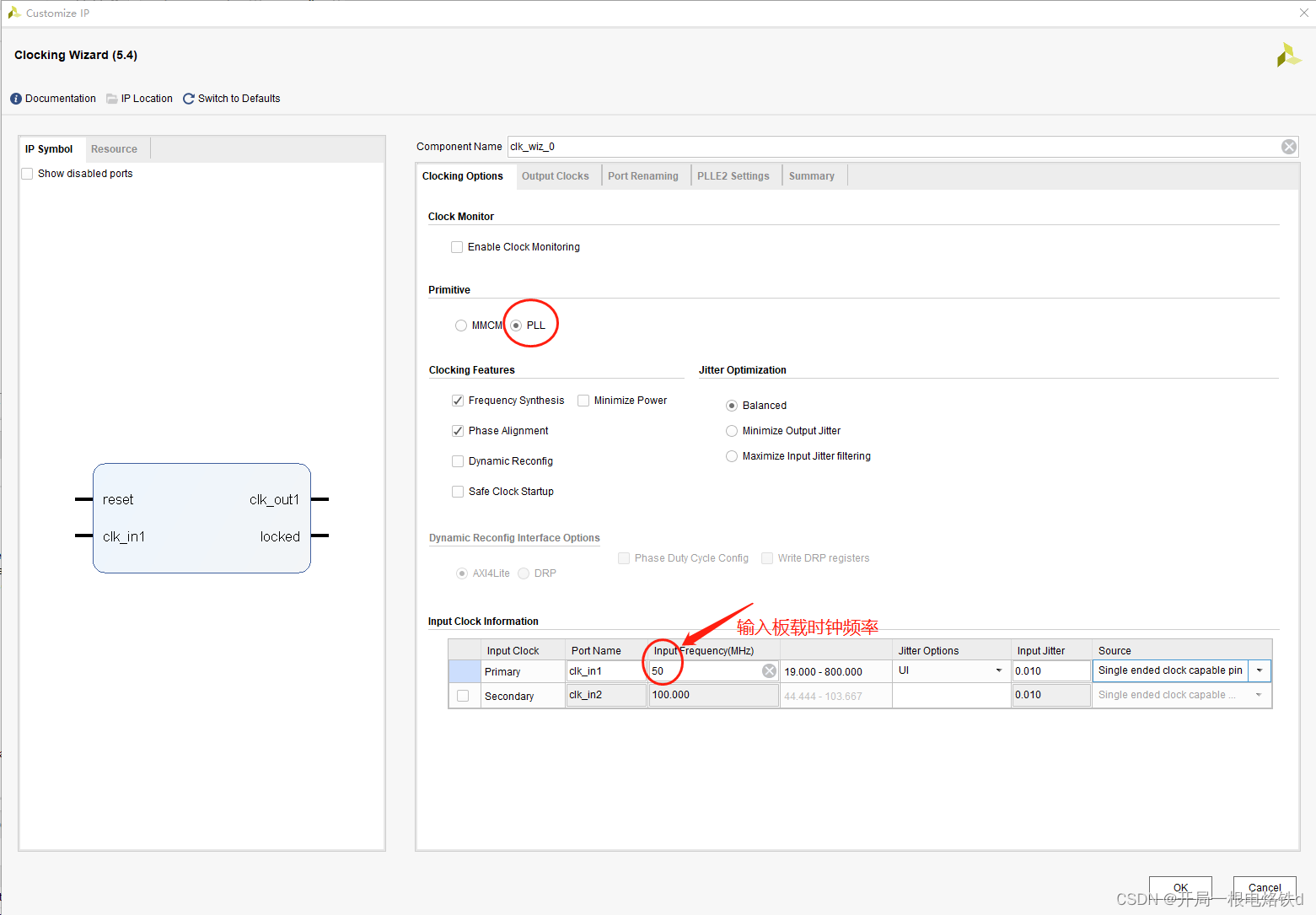

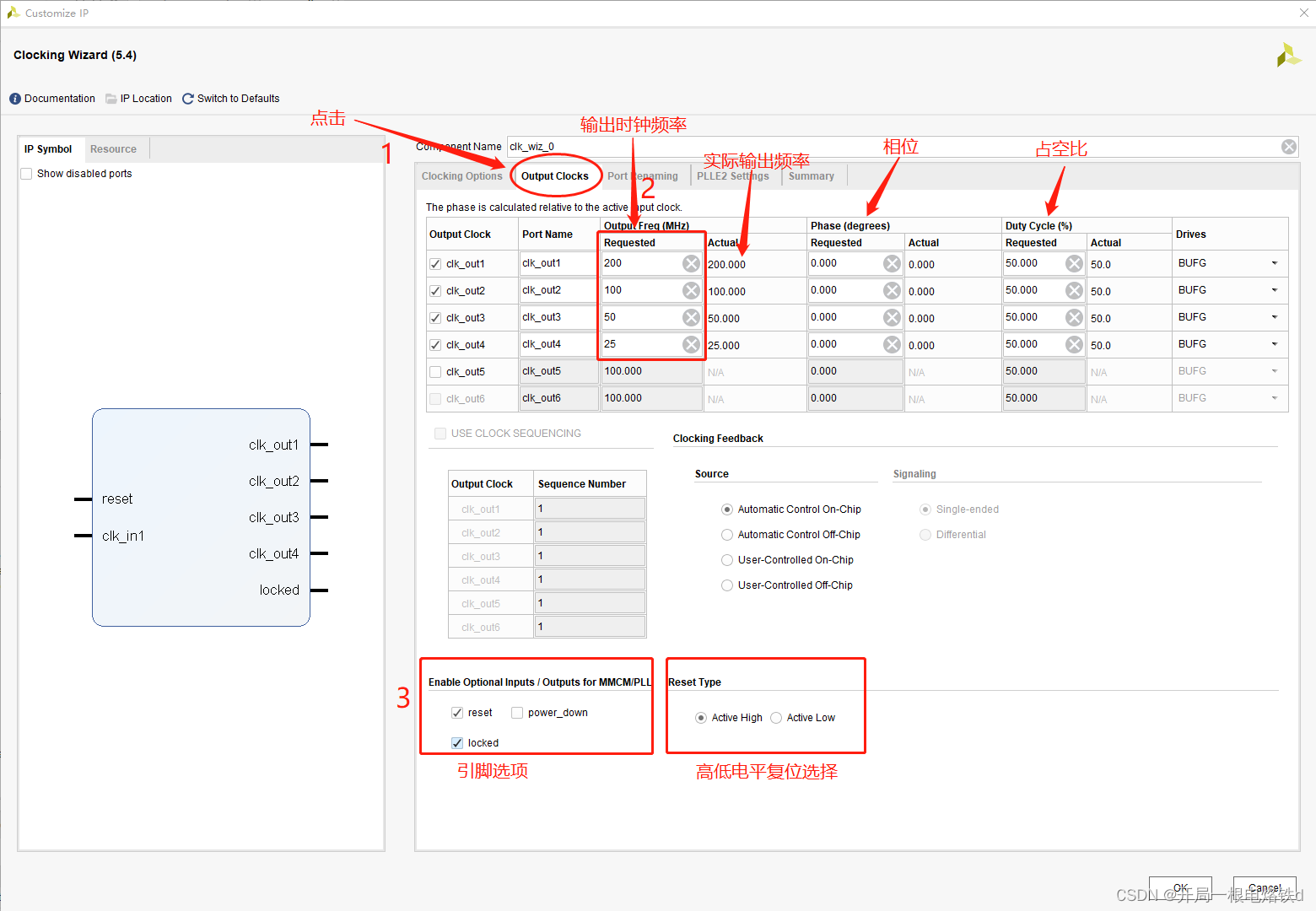

打开后可看到IP设置菜单,在MMCM下,可进行动态相位调整,切换至PLL时则无此选项:

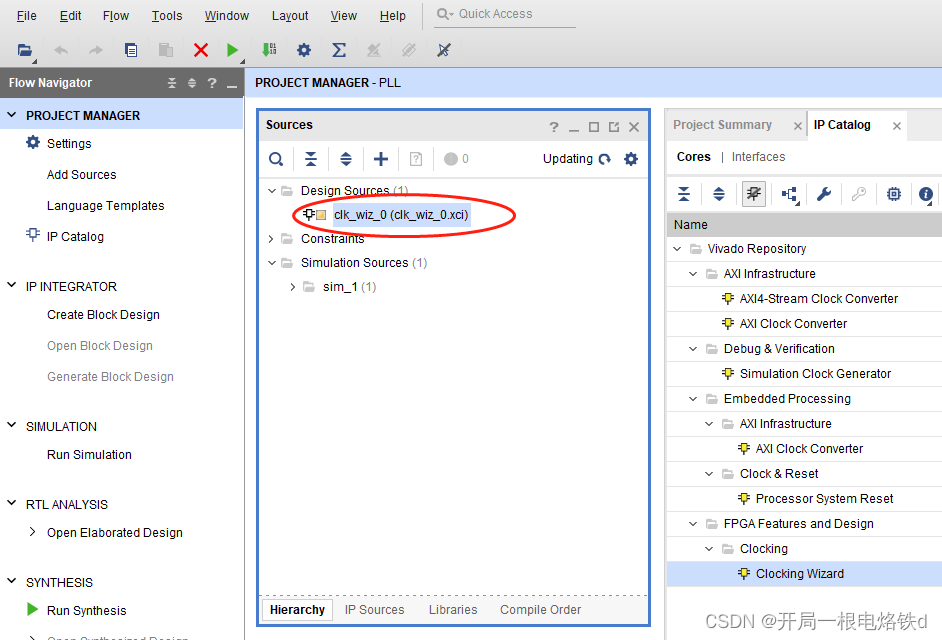

然后逐步点击设置进行生成即可,完成后会出现下图所示模块:

- 创建设计文件进行例化,具体过程见链接: vivado入门级指南

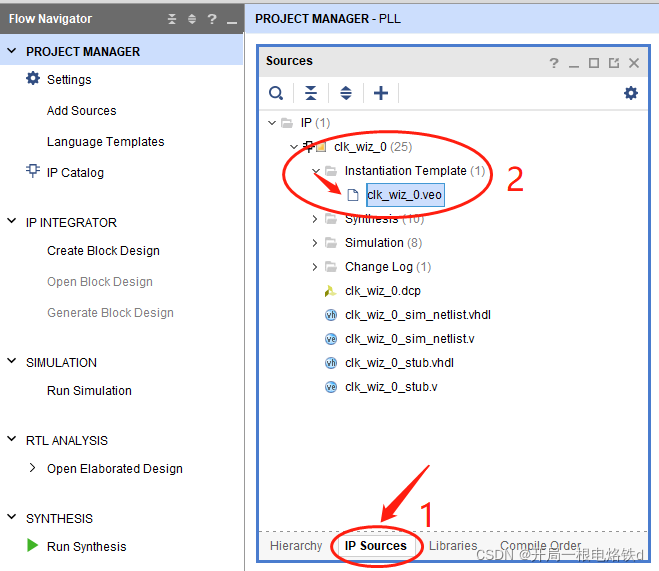

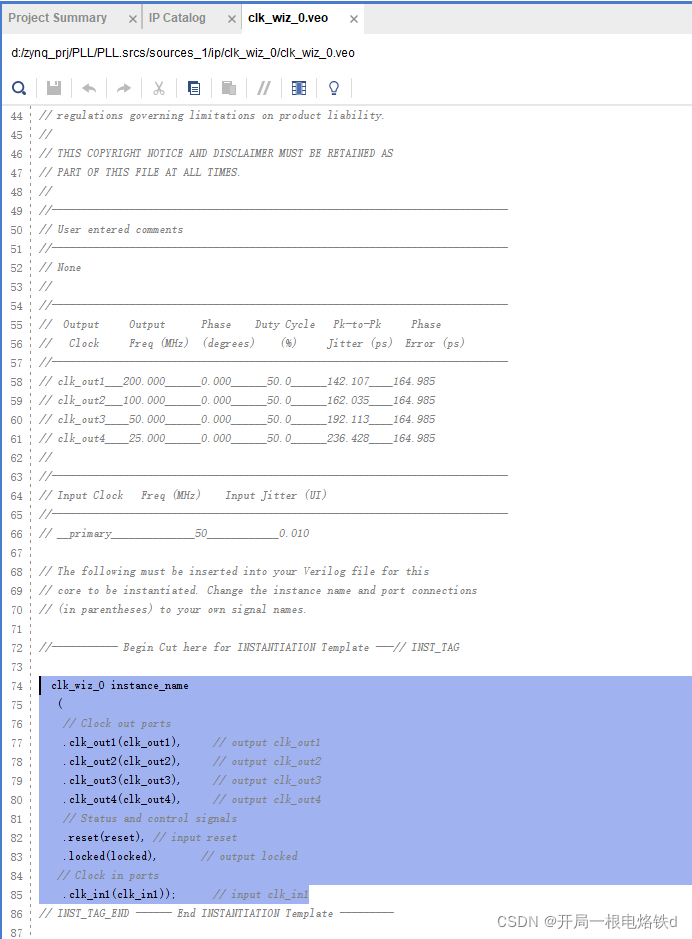

例化文件的书写我们可以查找模板,步骤如下:

打开后,将此代码段进行复制。

pll.v代码如下(只输出25MHz时钟进行测试):

module pll(

input sys_clk,

input rst_n,

output clk_out

);

wire pll_locked;

clk_wiz_0 clk_test

(

// Clock out ports

.clk_out1(), // output clk_out1

.clk_out2(), // output clk_out2

.clk_out3(), // output clk_out3

.clk_out4(clk_out), // output clk_out4

// Status and control signals

.reset(~rst_n), // input reset

.locked(pll_locked), // output locked

// Clock in ports

.clk_in1(sys_clk));

endmodule

- 创建仿真文件,过程同上,

vtf_pll.v代码如下(只输出25MHz时钟进行测试):

module vtf_pll(

);

reg sys_clk;

reg rst_n ;

wire clk_out;

pll clk_test

(

.sys_clk (sys_clk) ,

.rst_n (rst_n) ,

. clk_out(clk_out)

);

initial

begin

sys_clk = 1'b0;

rst_n = 1'b0;

#100 rst_n = 1'b1;

end

always #10 sys_clk = ~sys_clk;

endmodule

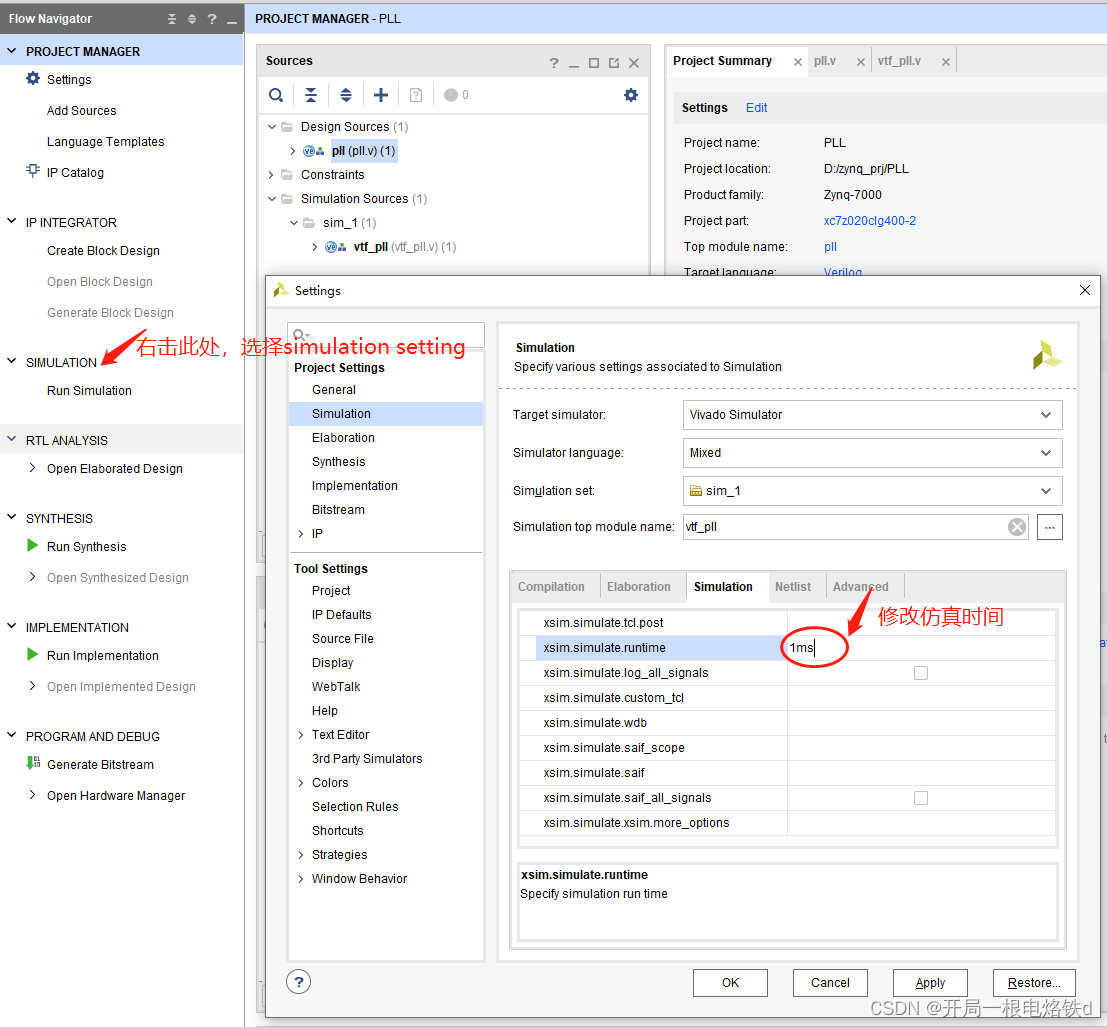

然后进行仿真。

接着运行仿真(Run Behavior Simulation),分析结果。

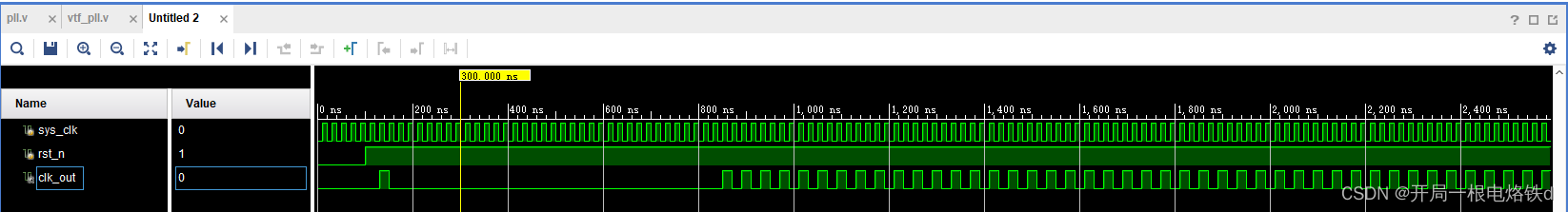

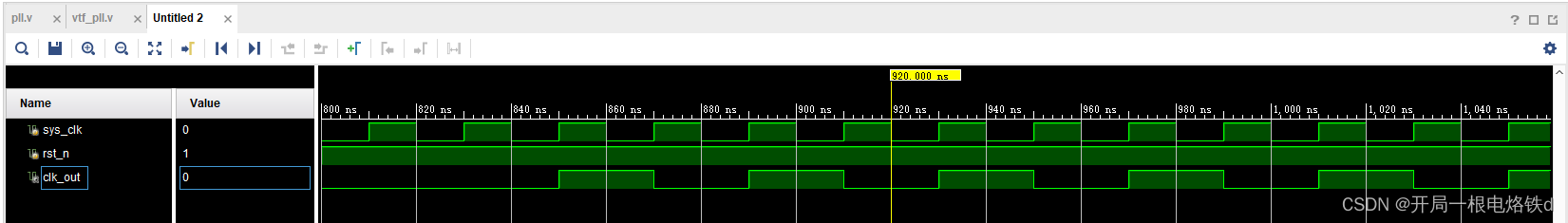

其中,前段为系统初始化和锁相环运行时间,运行稳定后,可看见clk_out进行周期性变化。

放大后半部分,可看到,输出时钟的周期是系统时钟的两倍,因此频率为其1/2,即25MHz。

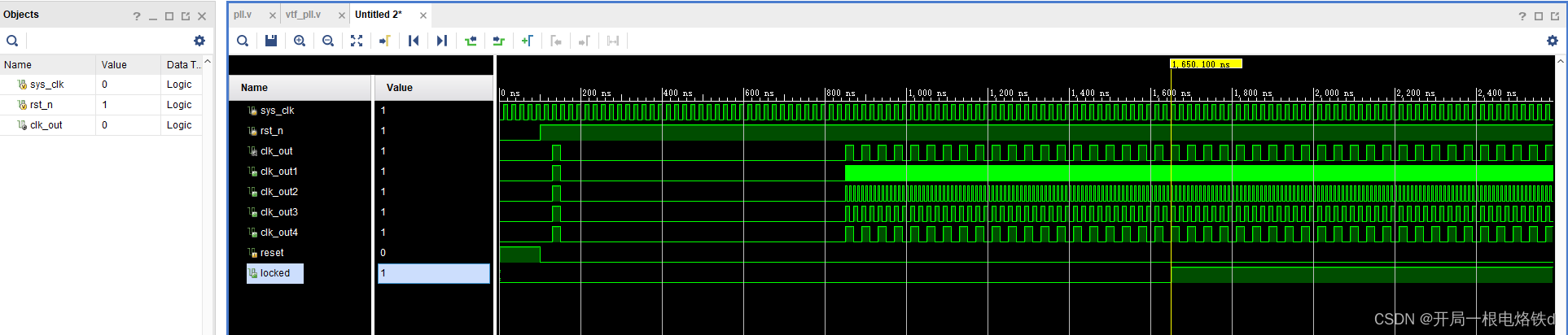

接着我们将所有信号拉入后进行测试,在locked信号处于上升沿时,此时输出的时钟才为稳定时钟,在前一段时间里,时钟可能会有抖动,无法使用,但注意,此过程时间极短。

本文参考《course_s1_ZYNQ那些事儿-FPGA实验篇V1.06》。

2023.11.23更新:

- 关于PLL的locked输出信号:起始输出为低电平,时钟信号锁存住以后拉高,由于该信号特性,工程师设计小型工程时一般将locked信号接到全局复位上。

- PLL原理:分为模拟电路和数字电路两块,首先模拟电路对系统产生时钟,然后将其倍频到几GHz,然后通过数字电路小数分频,因此可以产生用户所设置的到百分位级别的时钟频率,如30.32MHz。

本文介绍PLL锁相环在Xilinx FPGA中的配置与使用方法,包括CMT时钟管理单元的概述,PLL的创建过程及在Vivado中的实现步骤,并通过实例演示了如何生成指定频率的时钟。

本文介绍PLL锁相环在Xilinx FPGA中的配置与使用方法,包括CMT时钟管理单元的概述,PLL的创建过程及在Vivado中的实现步骤,并通过实例演示了如何生成指定频率的时钟。

1826

1826

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?