今天学习了Max+plus Ⅱ系统的基本使用,仿真顶层电路,这里还是写一个教程,供大家学习,也供自己熟悉。

一、设计输入

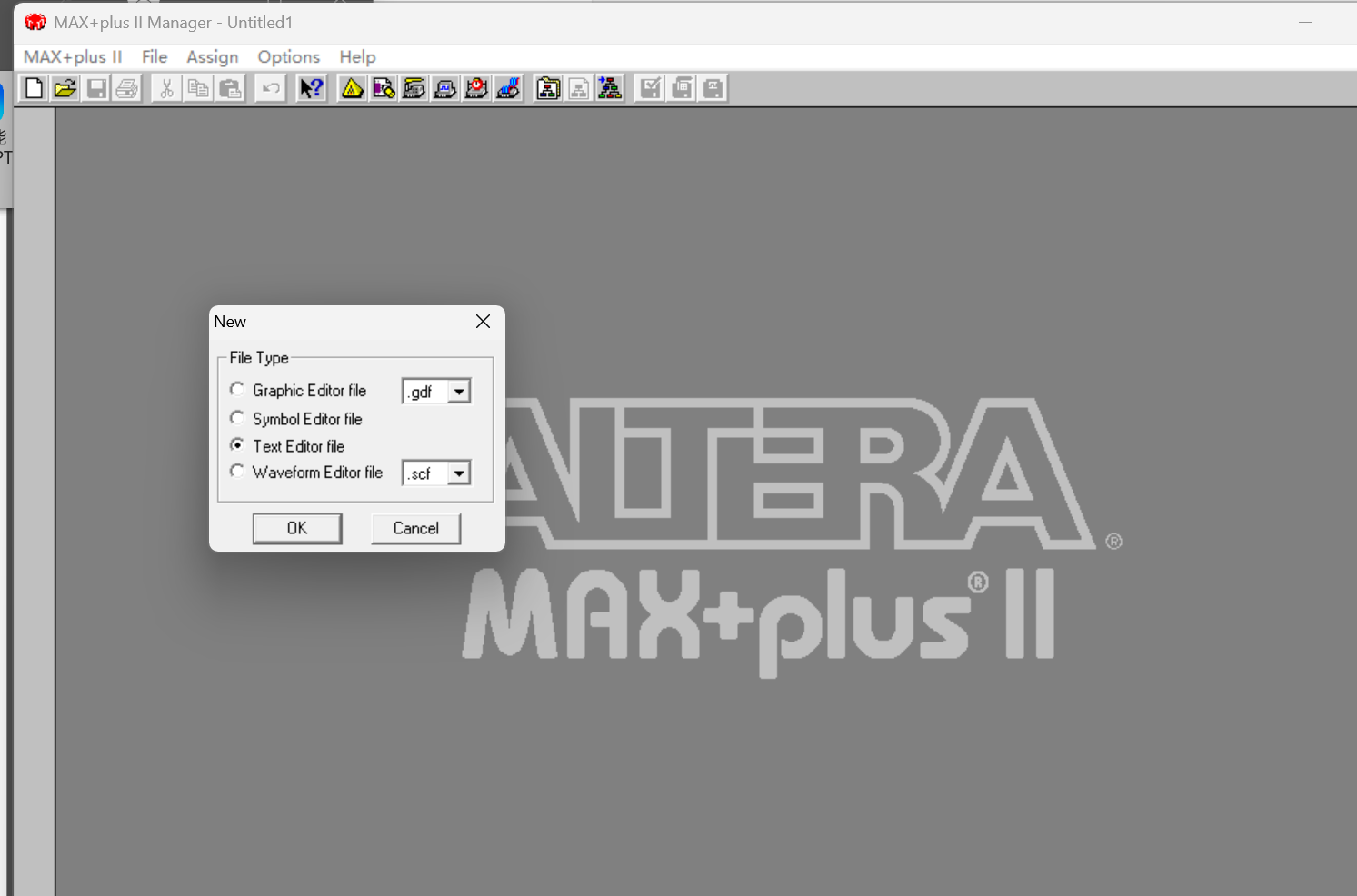

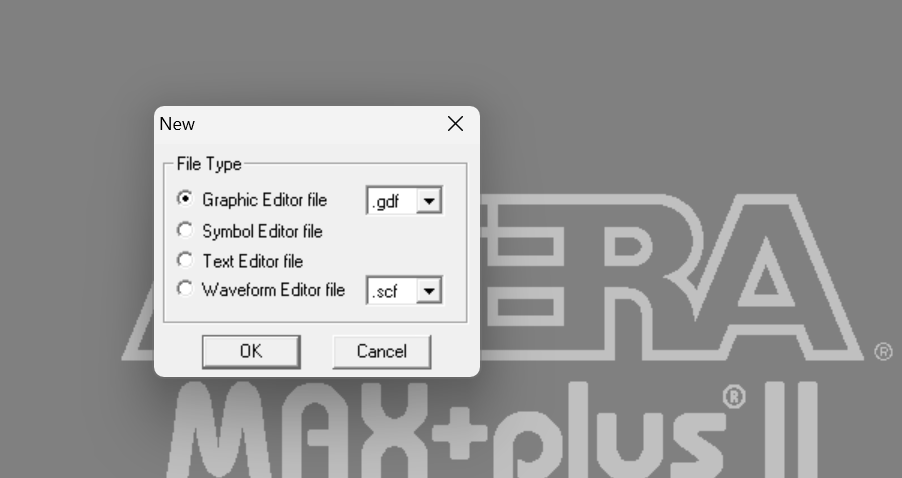

打开Max+plus Ⅱ系统后,按屏幕上方的按钮![]() ,或者选择菜单“File”-->“NEW…”,出现如图1-1所示的对话框,在框中选中“Text Editor file”

,或者选择菜单“File”-->“NEW…”,出现如图1-1所示的对话框,在框中选中“Text Editor file”

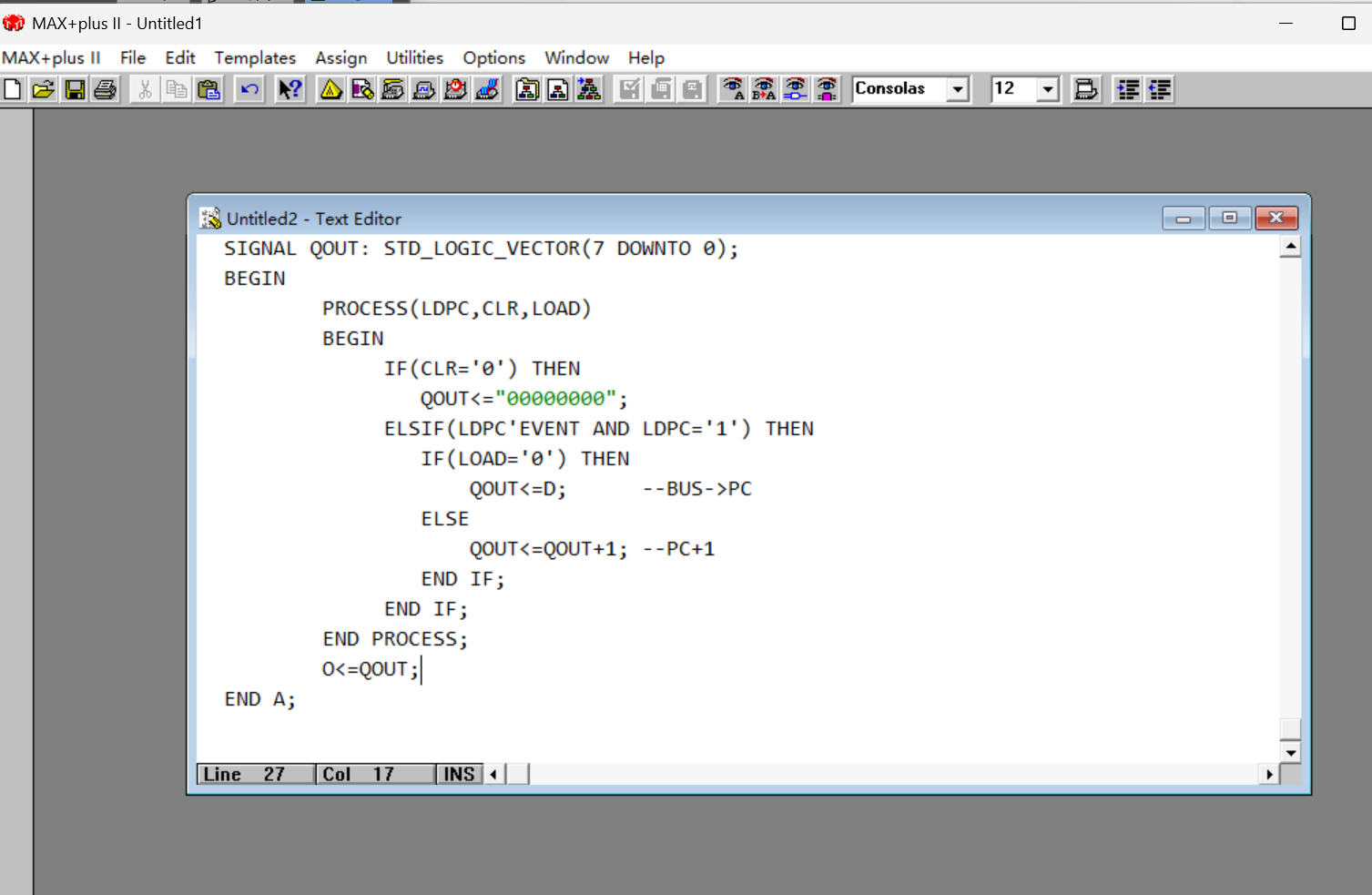

将下面粉色部分的程序代码复制到文本输入框内

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY PC IS

PORT(

LOAD,LDPC,CLR: IN STD_LOGIC;

D: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

O: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END PC;

ARCHITECTURE A OF PC IS

SIGNAL QOUT: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(LDPC,CLR,LOAD)

BEGIN

IF(CLR='0') THEN

QOUT<="00000000";

ELSIF(LDPC'EVENT AND LDPC='1') THEN

IF(LOAD='0') THEN

QOUT<=D; --BUS->PC

ELSE

QOUT<=QOUT+1; --PC+1

END IF;

END IF;

END PROCESS;

O<=QOUT;

END A;

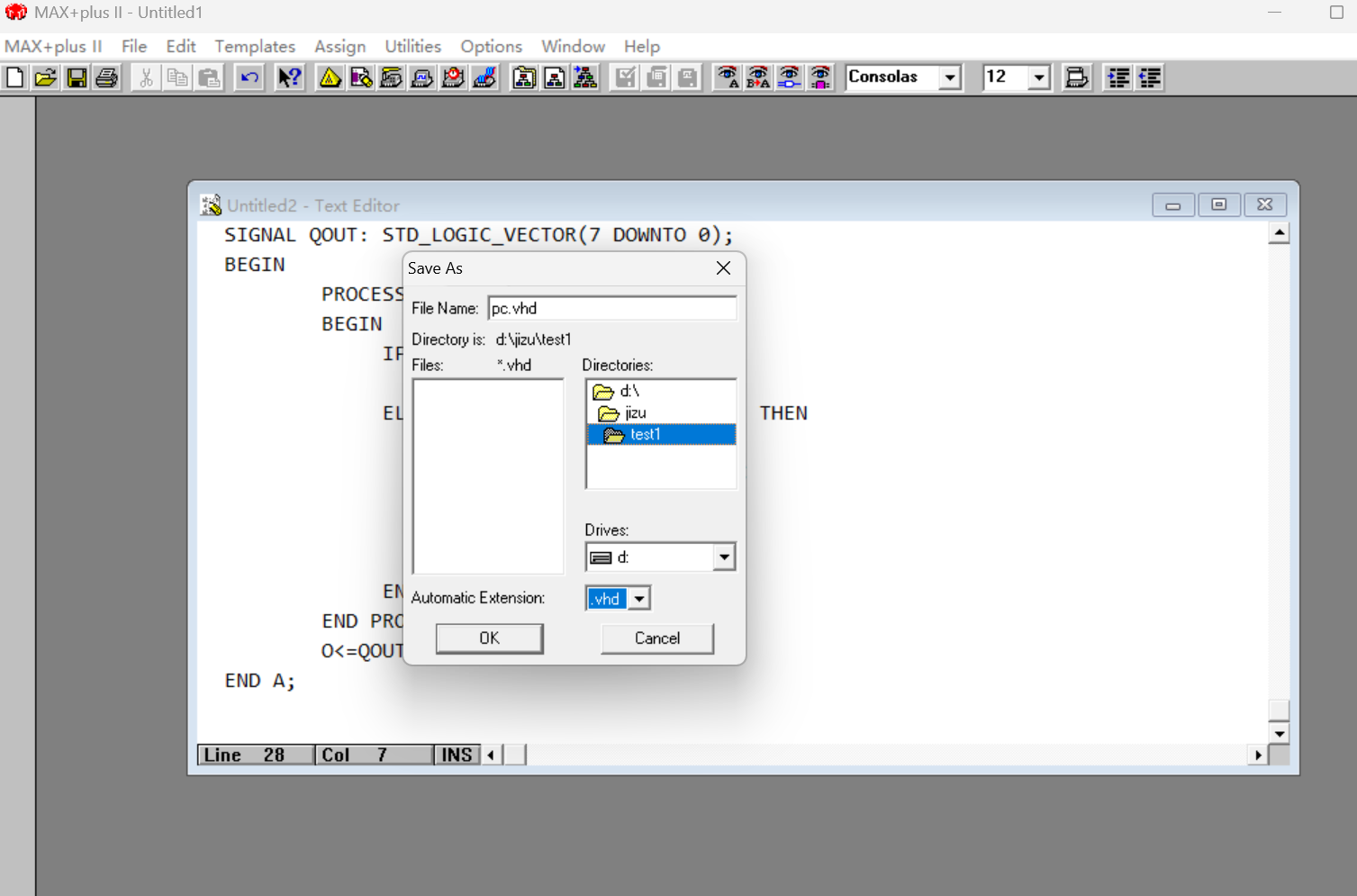

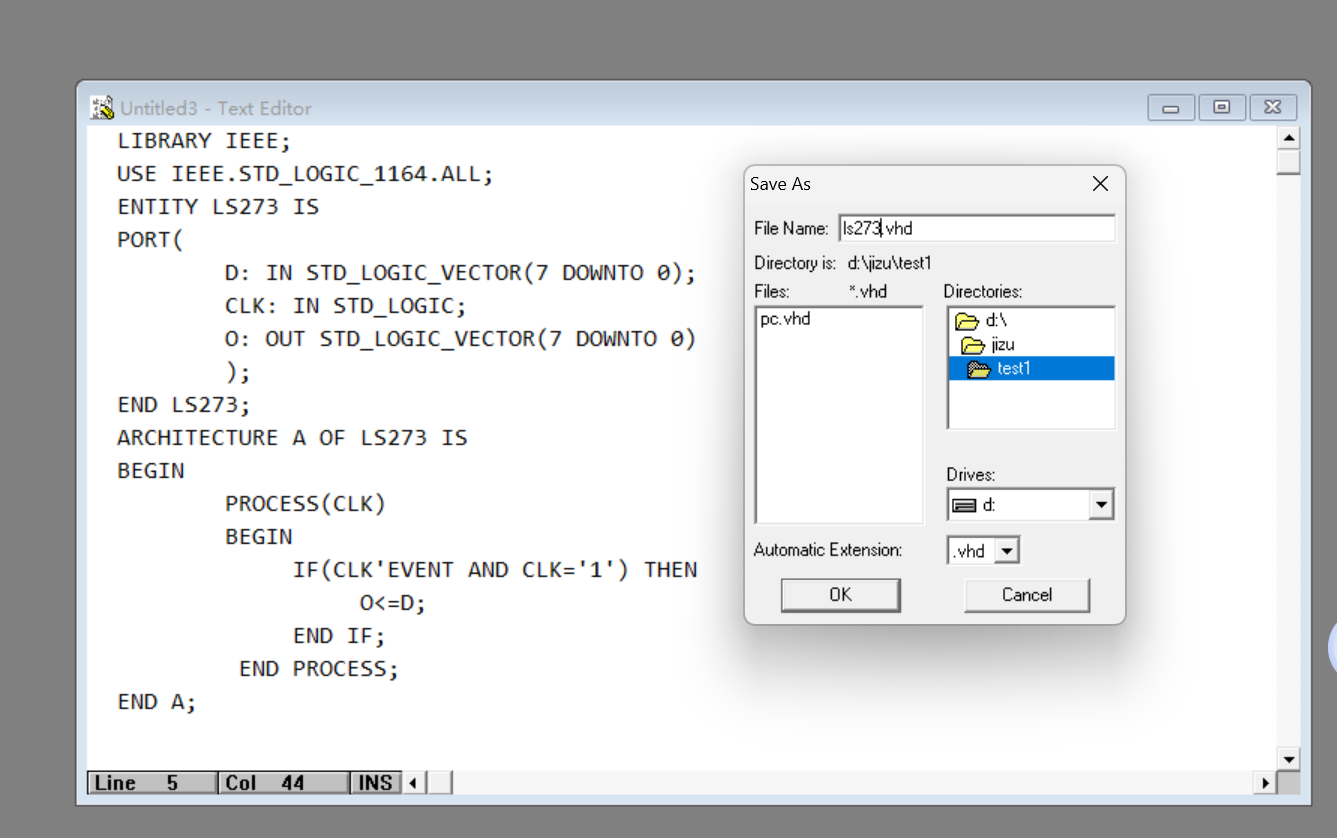

输入完毕后,选择菜单“File-->Save”,点击选中保存的路径。输入正确的文件名称pc.vhd,并把Automatic Extension修改为vhd

注意一定要双击选中,且路径不带有中文,文件后缀名正确,不然编译的时候会报错。

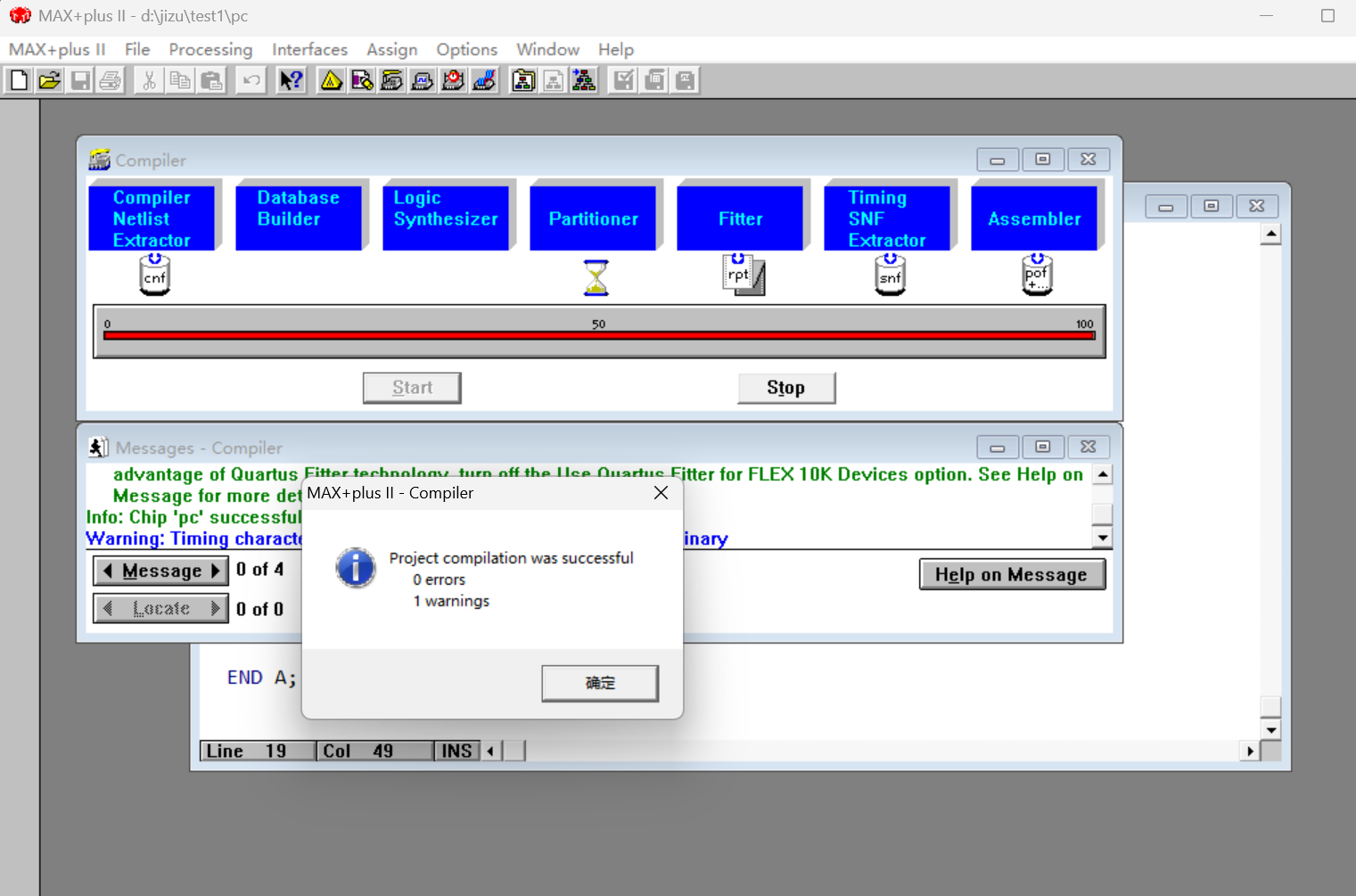

选择菜单“File”-->“Create Default Symbol”,弹出编译窗口,点击start,如果是0errors,则继续。

接下来创建源程序ls273.vhd,步骤与创建pc.vhd的步骤一致,可以参考上面的步骤,程序代码为下面的粉色部分,要注意的是,文件名要修改正确,路径与pc.vhd保持一致。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LS273 IS

PORT(

D: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK: IN STD_LOGIC;

O: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END LS273;

ARCHITECTURE A OF LS273 IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

O<=D;

END IF;

END PROCESS;

END A;

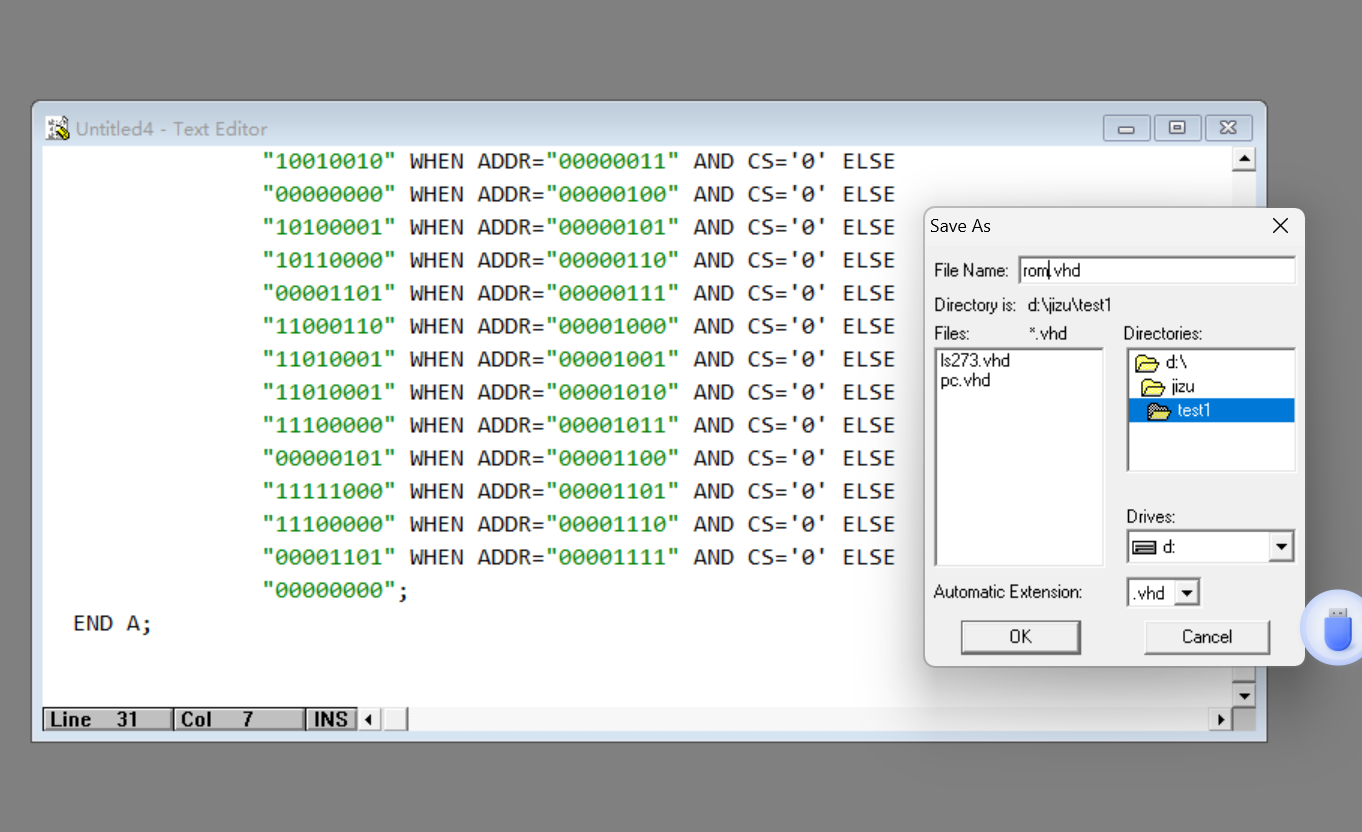

接下来创建源程序rom.vhd,步骤与创建pc.vhd的步骤一致,可以参考上面的步骤,程序代码为下面的粉色部分,要注意的是,文件名要修改正确,路径与pc.vhd保持一致。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ROM IS

PORT(

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

ADDR:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CS:IN STD_LOGIC

);

END ROM;

ARCHITECTURE A OF ROM IS

BEGIN

DOUT<="10000000" WHEN ADDR="00000000" AND CS='0' ELSE

"10010001" WHEN ADDR="00000001" AND CS='0' ELSE

"00000001" WHEN ADDR="00000010" AND CS='0' ELSE

"10010010" WHEN ADDR="00000011" AND CS='0' ELSE

"00000000" WHEN ADDR="00000100" AND CS='0' ELSE

"10100001" WHEN ADDR="00000101" AND CS='0' ELSE

"10110000" WHEN ADDR="00000110" AND CS='0' ELSE

"00001101" WHEN ADDR="00000111" AND CS='0' ELSE

"11000110" WHEN ADDR="00001000" AND CS='0' ELSE

"11010001" WHEN ADDR="00001001" AND CS='0' ELSE

"11010001" WHEN ADDR="00001010" AND CS='0' ELSE

"11100000" WHEN ADDR="00001011" AND CS='0' ELSE

"00000101" WHEN ADDR="00001100" AND CS='0' ELSE

"11111000" WHEN ADDR="00001101" AND CS='0' ELSE

"11100000" WHEN ADDR="00001110" AND CS='0' ELSE

"00001101" WHEN ADDR="00001111" AND CS='0' ELSE

"00000000";

END A;

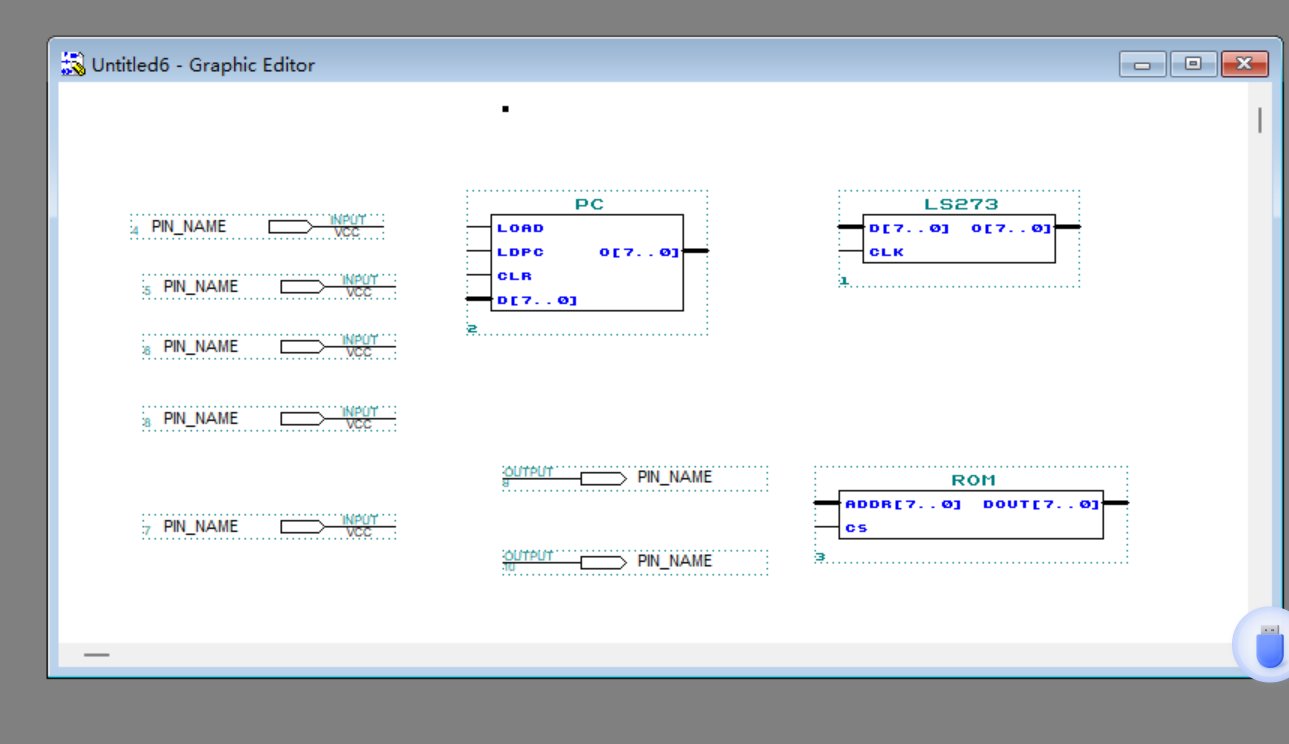

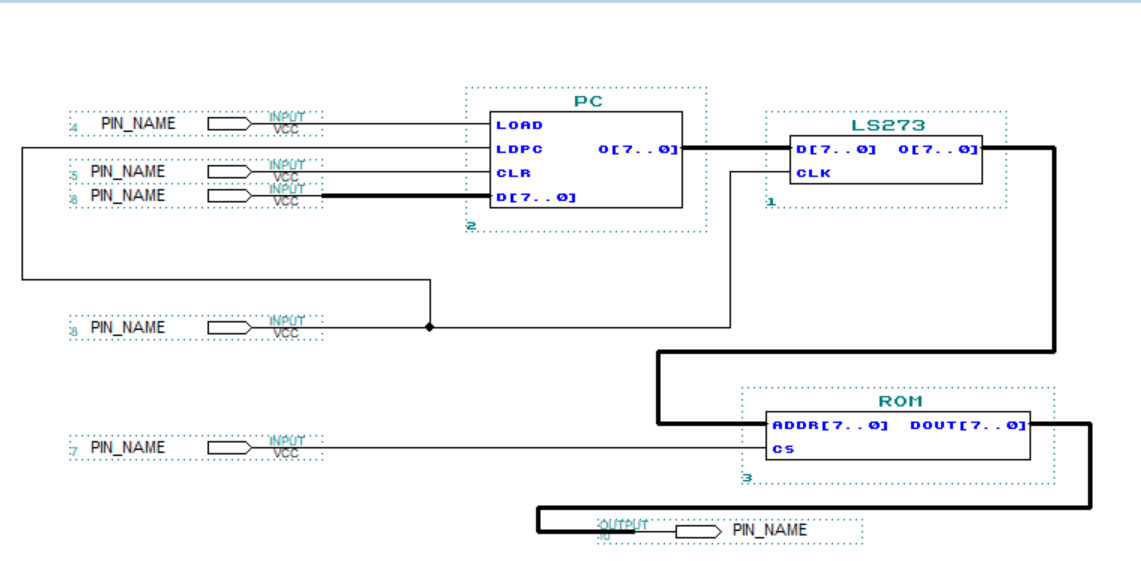

上面三个源程序文件创建完后,我们创建图形设计文件。

选择菜单“File”-->“New”,在如图1-1所示的对话框中选择“Graphic Editor File”

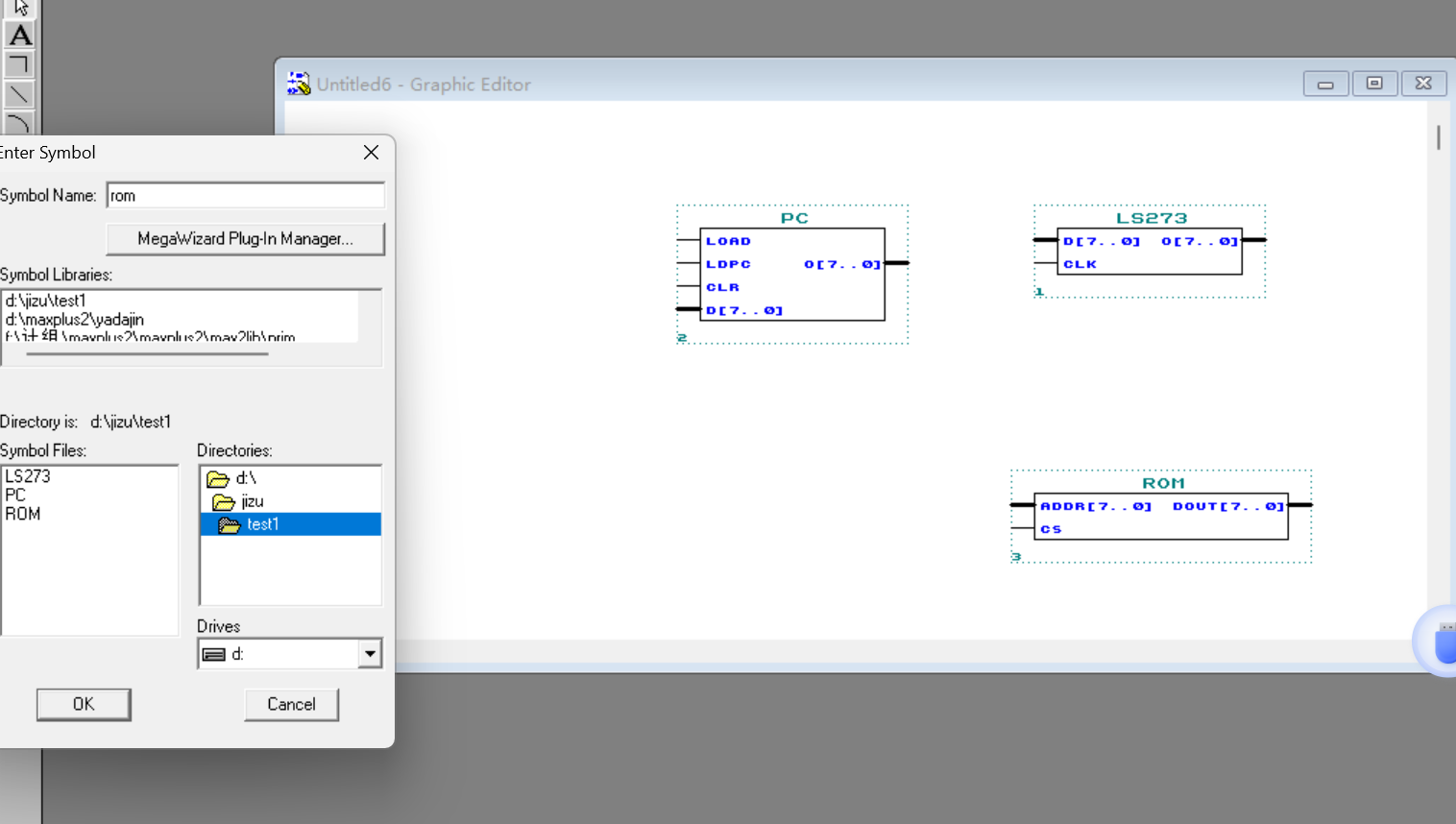

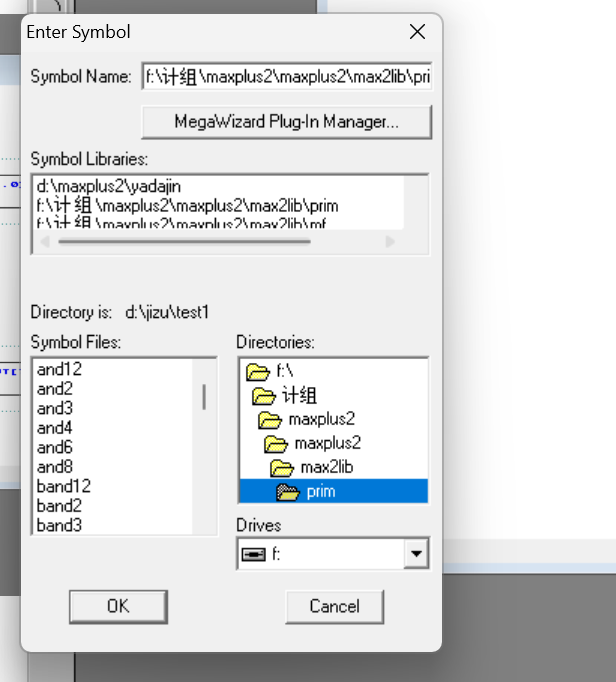

双击空白处,弹出“Enter Symbol”对话框,双击Symbol Files的原件添加进去(三个:PC、LS237、ROM)

继续双击空白处,将Symbol Libraries修改到f:\计组\maxplus2\max2lib\prim,即你的prim目录,目录跟我不一样的按自己的来。

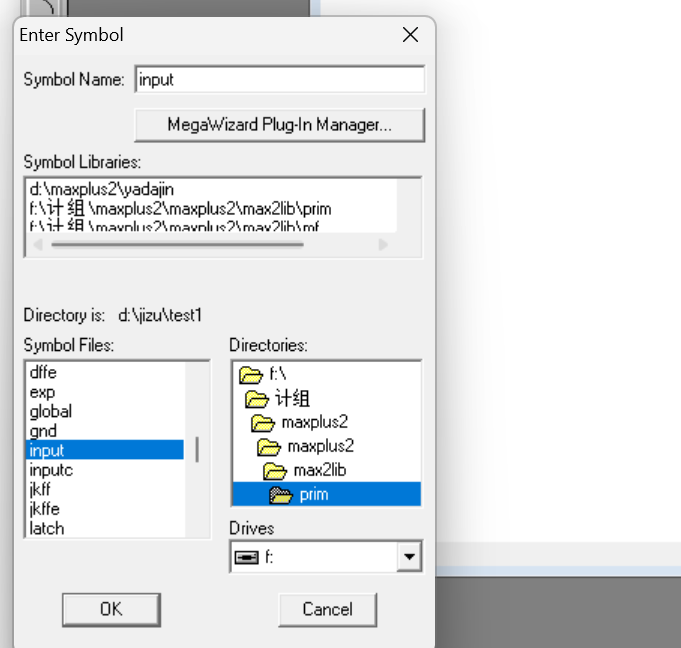

在Symbol Files下划找到input,双击添加

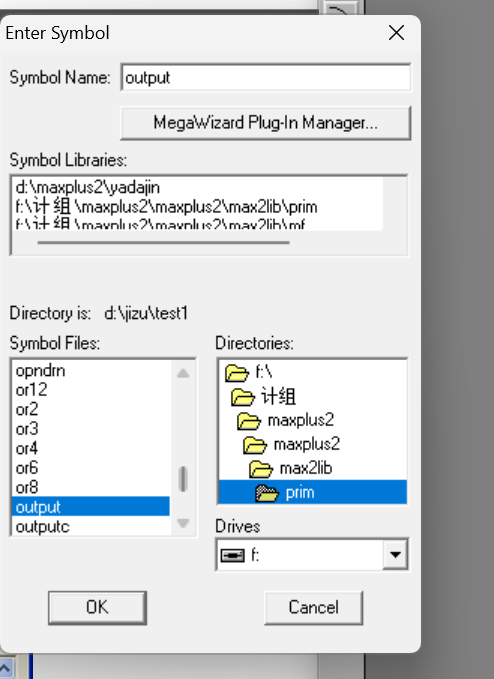

在Symbol Files下划找到output,双击添加

点击input元件,CTRL+c复制,CTRL+v粘贴,一共需要5个input元件,1个output元件。(PS:下面的图我不小心多复制了一个output,如果你也不小心的话,CTRL+z撤销就好了)

放好输入/输出元件符号,再将鼠标箭头移到符号的输入/输出引脚上,鼠标箭头形状会变成“+”字形,然后可以按着鼠标左键并拖动鼠标,绘出一条线。

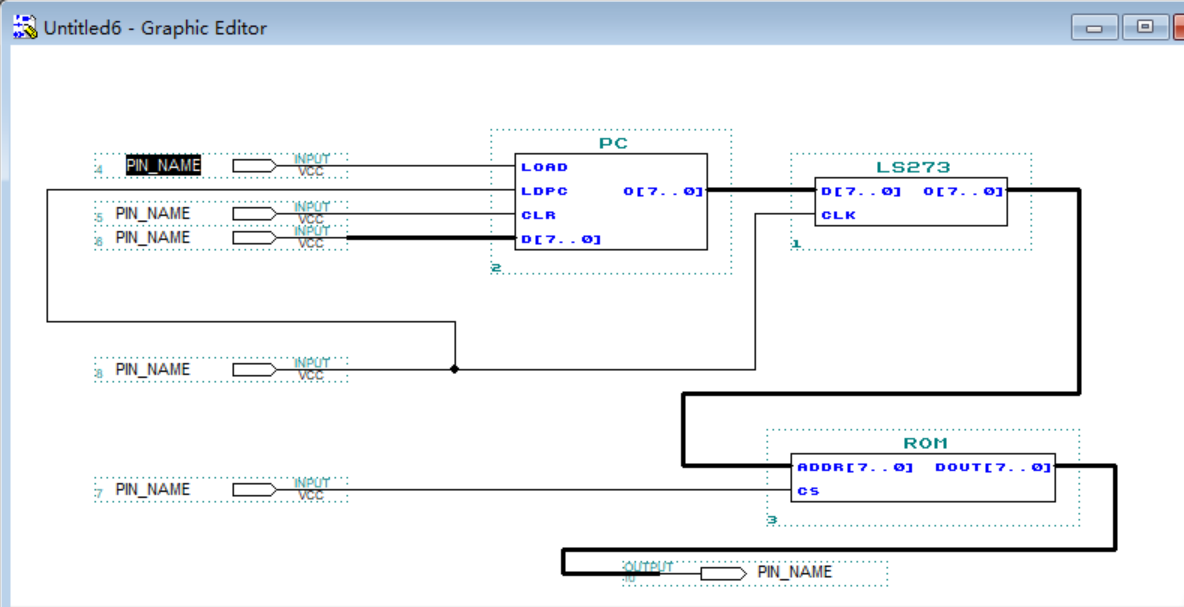

相信聪明的你一下子就学会操作了~接下来只要根据下面的图进行连线就好了

注意:线的粗细一定与图一致,若线画错可以点击线,线变红后点击delete删除

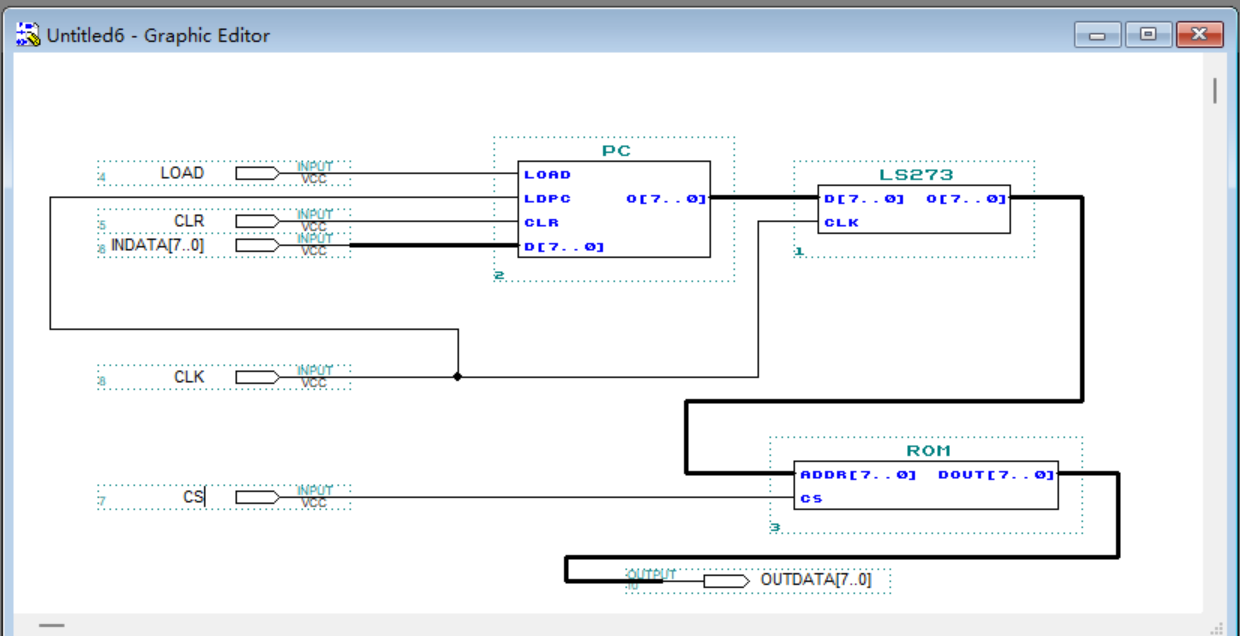

接下来设置输入/输出引脚名,双击PIN_NAME,修改为对应的原件名。

各个输入/输出引脚名与下图保持一致。

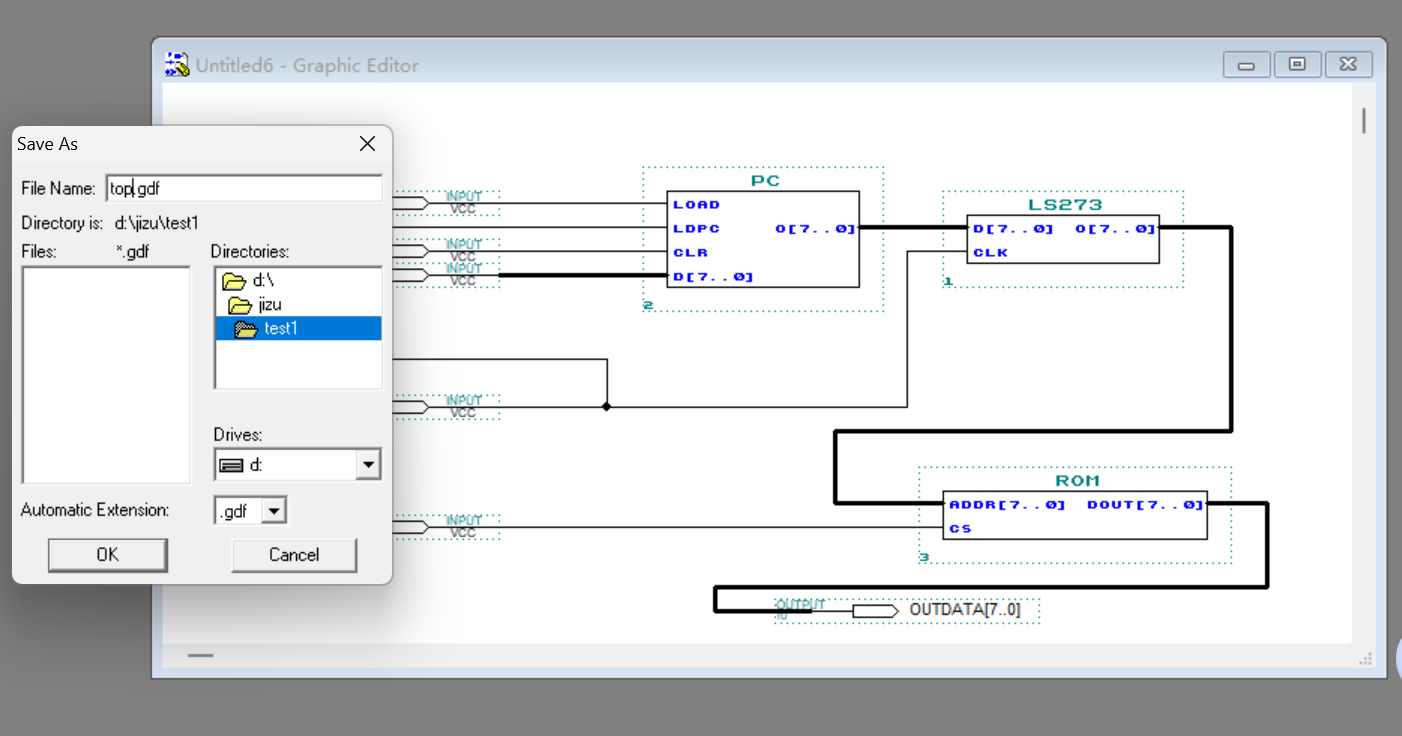

最后选择“File”-->“Save”菜单,将此顶层原理图文件取名为top.gdf,Automatic Extension修改为.gdf

二、编译处理

在编译top.gdf之前,需要设置此文件为顶层文件,或称工程文件(项目文件):Project。选择菜单“File”-->“Project”-->“Set Project to Crurrent File”,当前的工程即被设为top。

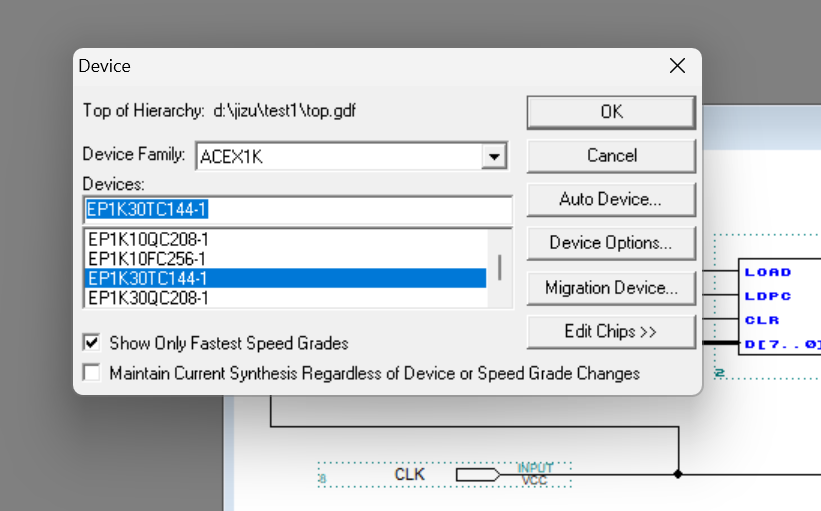

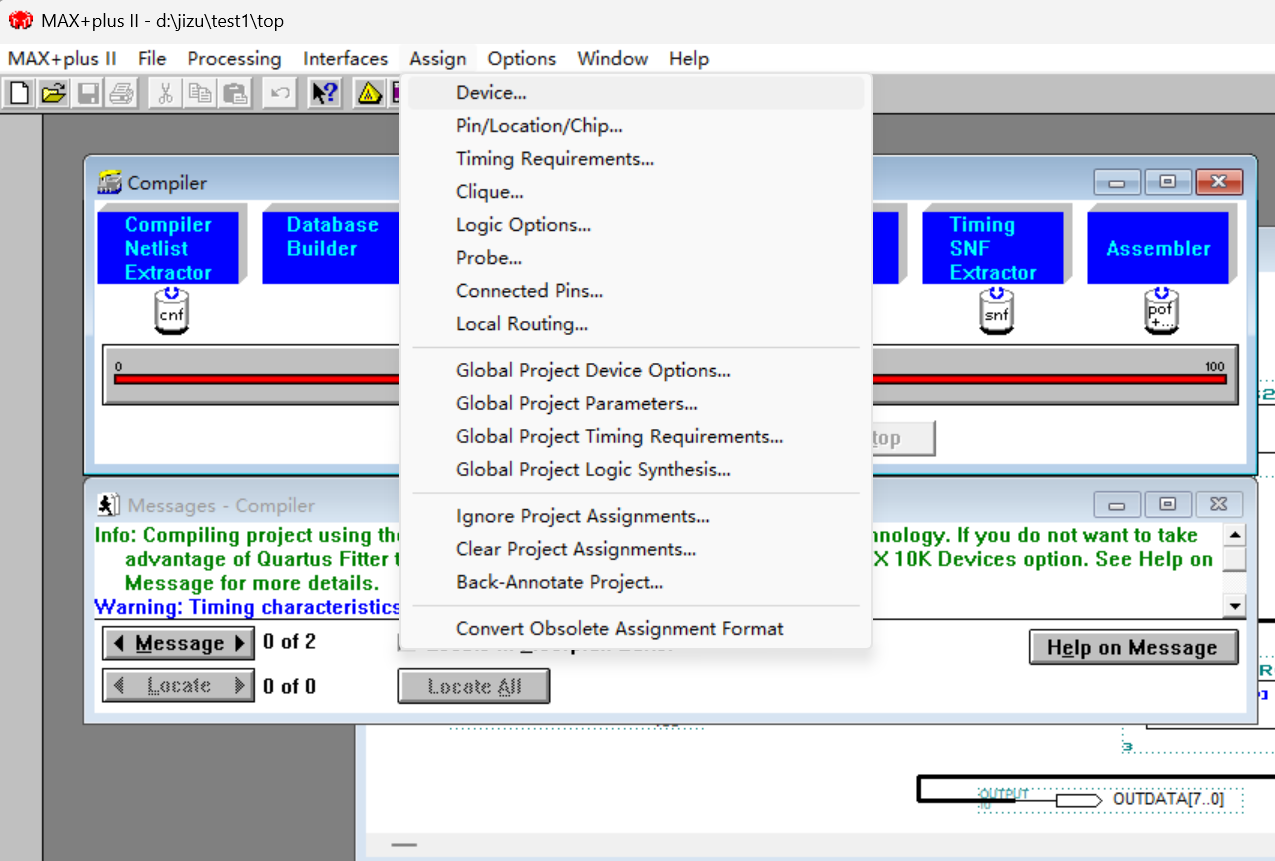

然后选择用于编程的目标芯片。选择菜单“Assign”-->“Device

在对话框中的“Device Family”下拉栏中选择ACEX1K,然后在“Devices”列表框中选择芯片型号“EP1K30TC144-1”

单击工具栏中的编译器快捷按钮,(选择MAX+plus Ⅱ-->Compiler选项,即可打开编译器窗口)对顶层文件进行编译,也是弹出后点击start

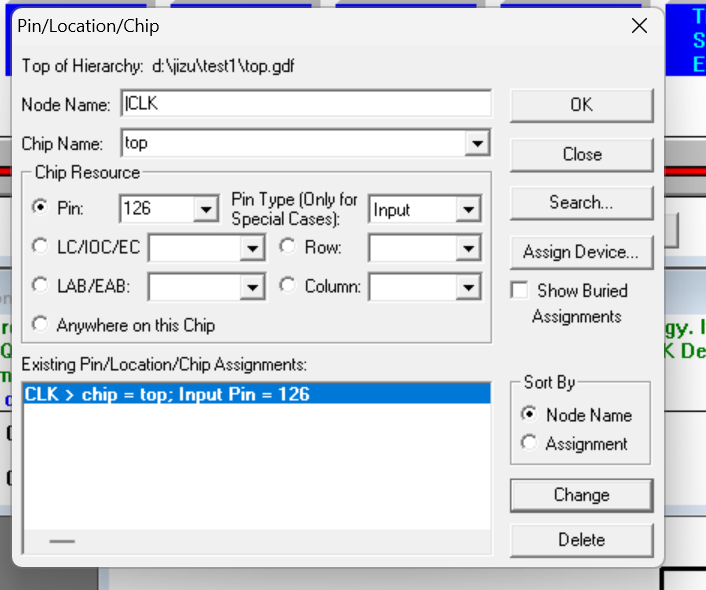

编译成功后,不要关掉编译窗口,我们来确定引脚。选择菜单“Assign”-->“Pin/Location/Chip…”

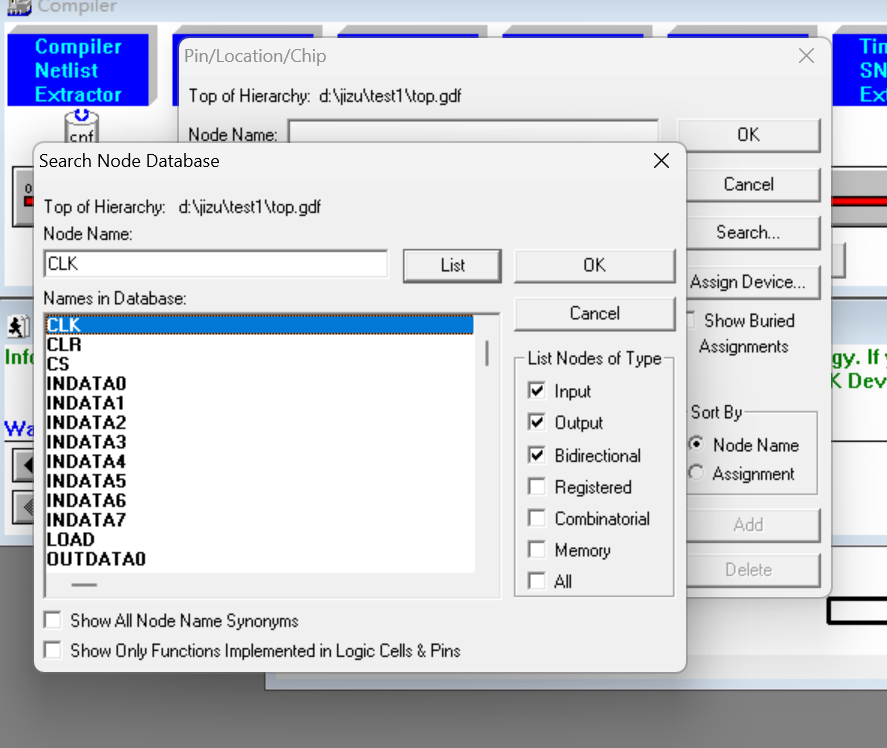

在弹出的窗口中,可以点击Search按钮,在弹出的窗口中Node Name输入项的右边有一个List,点击后出现顶层文件包含的所有输入输出引脚名,我们点击选中CLK

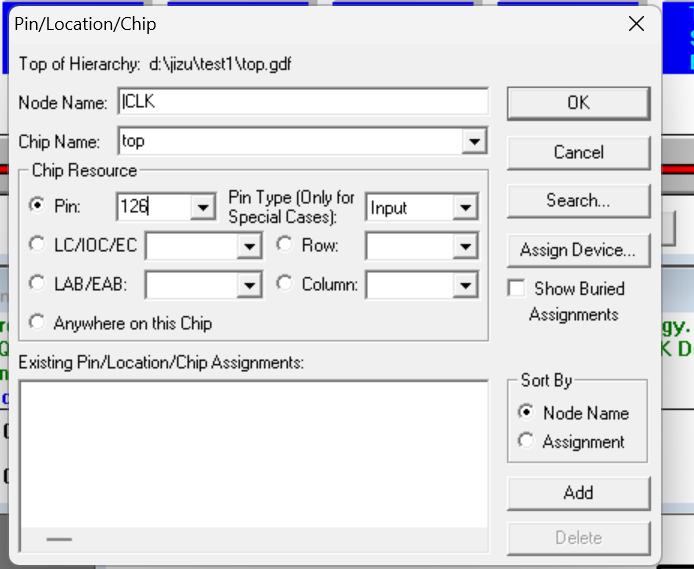

将Pin填入128,点击Add。

当你看到白色框框出现刚刚你输入的元件与引脚,则设置成功。

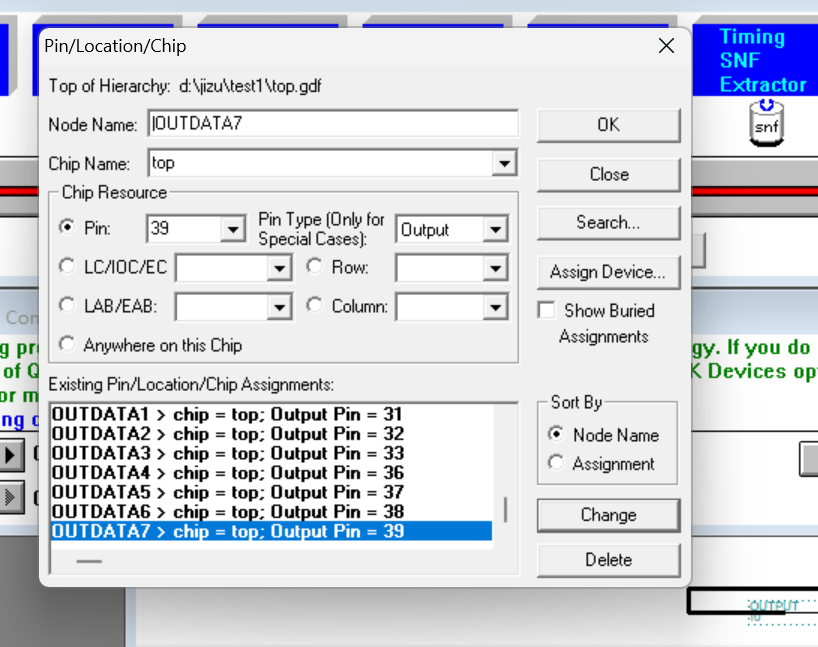

接下来的如法炮制,将下面的表的各个引脚一一添加

|

引脚名 |

芯片引脚号 |

引脚名 |

芯片引脚号 |

引脚名 |

芯片引脚号 |

|

CLK |

126 |

INDATA3 |

12 |

OUTDATA2 |

32 |

|

CLR |

138 |

INDATA4 |

13 |

OUTDATA3 |

33 |

|

CS |

20 |

INDATA5 |

17 |

OUTDATA4 |

36 |

|

LOAD |

21 |

INDATA6 |

18 |

OUTDATA5 |

37 |

|

INDATA0 |

8 |

INDATA7 |

19 |

OUTDATA6 |

38 |

|

INDATA1 |

9 |

OUTDATA0 |

30 |

OUTDATA7 |

39 |

|

INDATA2 |

10 |

OUTDATA1 |

31 |

全部添加完毕后,点击ok

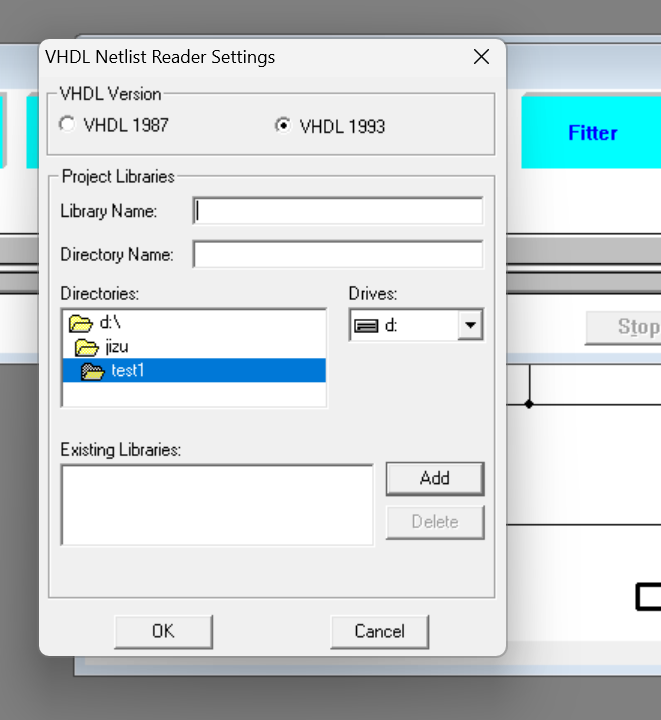

全部设定完毕后,下面开始编译。选择“MAX+plusII”-->“Compiler”菜单,start进行编译,不要关闭编译窗口,在编译器窗口上方的“Interfaces”-->“VHDL Netlist Reader Settings”,在弹出的窗口中选“VHDL’93”

三、仿真波形

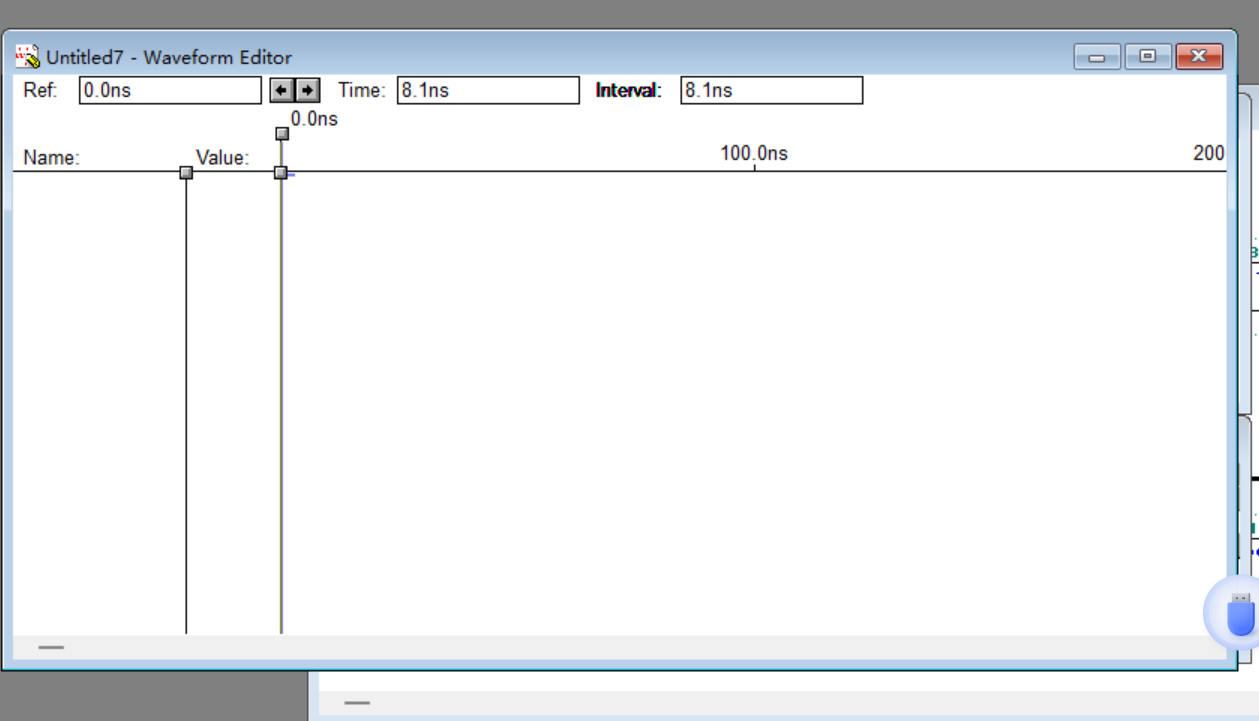

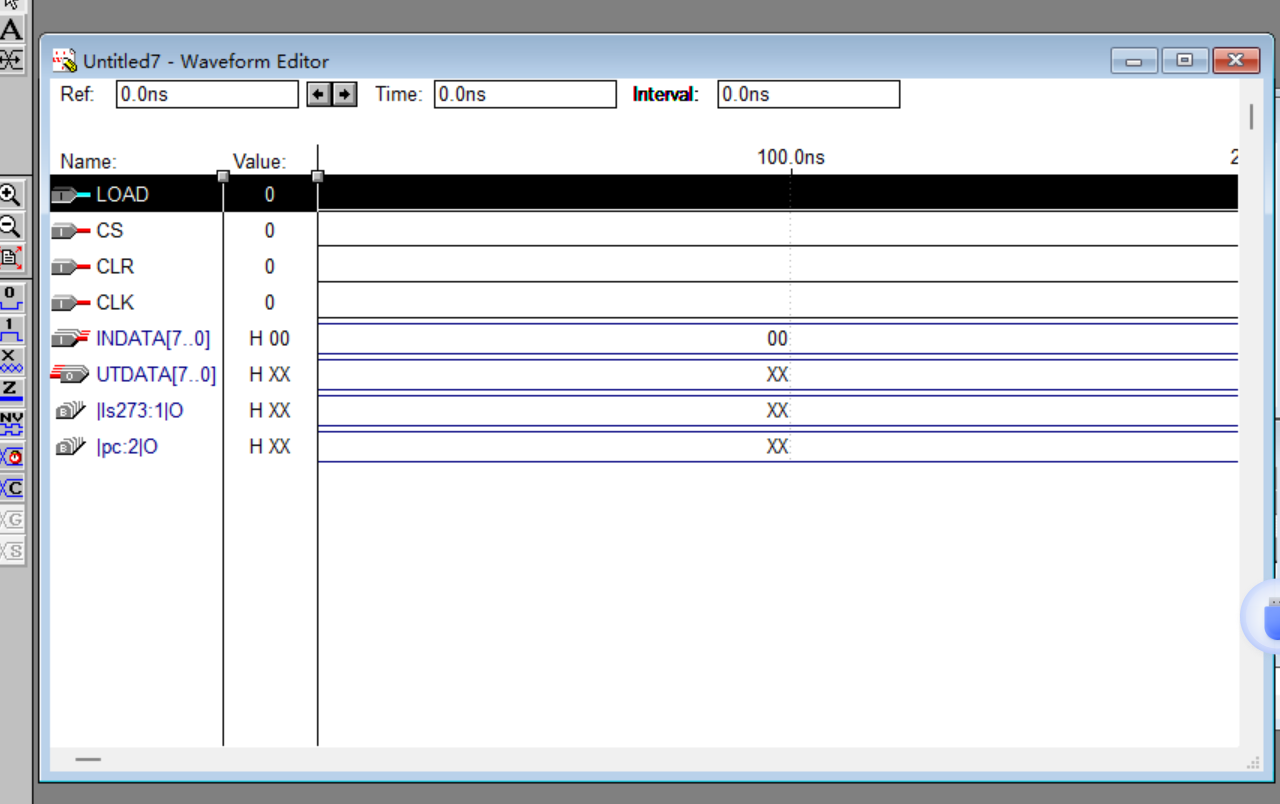

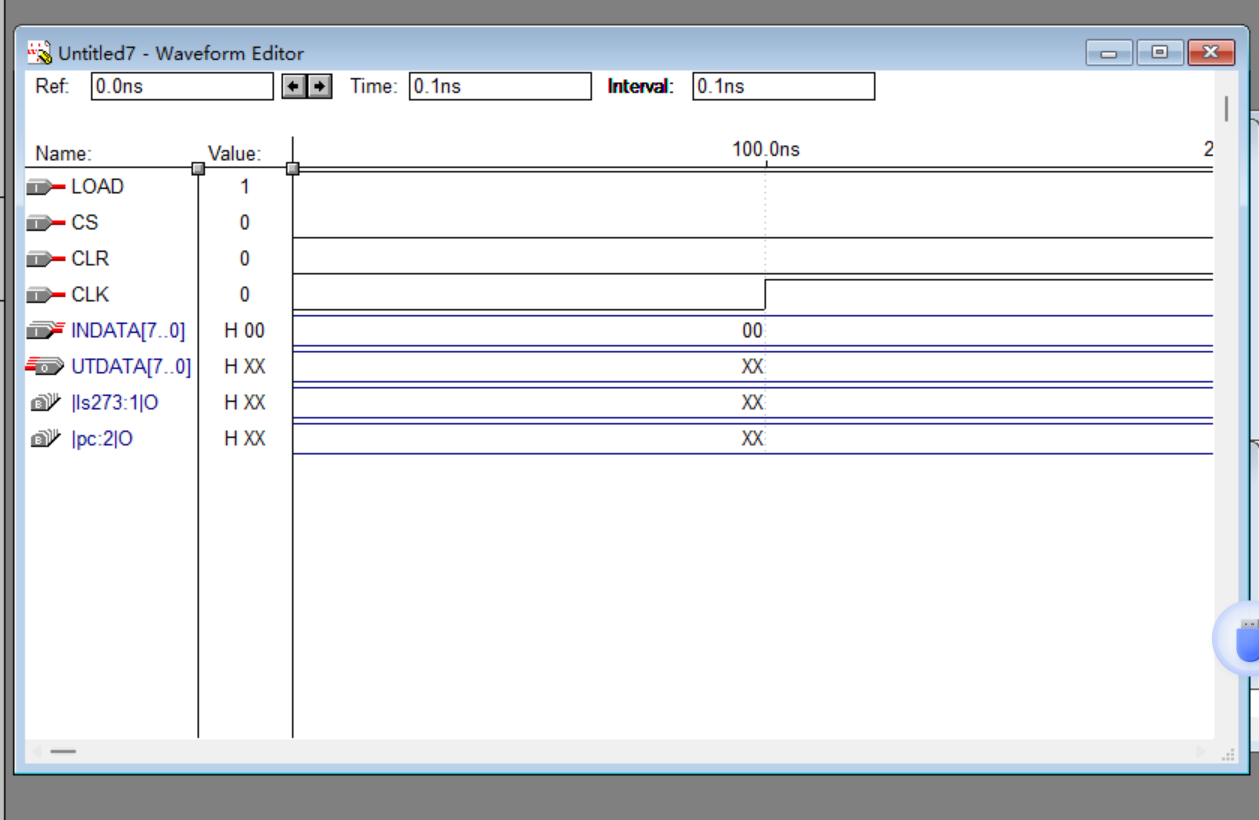

选择菜单“File”-->“New”,在出现的“New”对话框中选择“Waveform Editor file”,确定后出现下面图片。

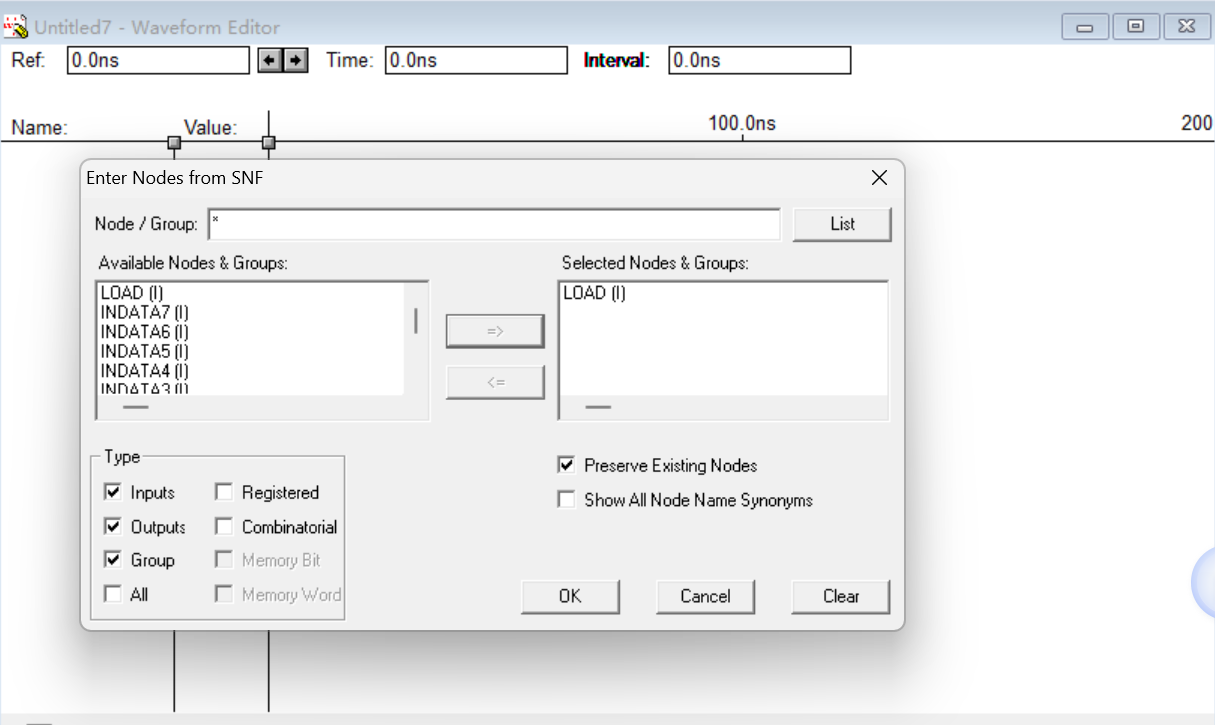

选择菜单“Node”-->“Enter Nodes from SNF…”,出现如图所示的选择信号节点对话框,点击List,左边列表框选中LOAD[I],然后点击“=>”按钮,添加到右边的框框

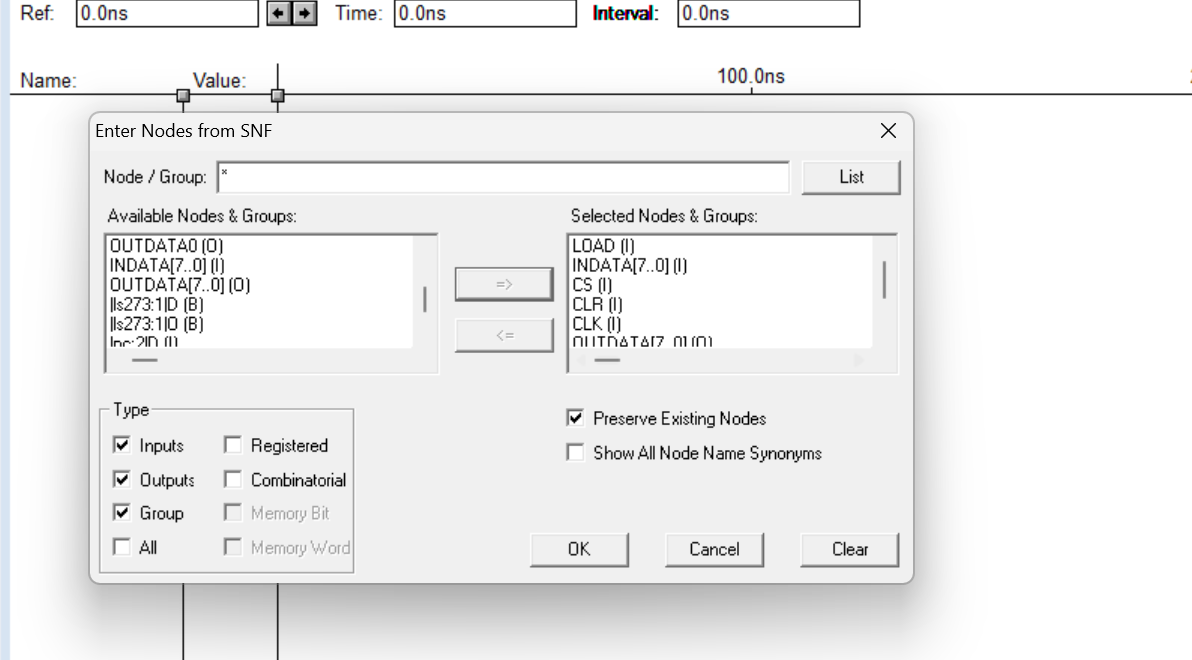

接下来将左边列表框中的节点CS[I]、CLR[I]、CLK[I]、INDATA[7..0](I)、OUTDATA[7..0](O)、|pc:2|O(B)和|ls273:1|O(B)也分别选中到右边的列表框

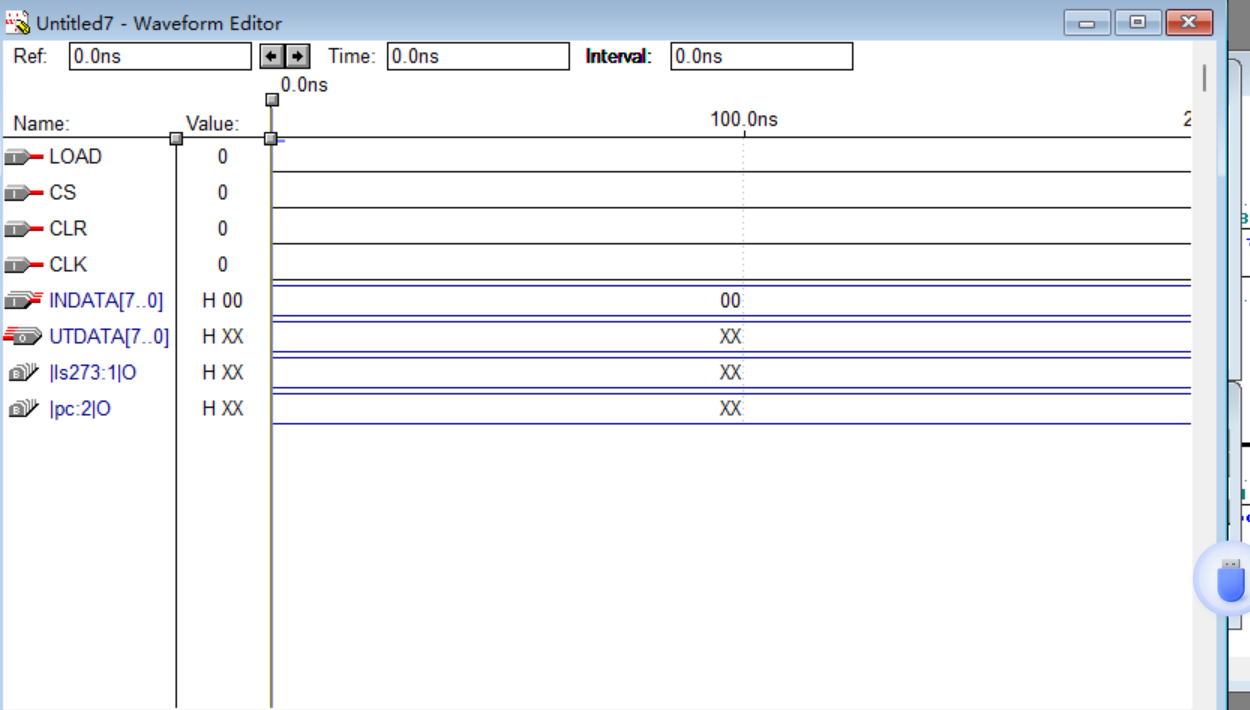

添加完毕ok后,出现下面一致的东西

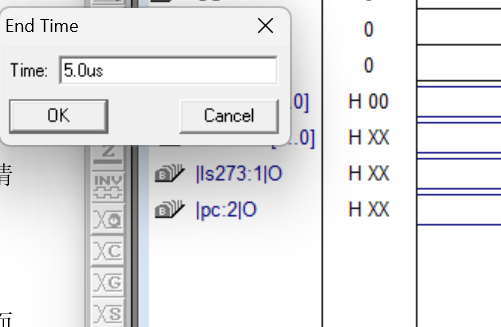

点击“File”-->“End Time”,将时间设置为5us,方便全局查看。

接下来设置各个节点的信号。

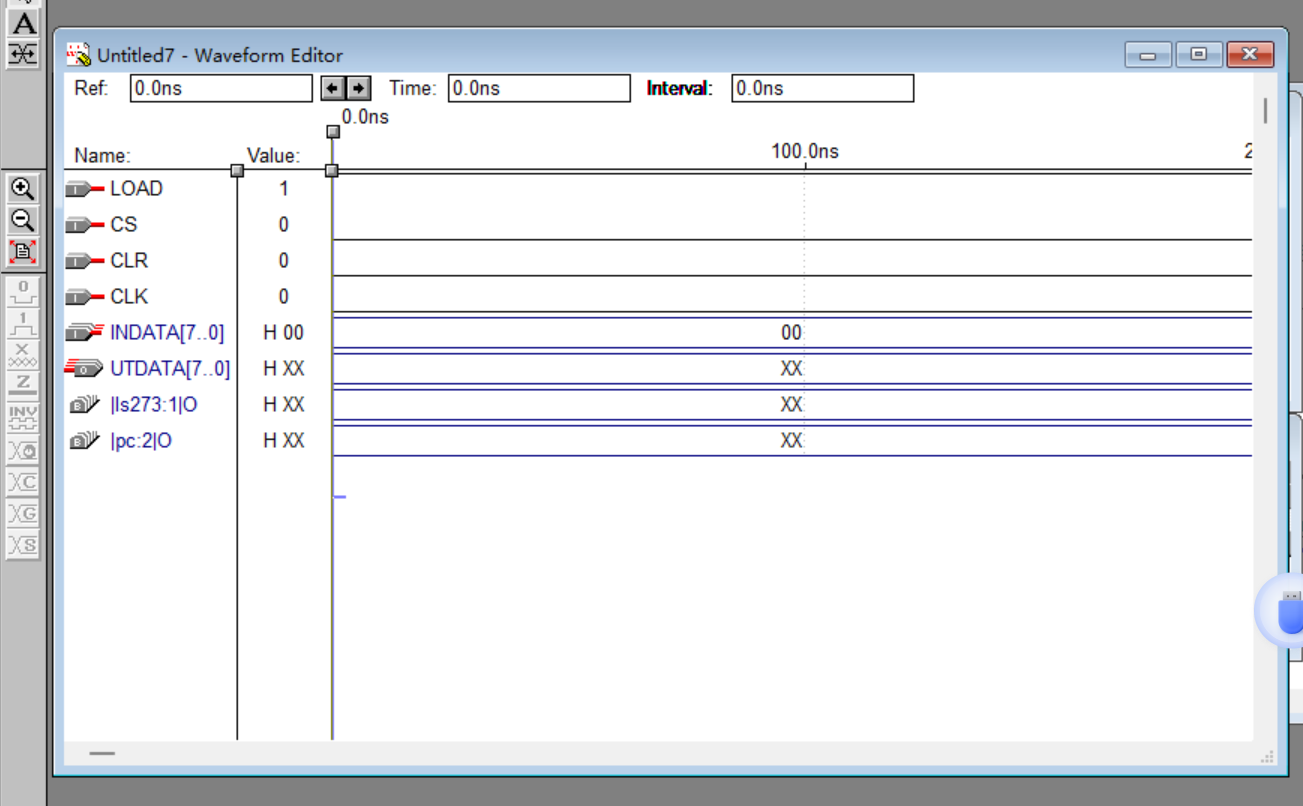

首先设置LOAD信号,用鼠标点LOAD信号的Value区域,可以将LOAD选中,这时LOAD的波形区域全部变成黑色。按集成环境窗左边上的置“1”按钮![]() ,LOAD的值将被置为“1”;

,LOAD的值将被置为“1”;

LOAD的value设置为了1,如图

然后设置CS信号,用鼠标点CS信号的Value区域,可以将CS选中,这时CS的波形区域全部变成黑色。按集成环境窗左边上的清“0”按钮![]() ,CS的值将被清为“0”;

,CS的值将被清为“0”;

再设置CLR信号,采用与设置LOAD信号相同的方法将CLR的值置为“1”,然后用鼠标左键点击CLR的0~100ns区域,按住鼠标往后挪到200ns区域全部变成黑色。按集成环境窗左边上的清“0”按钮![]() ,CLR在0~200ns区域的值将被清为“0”。

,CLR在0~200ns区域的值将被清为“0”。

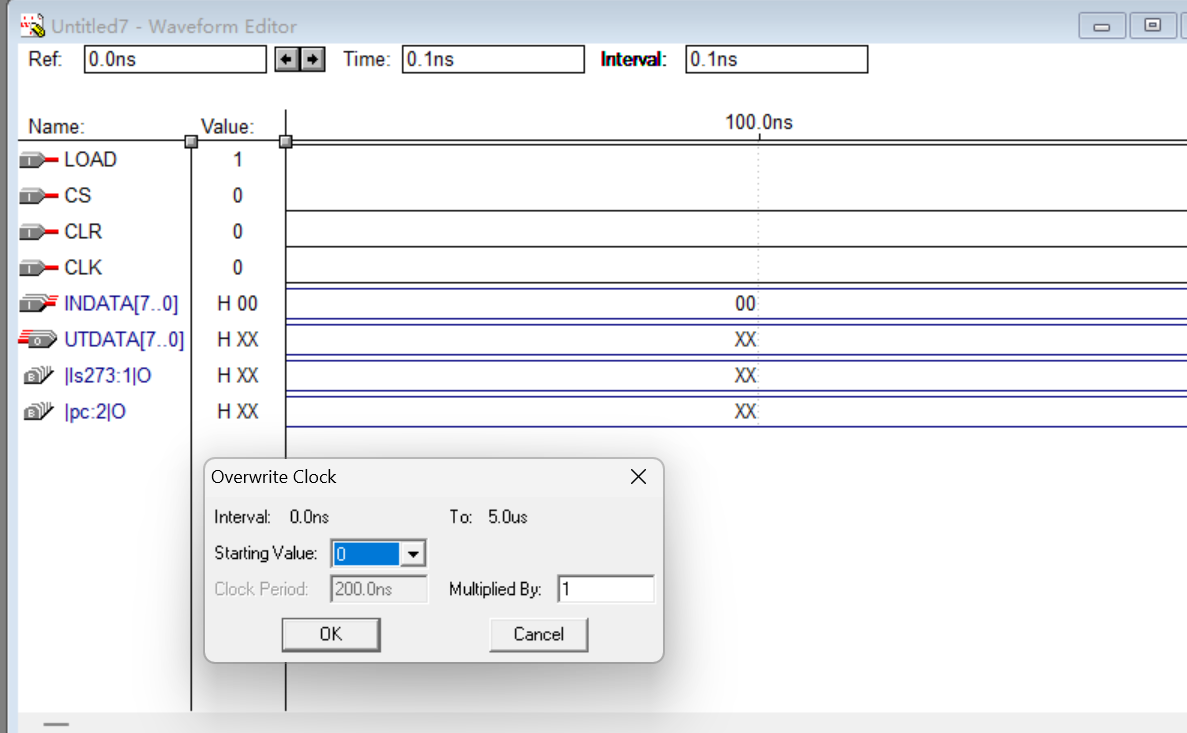

接着再设置CLK时钟信号,用鼠标点CLK信号的Value区域,可以将CLK选中,这时CLK的波形区域全部变成黑色。按集成环境窗左边的时钟按钮![]() ,对话框默认值0。

,对话框默认值0。

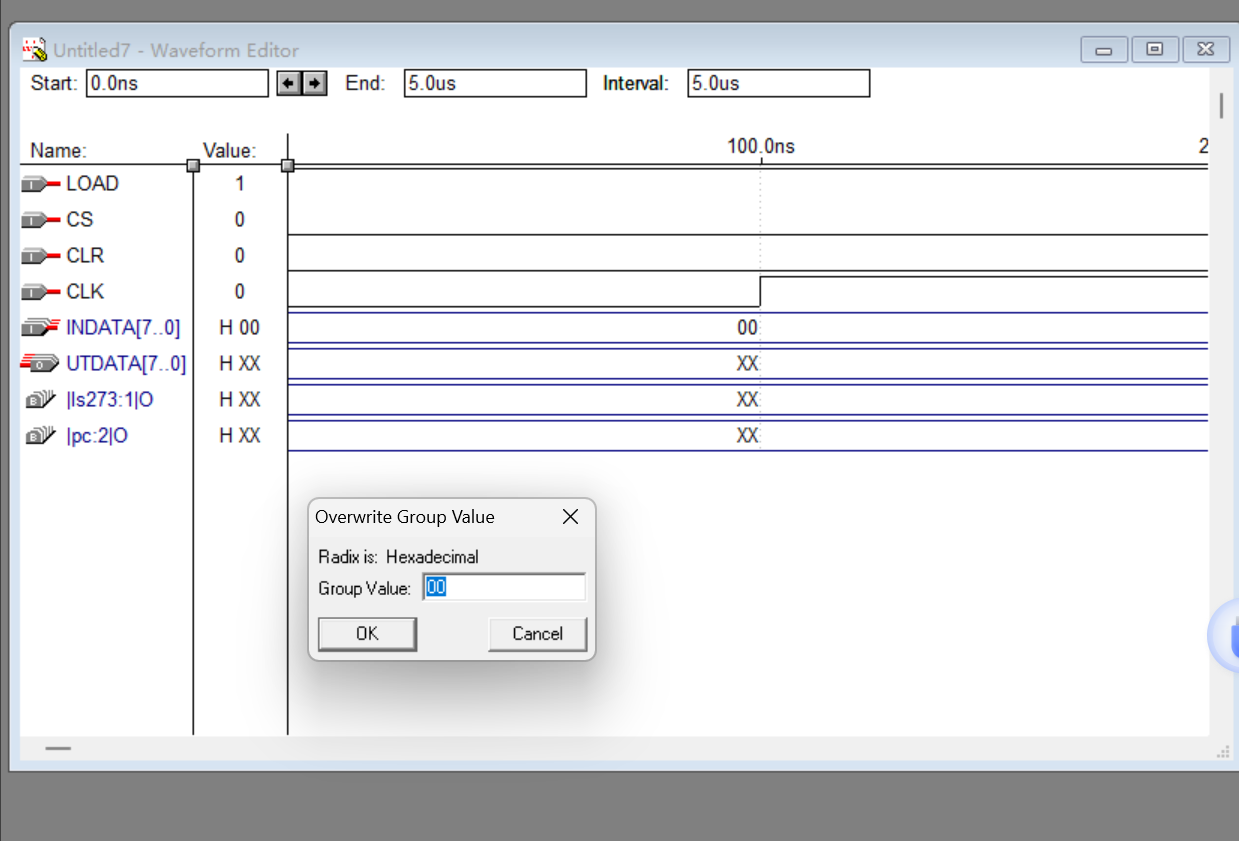

最后设置INDATA[7..0]信号,用鼠标点INDATA[7..0]信号的Value区域,可以将INDATA[7..0]选中,这时INDATA[7..0]的波形区域全部变成黑色。按集成环境窗左边的总线数据设置按钮![]() ,弹出对话框,默认值0就可以。

,弹出对话框,默认值0就可以。

全部设置完如下图。

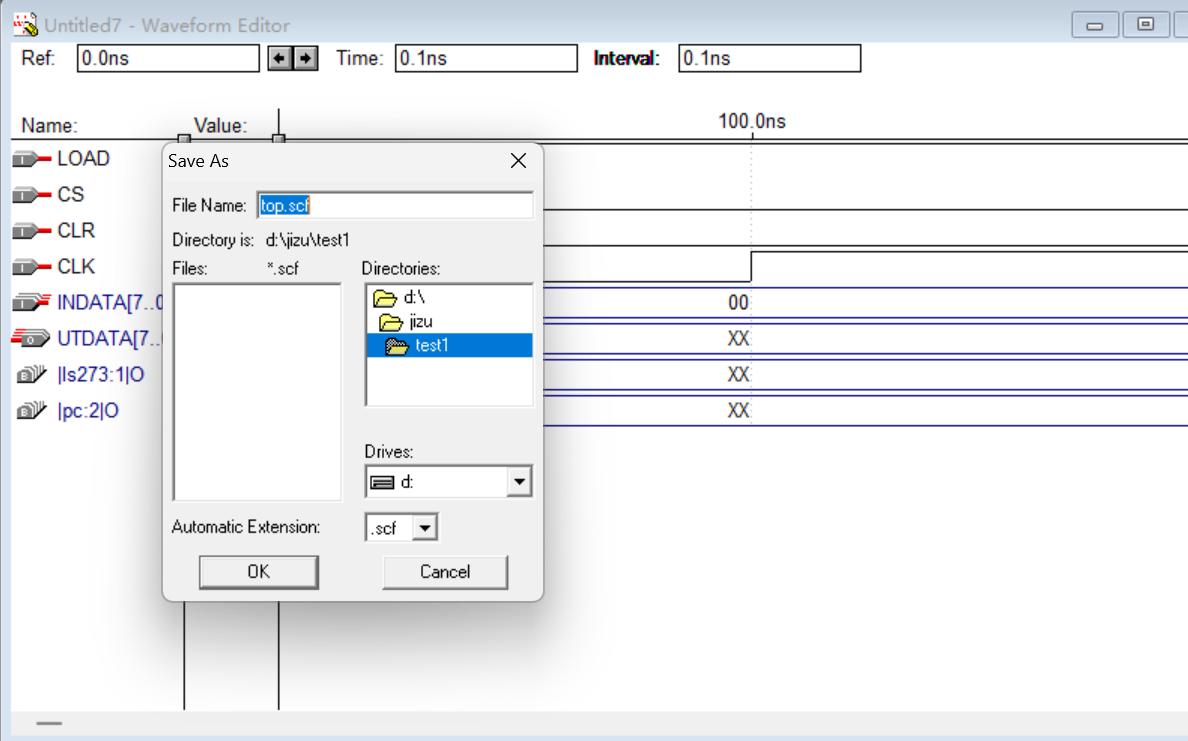

接下去是运行仿真器(Simulator)。点击工具栏上的波形仿真快捷按钮![]() ,出现保存提醒,将文件命名top.scf,保存在统一路径。

,出现保存提醒,将文件命名top.scf,保存在统一路径。

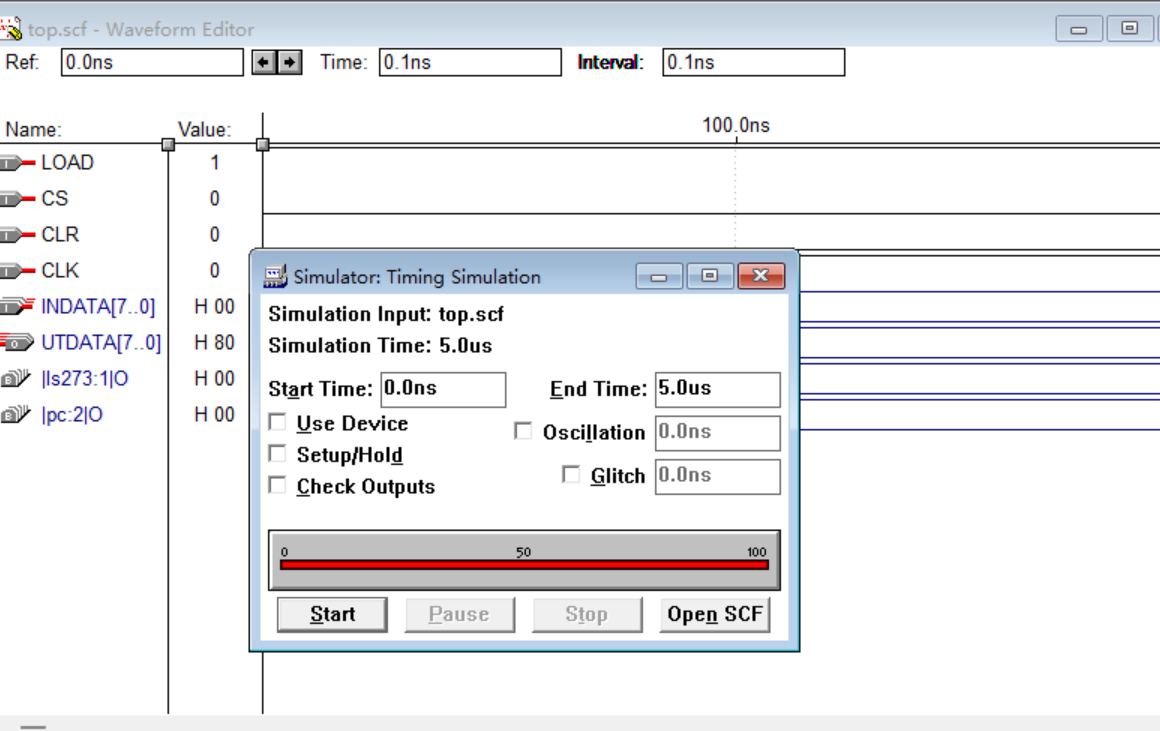

点击start进行时序仿真

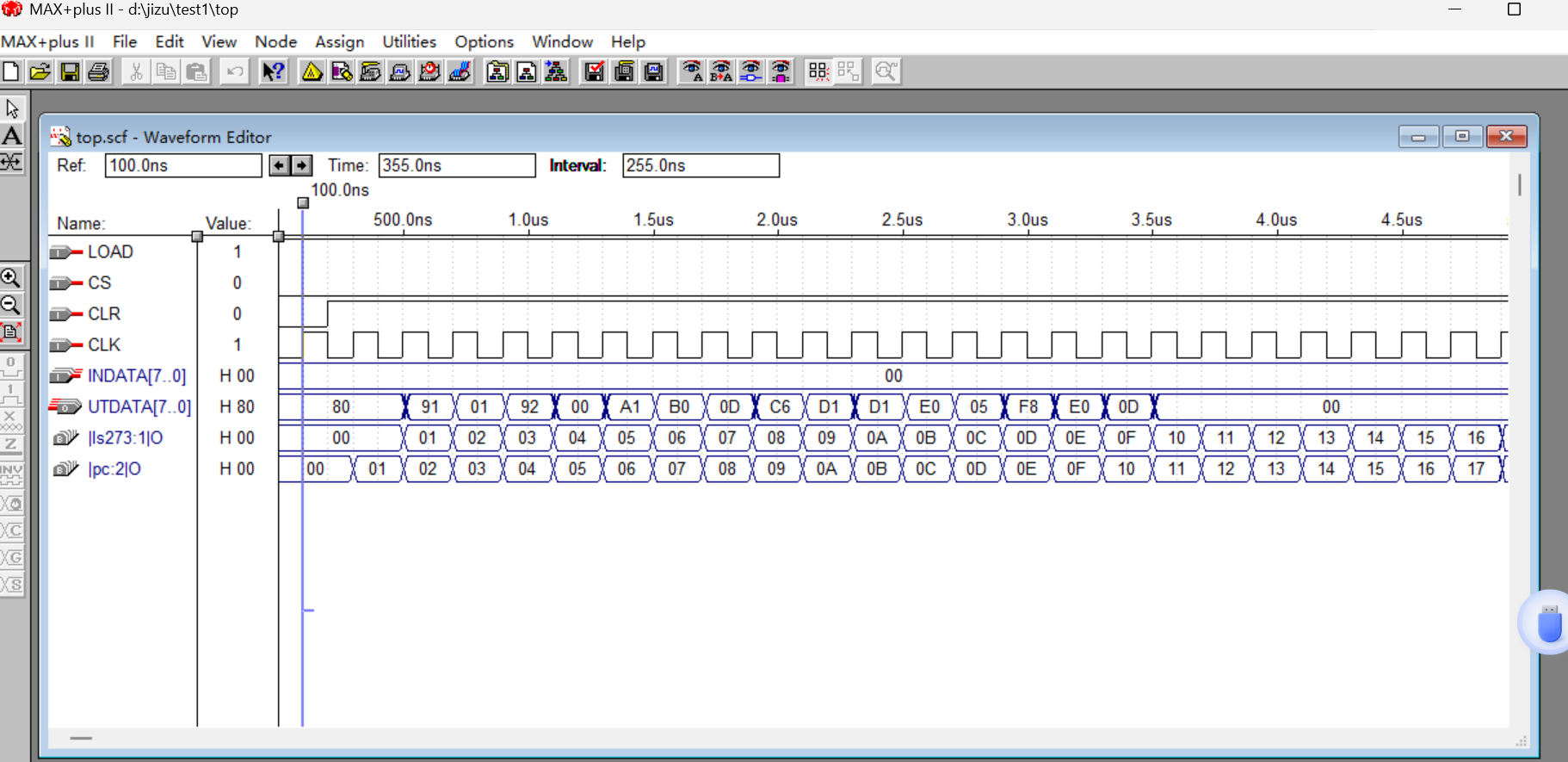

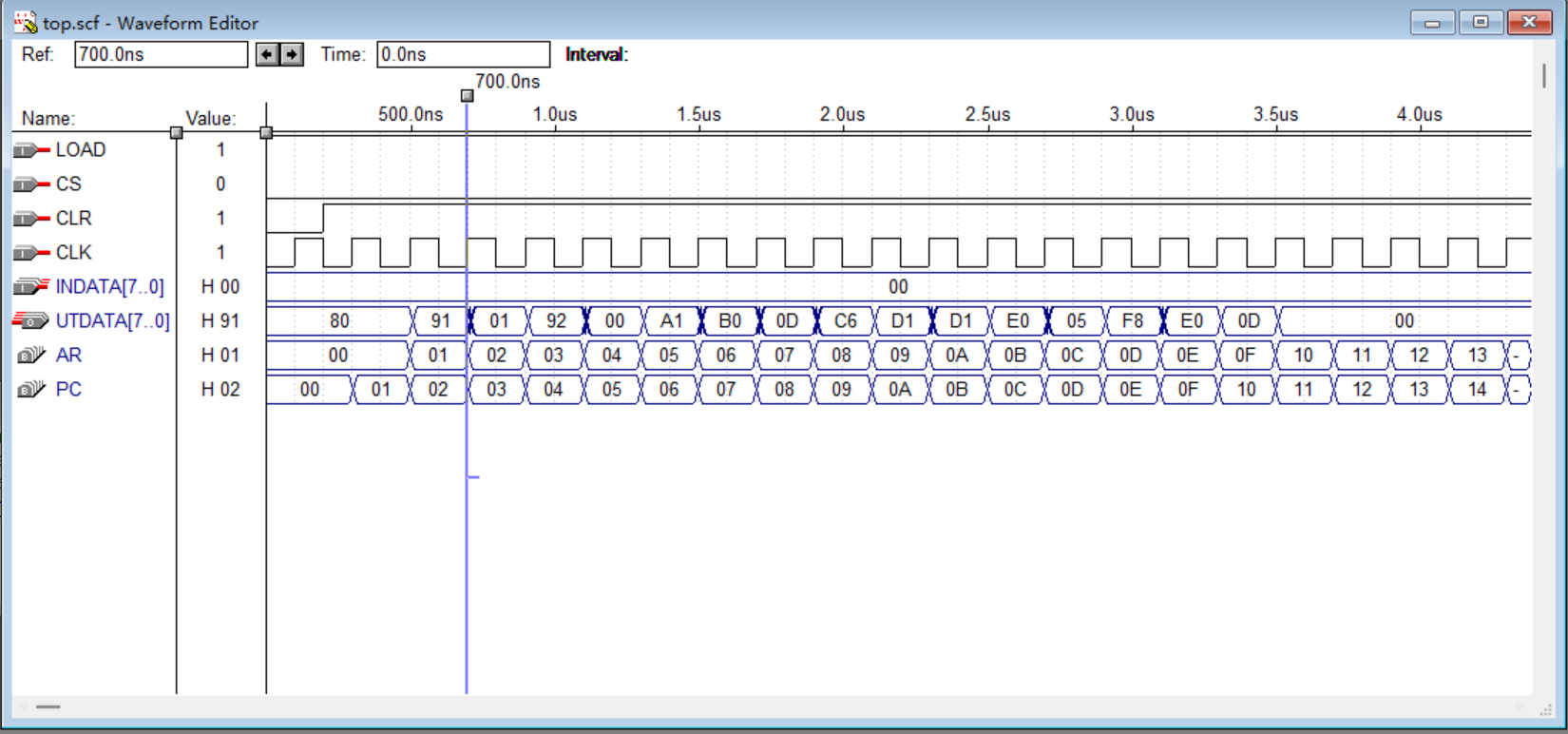

时序仿真波形结果如图所示

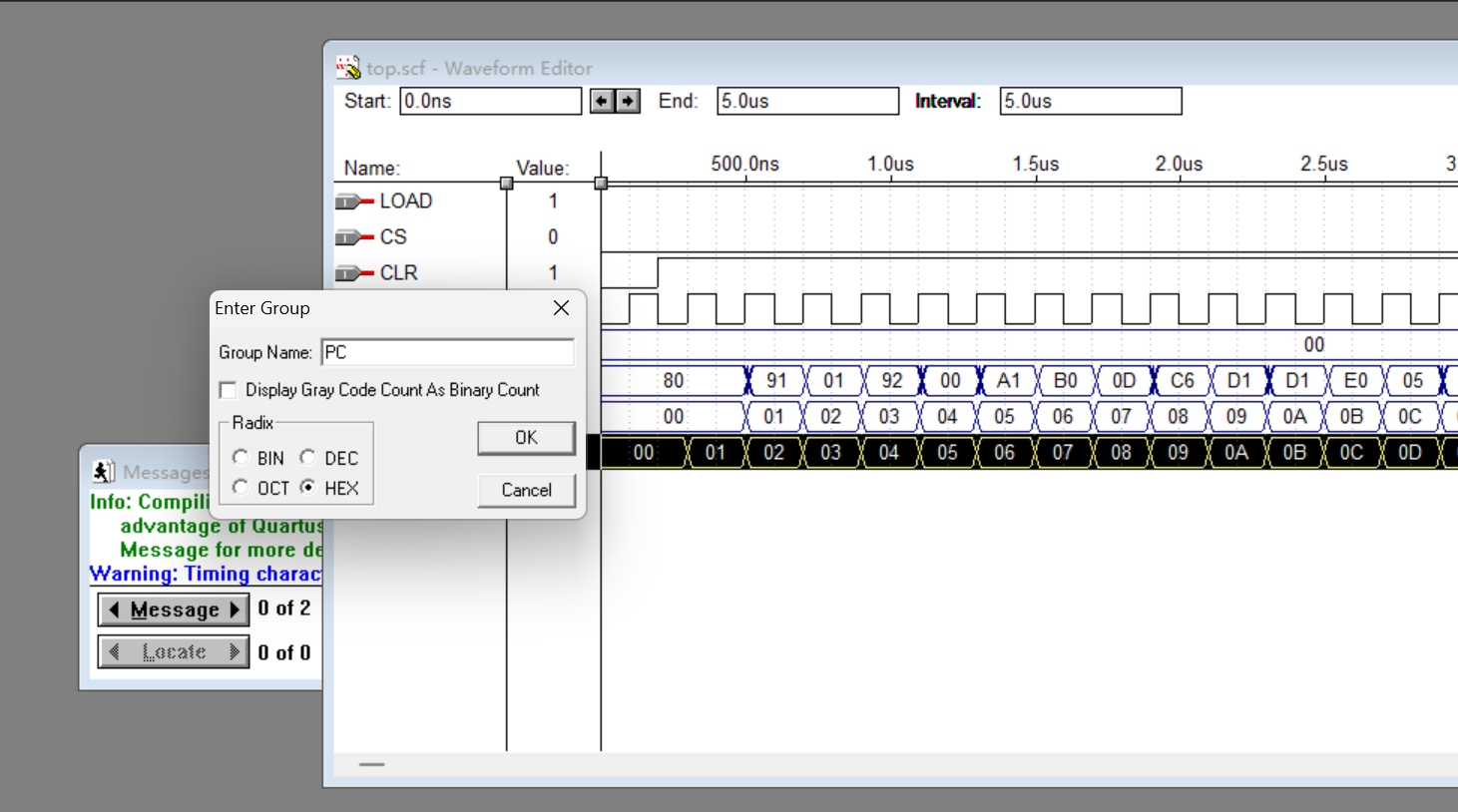

双击pc:2IO,出现对话框,把名字修改为PC,如果你的value值不是16进制,可以点击HEX修改进制。

将ls273:1|O修改为AR,全部修改完毕后,我们的仿真波形到这里全部完成。

到这里的完美收官了

结束,完结撒花~

1031

1031

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?