开源仓库

如果仓库的代码对你有帮助记得Star!

MaxPlusII设计 3x3阵列乘法器

全加器

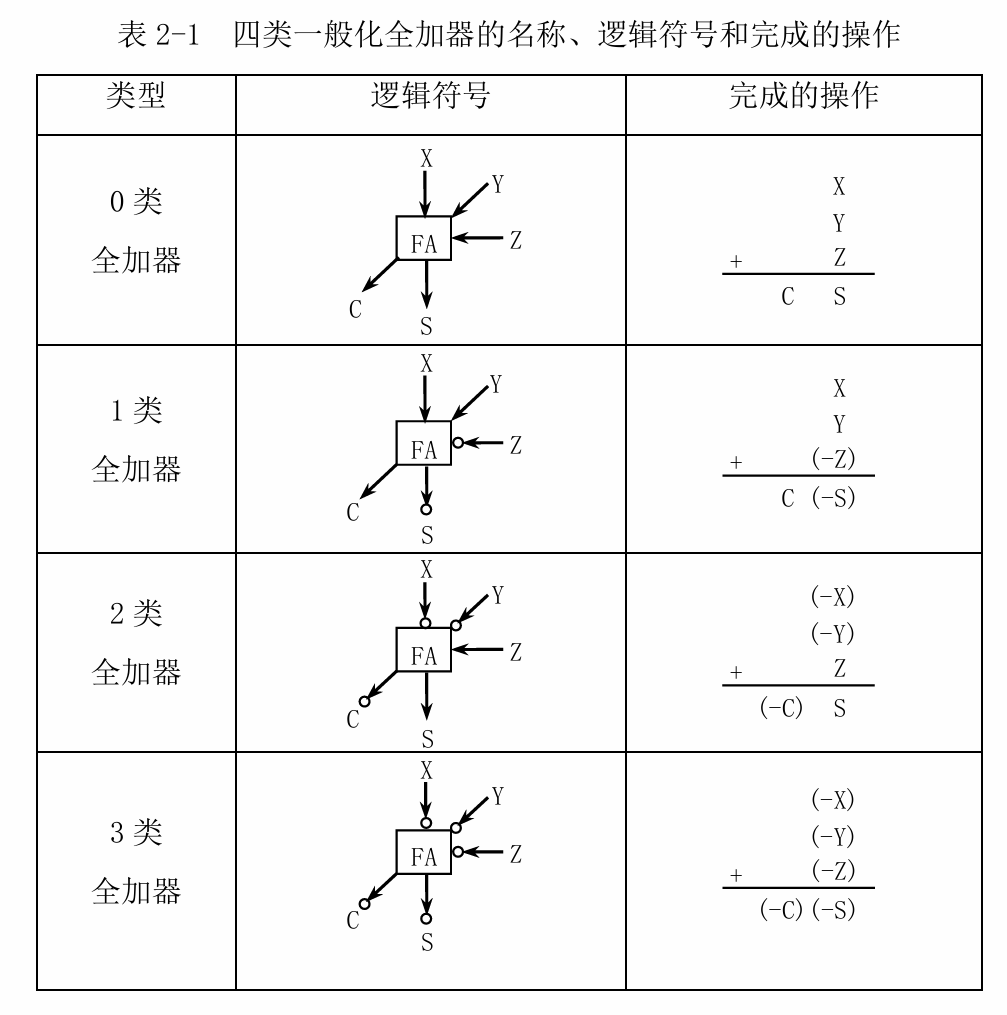

已知:

根据表2-1,可以推导出这四类全加器S和C的逻辑表达式。

Si = Xi ⊕ Yi ⊕ Zi-1

Ci = XiYi + Zi-1(Xi + Yi)

-

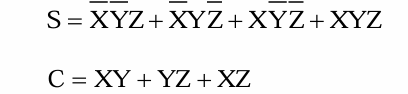

对0类、3类全加器而言有:

-

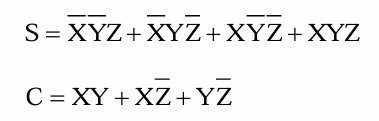

对1类、2类全加器,则有:

0类和3类全加器中S和C的逻辑表达式相同,它和常规的全加器是一致的。1类和2类全加器中S 和C的逻辑表达式也是相同的。

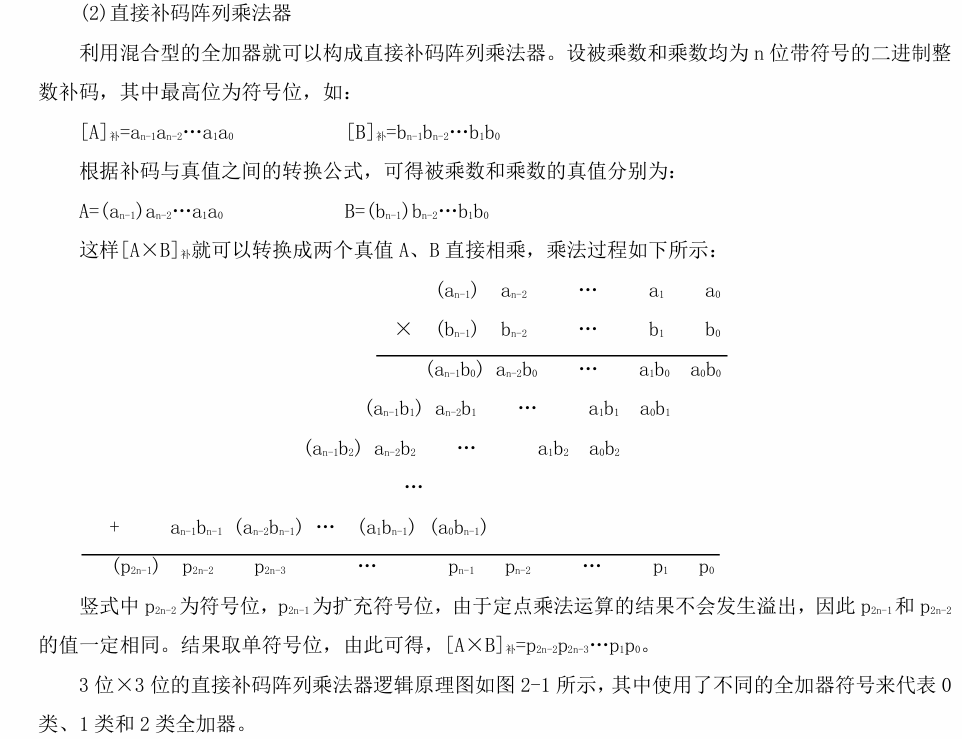

阵列乘法器逻辑原理

注意理解输入的符号位 和 输出的 补充符号位。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1615

1615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?