起始工程是原来的helloworld 工程,若有不清楚,那就先实验了helloworld,再来开始这个实验。

http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html 是主要参考资料,详细原理请参考原文。

原文实验是Vivado 2014, 我的验证测试是在 Vivado 2018.2.

实验内容是用 AXI DMA 存取DDR 内存的数据,给一个ip 应用, 这里简单为 AXI4-FIFO,然后构成一个回路。写数据,然后校核数据,如果一致就表示成功。

1:添加 AXI DMA

在 Vivado 中打开原来的helloworld 工程,Save As 本工程的名字 RDddr,作为工程起点。

打开原理图, 在其中 Add IP,选择 AXI Direct Memory Access,

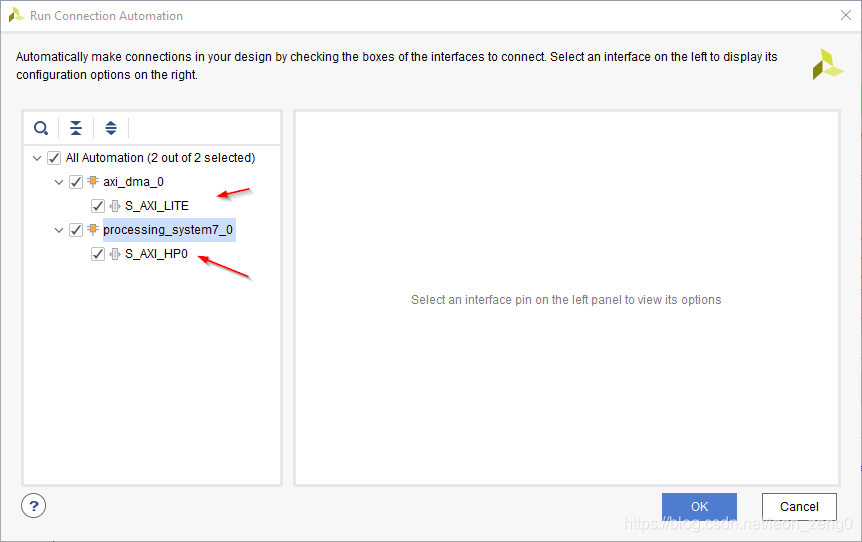

加入后,点击 ‘Run Connection Automation

下拉菜单中选择 /axi_dma_0/S_AXI_LITE

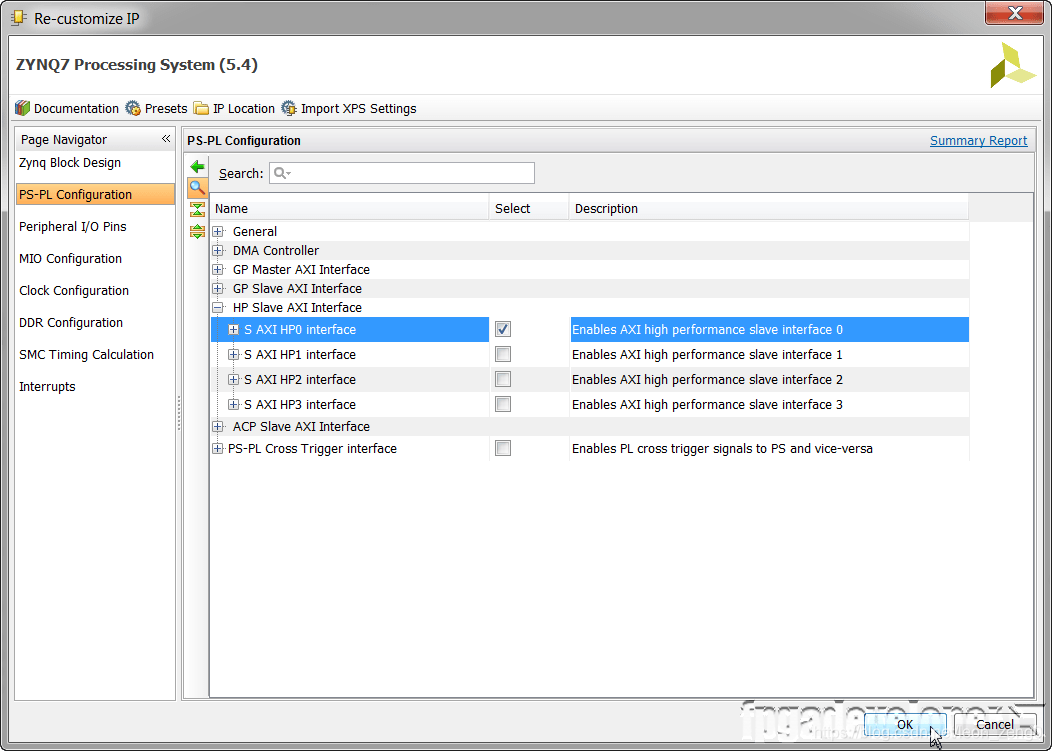

更改zynq 7000 的设置 , 选择 PS_PL Configuration, 选择 HP Slave AxI Interface, 勾选第一个HP0

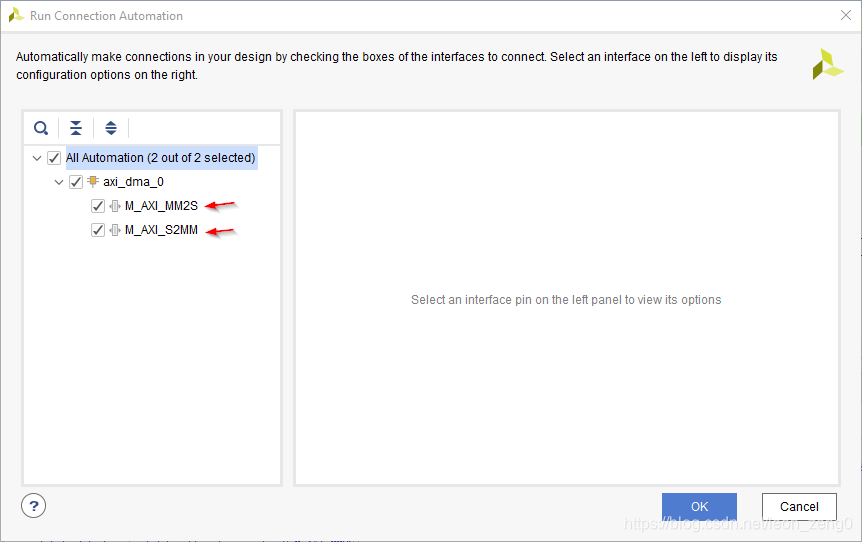

自动连接:点击 ‘Run Connection Automation

2:添加 FIFO

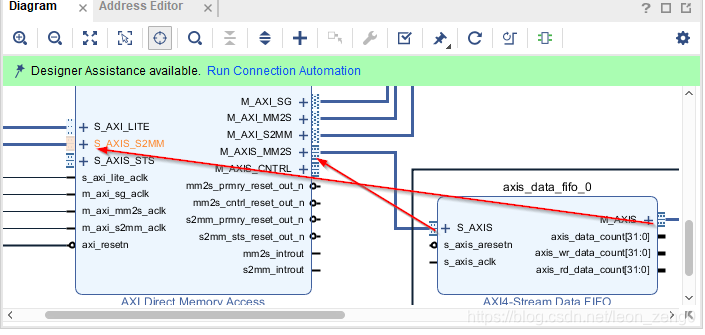

ADD IP , 选择 'AXI4-Stream Data FIFO’

连线:fifo 的 M_AXIS => dma 的 S_AXIS_S2MM

fifo 的 S_AXIS => dma的 M_AXIS_MM2S

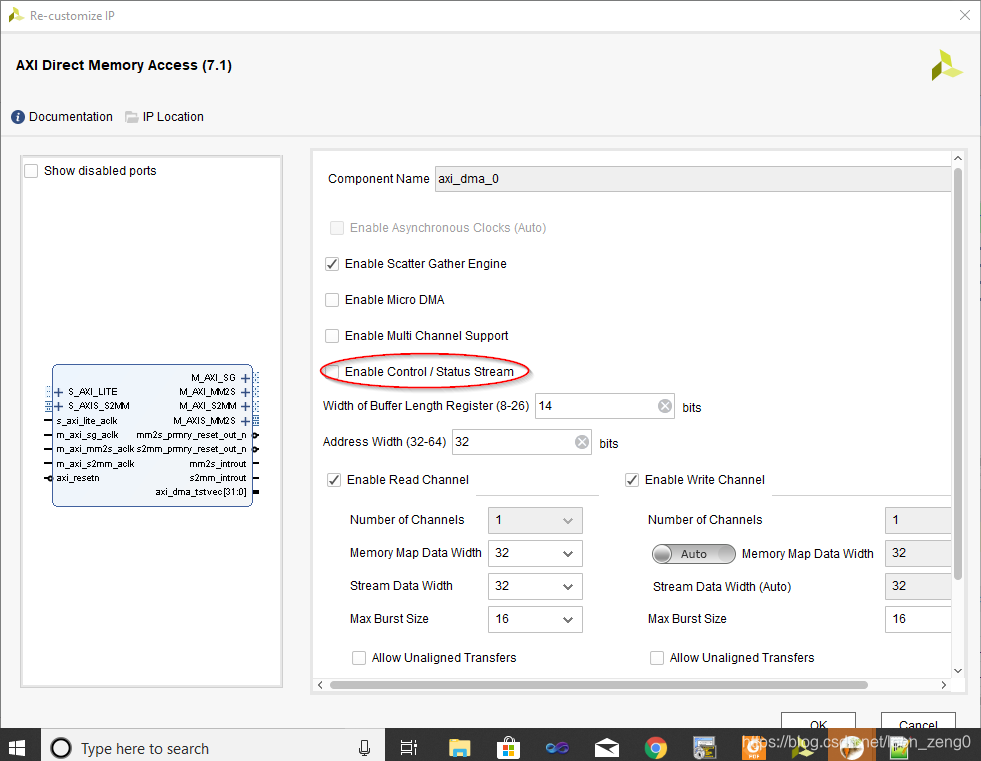

清除 dma 的 AXI-Streaming status and control ports,因为本实验没有用到这2个,所以清除,如果你的ip 用到就要保留。

3:连接dma 的中断到 PS

dma 的 mm2s_introut’ 和 ‘s2mm_introut 需要连接到ps

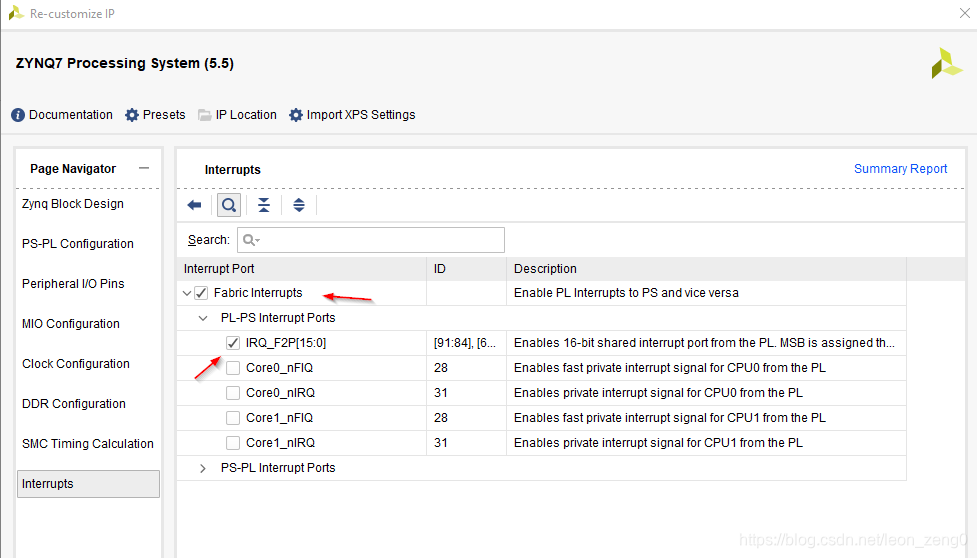

使能 ps 的 pl-ps 中断:

添加一个 ip , Concat, 然后连线, mm2s_introut’ 和 ‘s2mm_introut 分别到 Concat的 2个输入In0和 In1,concat 的输出到 ps 的 ‘IRQ_F2P’口

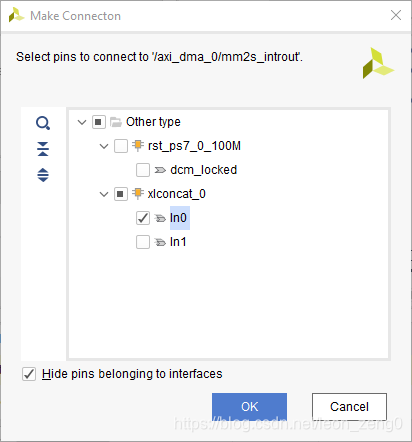

连线也可如下操作,选择 s2mm_introut, 然后 右键,选择 Make Connecton,然后出现如下对话框, 选择 In0

Connection 才对吧,但他是 Connecton。

4:后续处理

Tools->Validate 校验下原理图,应该没错。然后可以 原理图图标 Regenerate Layout,更改布局清楚一些。

产生流文件, 输出硬件Export Hardware, Launch SDK。

5:SDK 编程

在 SDK 里 新建一个工程, helloworld,我们就让他显示 helloworld。 编译测试都没问题了。

下面我们修改代码。在你的系统里 找到如下文件, ()里内容要修改版本号, 实在不行,你在 Xilinx 目录下 搜索。

C:\Xilinx\SDK\(version)\data\embeddedsw\XilinxProcessorIPLib\drivers\axidma_v(ver)\examples\xaxidma_example_sg_poll.c把这个文件里的内容替换掉你原来helloworld 的内容,并保存。 调试运行,应该如下显示:

--- Entering main() ---

Successfully ran AXI DMA SG Polling Example

--- Exiting main() ---

那个目录下还要几个文件,你也可替换试试。

至于读写的位置 在dma 程序段设置,你看看代码吧。 而我们设计的ip 就替换掉 fifo 这个ip,这个是我们真正的应用。

本文介绍到此。

本博客详细介绍了如何在Vivado 2018.2中使用AXI DMA进行DDR内存的读写操作。首先,通过添加AXI DMA IP并配置接口,接着添加FIFO并建立DMA与FIFO的连接。然后,将DMA中断连接到PS,完成PL到PS的中断设置。最后,在SDK中编程验证DMA功能,实现数据回路校核。

本博客详细介绍了如何在Vivado 2018.2中使用AXI DMA进行DDR内存的读写操作。首先,通过添加AXI DMA IP并配置接口,接着添加FIFO并建立DMA与FIFO的连接。然后,将DMA中断连接到PS,完成PL到PS的中断设置。最后,在SDK中编程验证DMA功能,实现数据回路校核。

3039

3039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?