xilinx官网axi-dma介绍

一、认识axi-dma的接口

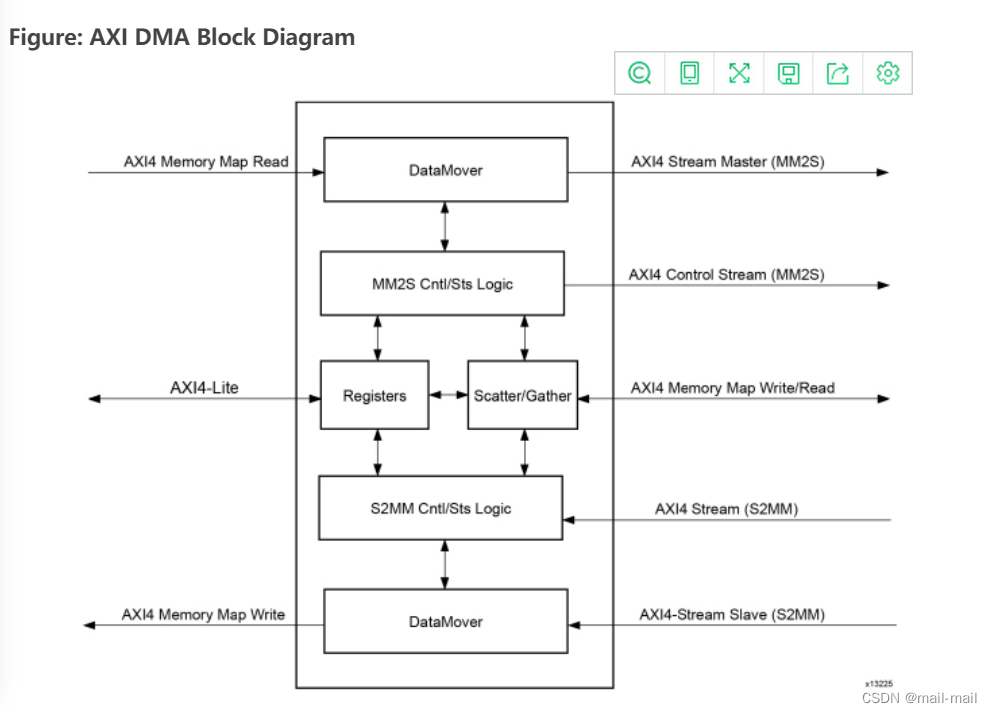

先来认识下 AXI DMA 模块

此模块用到了三种总线,

AXI4-Lite 用于对寄存器进行配置,

AXI4 Memory Map 用于与内存交互,在此模块中又分立出了 AXI4 Memory Map Read 和 AXI4 Memory Map Write 两个接口,又分别叫做 M_AXI_MM2S 和 M_AXI_S2MM,一个是读一个是写,这里要搞清楚,不能混淆。

AXI4 Stream 接口用于对外设的读写,其中 AXI4 Stream Master(MM2S)用于对外设写, AXI4-Stream Slave(S2MM)用于对外设读。

另外还支持Scatter/Gather 功能,但本实验不再讲述,留待用户研究。(MM2S 表示 Memory Map to Stream, S2MM 表示 Stream to Memory Map)。

AXI Memory Map 数据宽度支持 32, 64, 128, 256, 512, 1024bits

AXI Stream 数据宽度支持 8, 16, 32, 64, 128, 256, 512, 1024bits

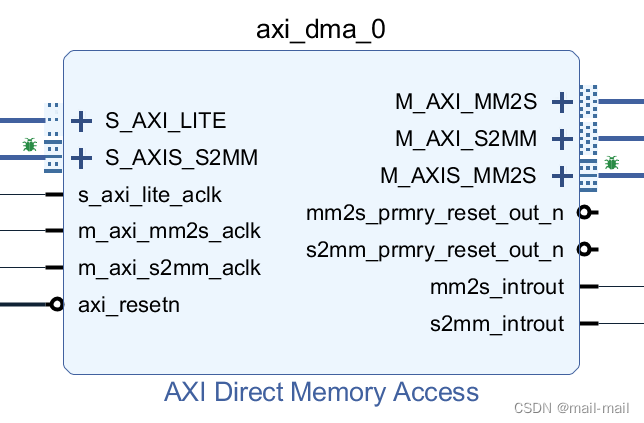

在vivado中视图

接口的分类

S_AXI_LITE是ARM配置DMA寄存器的接口;

S2MM和MM2S表示数据的方向,

MM2S :memory

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1473

1473

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?