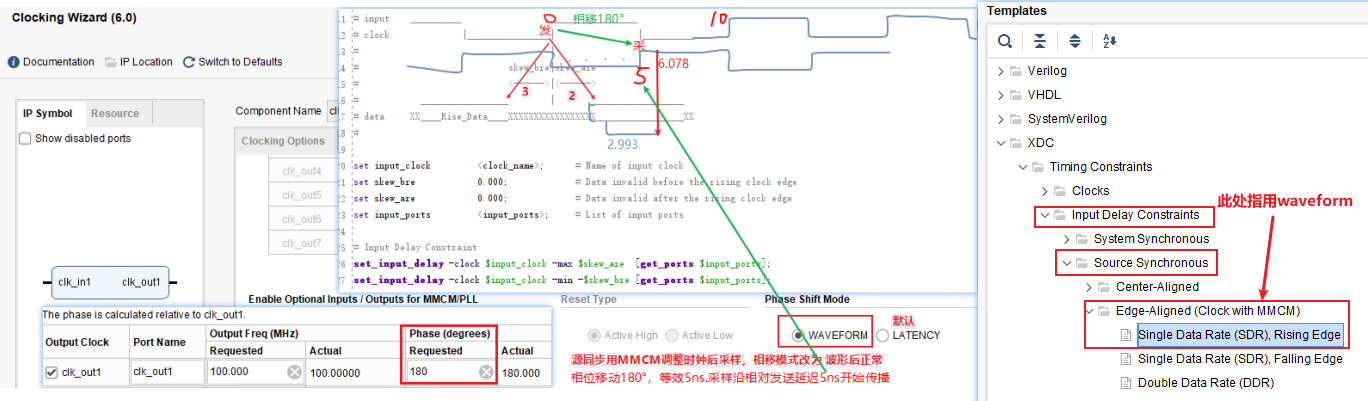

1、输入clk用MMCM-waveform做翻转

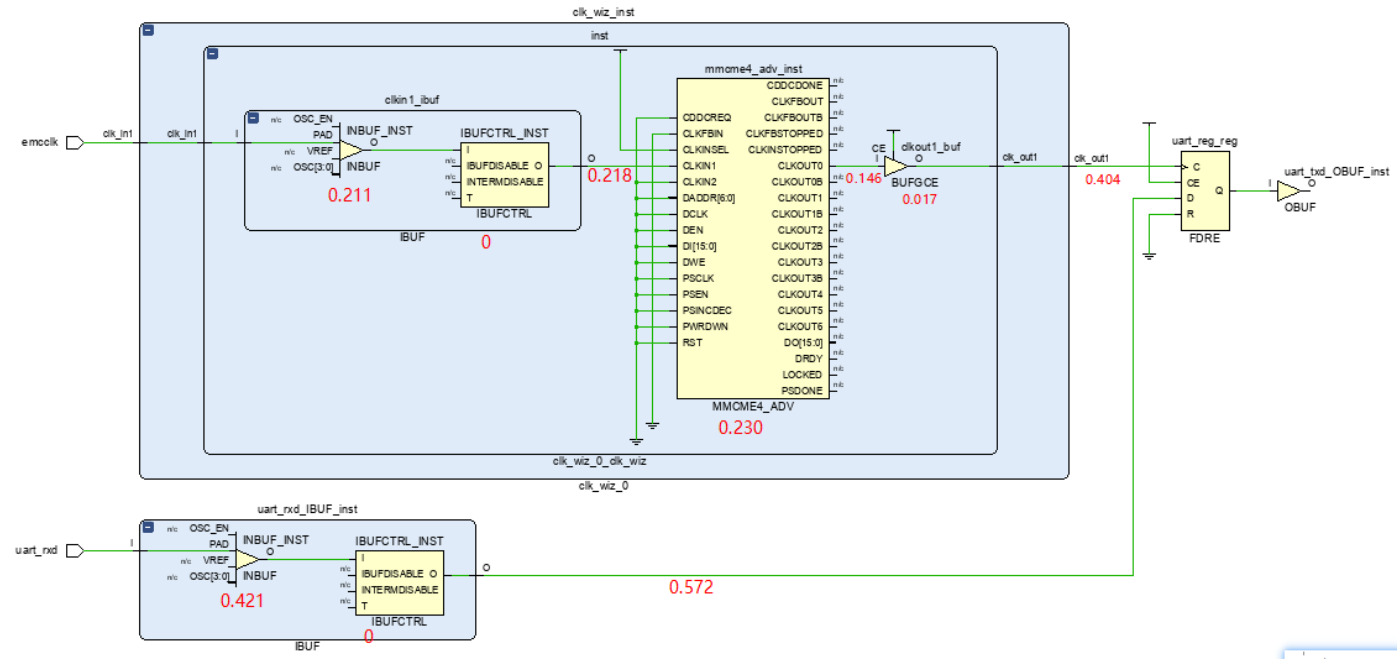

下图中的input约束为源同步边沿对齐,SDR rise采样。在FPGA中用MMCM对输入emcclk时钟做180°翻转后得clk_out1采样,默认在发送emcclk后的第一个采样clk的rise采样。

源同步的时钟、数据应在同一BANK就近放置。可以使用多周期set_multicycle_path调整默认的建立/保持分析沿。

set_input_delay -clock emcclk -max 2 [get_ports uart_rxd]

set_input_delay -clock emcclk -min -3 [get_ports uart_rxd]

2、vivado中的路径分析

分析Required Time的时间起点不再从0开始,而是直接从偏移后的相位5ns开始,但是整个输入路径的延时都在。-waveform 后时钟的相位突变,后续有其独立的分析起点。-latency时后续分析的起点仍然是0或T,仅在MMCM中增加了延时。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

937

937

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?