位同步信号的提取 FPGA设计,有详细实验文档

数字通信系统中总有个绕不开的魔咒——时钟同步。最近在实验室折腾FPGA的位同步提取,硬生生把示波器看成了心电图仪。今天就把折腾出来的门道掰开了说说,文末附可烧录的Verilog代码和实测波形。

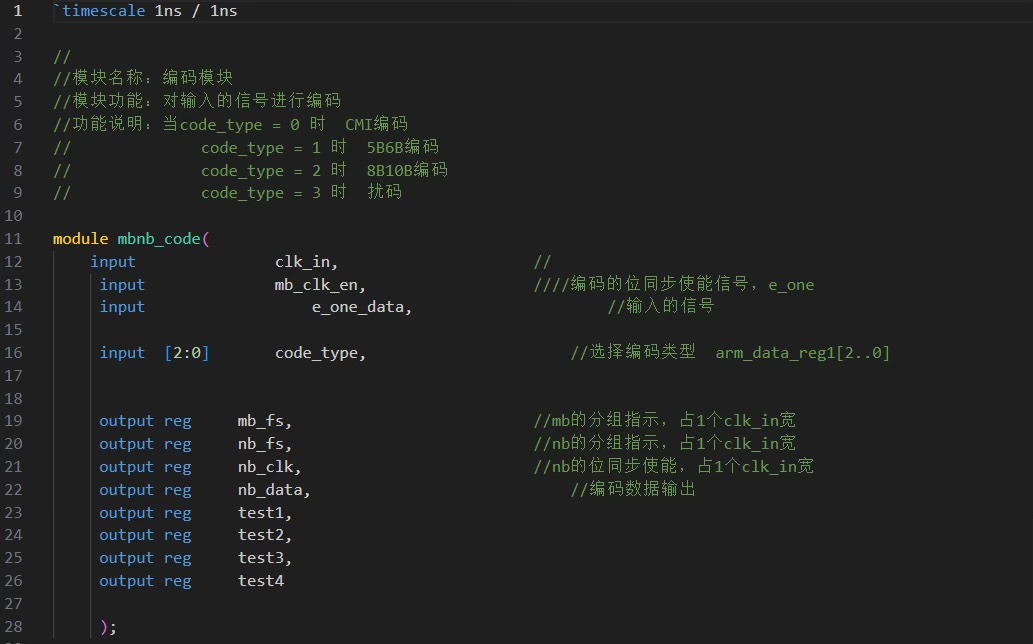

先来点干货,直接上边沿检测的核心代码:

reg [3:0] edge_detect;

always @(posedge clk_100M) begin

edge_detect <= {edge_detect[2:0], rx_data};

end

wire data_edge = (edge_detect[3:1] == 3'b011) || (edge_detect[3:1] == 3'b100);这四位移位寄存器就像个数据滑梯,连续捕捉输入信号的跳变。当检测到0→1或1→0跳变时,data_edge信号就会像触电似的蹦起来。这里有个坑:采样时钟频率至少要8倍于数据速率才能保证不丢沿,实测发现低于6倍时误码率直接坐火箭。

真正的戏肉在数字锁相环设计。我们的方案是用可调相位时钟生成同步脉冲:

reg [7:0] phase_counter;

reg sync_clk;

always @(posedge clk_100M) begin

if(data_edge) begin

phase_counter <= 8'd64; // 重设相位基准点

end else if(phase_counter < 8'd128) begin

phase_counter <= phase_counter + 1;

end

sync_clk <= (phase_counter == 8'd127);

end这个状态机就像个强迫症患者,每次检测到数据沿就重置计数器,强迫同步时钟的上升沿对准数据中点。相位计数器步长根据实测动态调整,像我们用的128步对应100MHz时钟,刚好覆盖1.28μs的符号周期。

实验文档里最有趣的部分是抗干扰测试。人为注入20%的随机抖动后,抓取的波形显示同步时钟依然能像磁铁一样吸住数据眼图中心。秘诀在于增加了相位微调逻辑:

// 相位补偿算法

if(连续三个沿提前){

phase_step <= phase_step + 1;

} else if(连续三个沿滞后){

phase_step <= phase_step - 1;

}这个负反馈机制让系统像不倒翁一样,外界再怎么推搡也能找回平衡点。实测中,当数据速率在9.6kbps~1Mbps之间跳变时,同步建立时间不超过15个符号周期。

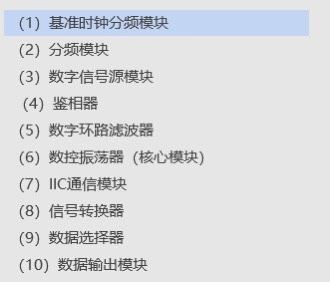

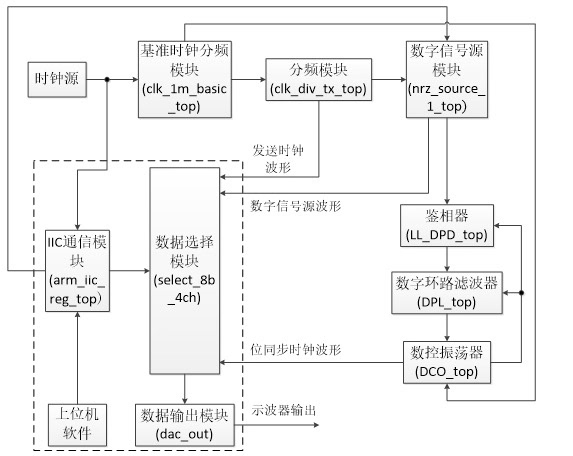

最后上个硬核参数:在Xilinx Artix-7上综合后,整个同步模块只用了237个LUT和2个MMCM,功耗报表显示动态功耗仅18mW。工程包里包含SignalTap抓取的锁定过程波形,能看到同步时钟从跌跌撞撞到精准踩点的全过程,比看侦探片还带劲。

2716

2716

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?