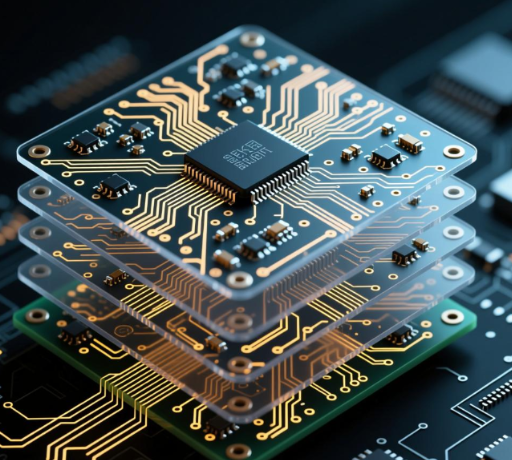

在多层 PCB(4 层及以上)设计中,“叠加设计” 是决定性能上限的核心环节 —— 它并非简单增加层数,而是通过合理规划信号层、电源层、接地层的位置关系、层压顺序、介质厚度,实现信号完整性、EMC 兼容性、供电稳定性的协同优化。与普通双层 PCB 相比,叠加设计的核心价值在于 “层间分工协同”:电源层与接地层相邻降低供电阻抗,信号层贴近接地层减少辐射干扰,多层信号层分流高密布线,让复杂 PCB(如服务器主板、工业控制板)在有限空间内实现低损耗、低干扰传输。今天,我们从基础入手,解析 PCB 叠加设计的定义、核心作用、层数选择原则与常见误区,帮你建立系统认知。

PCB 叠加设计的核心定义:指多层 PCB 的 “层功能分配 + 层压结构规划”,包括确定层数(4/6/8 层等)、各层功能(信号 / 电源 / 接地 / 介质)、层间顺序(如信号层 - 接地层 - 电源层 - 信号层)、介质层厚度(0.1-0.5mm),最终目标是:电源阻抗≤10mΩ、信号串扰≤-30dB、PCB 翘曲度≤0.75%(IPC-6012 标准)。与双层 PCB 相比,其核心差异体现在三个维度:一是 “干扰控制”,双层 PCB 电源与信号同层,干扰耦合强(串扰 - 20dB),叠加设计通过独立电源 / 接地层,串扰可降至 - 35dB;二是 “布线能力”,双层 PCB 布线密度≤10 点 /cm²,8 层叠加设计可提升至 30 点 /cm²;三是 “阻抗稳定性”,叠加设计中信号层与接地层距离固定,阻抗偏差≤±5%,双层 PCB 易因布线不均导致偏差 ±10%。

叠加设计的核心作用,由层间协同逻辑决定:① 降低供电干扰:电源层与接地层紧密相邻(间距≤0.2mm),形成低阻抗供电网络(PDN),电源噪声从 100mV 降至 30mV;② 优化信号完整性:信号层贴近接地层(间距 0.1-0.3mm),减少信号辐射损耗(1GHz 信号损耗从 2dB/m 降至 0.8dB/m);③ 提升 EMC 性能:多层接地层形成屏蔽,外部辐射干扰减少 40%;④ 适配高密布线:多层信号层分流不同类型信号(模拟 / 数字 / 高频),避免布线交叉冲突。

层数选择是叠加设计的首要决策,需结合 “信号密度、电源路数、频率、成本” 综合判断:

-

4 层板(最常用):经典叠加结构为 “Top(信号)-GND - 电源 - Bottom(信号)”,适合消费电子(WiFi 路由器)、简单工业控制板,支持 2-3 路电源、布线密度≤15 点 /cm²,频率≤1GHz;

-

6 层板:对称结构 “Top(信号)-GND - 模拟信号 - 电源 - 数字信号 - Bottom(信号)”,适合工业 PLC、汽车电子,支持 4-6 路电源、频率≤5GHz,抗干扰能力比 4 层板强 30%;

-

8 层板:对称结构 “Top(高频信号)-GND - 模拟信号 - 电源 - GND - 数字信号 - GND-Bottom(高频信号)”,适合服务器主板、5G 模块,支持 8 路以上电源、频率≤10GHz,信号串扰≤-40dB;

-

层数误区:并非层数越多越好,盲目增加层数(如用 8 层板设计简单传感器)会导致成本上升 50%,且层压难度增加(分层率从 1% 升至 3%)。

分享一个实际案例:某厂商用双层 PCB 设计工业控制板(含 3 路电源、100 个信号点),导致电源噪声 80mV、串扰 - 22dB,无法满足 EMC 要求;改用 4 层叠加设计(Top - 信号 - GND - 电源 - Bottom)后,电源噪声降至 25mV,串扰 - 33dB,顺利通过认证。

PCB 叠加设计的基础认知需聚焦 “层间协同”,层数选择需平衡性能与成本,避免盲目堆叠,才能为后续细节设计奠定基础。

284

284

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?