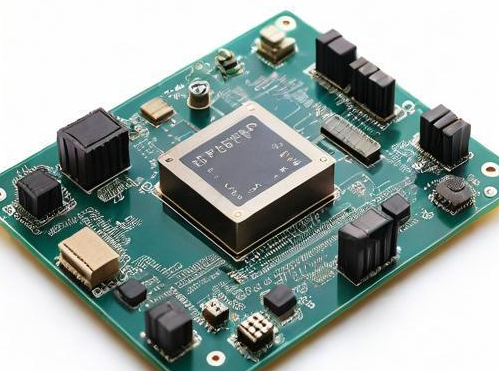

可持续 PCB 布局的核心目标之一是 “材料高效利用”—— 通过优化板型、元件排布、布线方式,减少 FR-4 基材、铜箔、阻焊剂等材料消耗,同时避免因材料浪费导致的生产能耗增加。与传统布局 “先功能后面积” 的思路不同,可持续布局需在设计初期就将 “材料利用率” 纳入核心指标,通过毫米级的细节优化,实现每万片 PCB 减少数十公斤材料消耗。今天,我们解析可持续 PCB 布局中材料高效利用的具体策略,包括板型优化、元件排布优化、布线优化,结合实际案例帮你掌握落地方法。

一、板型优化:减少基材废料的 “第一步”

PCB 板型直接决定基材利用率,传统异形板型(如圆形、不规则多边形)的废料占比常达 15%-25%,而矩形板型废料占比可控制在 5%-10%,通过以下策略优化板型:

1. 优先选择矩形板型,适配基材开料规格

PCB 基材(如 FR-4 覆铜板)的标准尺寸多为 1220mm×1020mm、1220mm×1830mm,矩形 PCB 可最大化适配基材开料,减少裁剪废料:

-

板型尺寸设计:根据基材规格计算 “最优矩形尺寸”,例如基材 1220mm×1020mm,若 PCB 设计为 100mm×80mm,每块基材可裁 12×12=144 片(废料仅 1220×1020 - 144×100×80=1244400-1152000=92400mm²,废料率 7.4%);若设计为 105mm×85mm,每块基材仅能裁 11×12=132 片(废料 1244400-132×105×85=1244400-1171800=72600mm²,废料率 5.8%),虽单块 PCB 面积增大,但基材利用率更高;

-

避免 “非必要异形”:若设备外壳限制需异形,尽量将异形部分设计为 “可裁剪的小凸起”,而非大面积不规则凹陷。例如,某智能手表 PCB 传统设计为圆形(直径 40mm,面积 1256mm²),每块 1220×1020mm 基材仅能裁 24×24=576 片(废料率 35%);优化为 “矩形 + 小弧形凸起”(面积 1300mm²),每块基材可裁 23×24=552 片,废料率降至 18%,虽单块面积略增,但总基材消耗减少 48%。

2. 合并相似功能 PCB,减少整体面积

若设备包含多块独立 PCB(如电源板、控制板、接口板),可通过 “功能合并” 设计为单块 PCB,减少板间连接材料(如连接线、连接器)消耗,同时降低总基材面积:

-

合并原则:功能关联紧密、信号交互频繁的 PCB 优先合并(如电源板与控制板合并,减少电源线损耗与连接器消耗);

-

隔离设计:合并后不同功能区域通过 “接地隔离带”(宽度≥1mm)分隔,避免信号干扰。某工业传感器设备传统采用 3 块 PCB(电源板 40cm²、控制板 50cm²、接口板 30cm²),总基材面积 120cm²,连接器消耗 15 个;合并为单块 PCB(面积 95cm²)后,基材消耗减少 20.8%,连接器减少至 5 个,同时减少连接线长度 300mm,铜消耗进一步降低。

二、元件排布优化:紧凑化与有序化的平衡

元件排布是材料高效利用的核心环节,需在 “紧凑化” 与 “散热、维修可行性” 之间平衡,避免因过度紧凑导致散热失效或维修困难。

1. 按 “尺寸 - 功能 - 发热” 分类排布,减少间隙浪费

-

尺寸分类:将同封装尺寸的元件(如 0402 电阻电容、SOT23 晶体管)集中排布,避免不同尺寸元件混排导致的间隙浪费(同尺寸排布比混排间隙减少 20%);

-

功能分类:同一功能模块的元件(如电源模块的整流桥、滤波电容、稳压器)集中排布,缩短模块内布线长度(平均缩短 15%);

-

发热分类:低发热元件(如电阻、电容,发热功率<0.1W)围绕高发热元件(如电源芯片,发热功率>1W)排布,利用高发热元件的散热空间,避免单独预留散热间隙。某消费电子 PCB 传统混排元件,间隙浪费达 12%;分类排布后,间隙浪费降至 5%,PCB 面积从 80cm² 缩小至 70cm²。

2. 利用 “边角空间”,填充小型元件

PCB 板型边缘或大型元件(如 CPU、连接器)周围常存在 “边角空间”(面积<1cm²),可填充小型元件(如 0402 电阻电容、LED 指示灯),避免空间浪费:

-

空间评估:边角空间需满足元件最小排布要求(如 0402 元件需≥0.3mm×0.3mm 空间);

-

优先级排序:填充非关键小型元件(如限流电阻、指示灯),避免影响关键元件散热与维修。某服务器 PCB 的 CPU(尺寸 20mm×20mm)周围存在 4 处边角空间(每处 0.8cm²),填充 0402 电阻电容后,减少额外布线面积 3.2cm²,PCB 总面积从 150cm² 缩小至 146.8cm²。

三、布线优化:缩短长度与减少层数的协同

布线长度直接决定铜箔消耗(每 100mm 长、0.2mm 宽、1oz 厚的布线消耗 0.0105g 铜),同时布线层数影响基材与阻焊剂消耗,需通过优化减少两者消耗。

1. 最短路径布线,减少铜箔消耗

-

优先表层布线:表层布线无需过孔,减少过孔铜消耗(每个 0.3mm 过孔消耗 0.005g 铜),同时缩短路径;

-

避免 “绕线”:通过 “扇出优化”(元件引脚扇出路径最短),减少绕线长度(平均减少 25%);

-

差分对并行布线:高频差分信号(如 USB 3.0)采用并行布线,避免交叉导致的长度增加。某医疗设备 PCB 传统布线长度平均 800mm / 块,最短路径优化后降至 600mm / 块,每块 PCB 铜消耗减少 2.1g,万片减少 21kg 铜。

2. 合理规划层数,避免过度设计

传统布局常为 “方便布线” 盲目增加层数(如 4 层可满足却用 6 层),而每层需消耗基材、铜箔、阻焊剂,层数每增加 2 层,材料消耗增加 30%。可持续布局需按 “功能需求最小化层数”:

-

层数评估:根据信号数量、电源路数计算最小层数(如 2 路电源、50 路信号,2 层可满足;10 路电源、200 路信号,4 层可满足);

-

共享层资源:低频信号与电源线路共享内层(如 2 层 PCB 的内层同时作为电源层与低速信号层),避免单独增加层数。某智能家居 PCB 传统设计为 4 层,优化后通过共享内层资源,3 层即可满足需求,基材消耗减少 25%,阻焊剂消耗减少 33%。

可持续 PCB 布局的材料高效利用需 “从板型到布线的细节把控”,通过毫米级优化实现材料消耗显著降低,同时保障设备性能,是可持续设计的核心落地环节。

106

106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?