PCB设计中,关键信号线的布线是确保电路性能和可靠性的关键步骤。这些信号包括电源、模拟信号、高速信号、时钟信号、差分信号和同步信号等。以下是对这些关键信号布线要求的优化和详细说明:

模拟信号布线

模拟信号因其抗干扰能力较弱,需要特别的保护措施。布线时应尽量缩短走线长度以增强抗干扰性。在某些情况下,可以放宽对阻抗控制的要求,适当加粗走线以提高信号的稳定性。此外,应将模拟信号布线限制在特定的区域内,并尽可能远离数字信号,以减少潜在的干扰。

高速信号布线

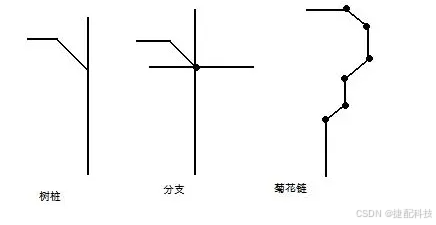

高速信号的布线要求多层板设计,这不仅有助于布线,还能有效降低干扰。在布线时,应尽量减少引线的弯折,优先采用直线或45°折线,以减少信号的辐射和反射。同时,引线应尽可能短,以减少分布电感和电容的影响。过孔的使用也应尽量减少,以避免增加电路的延时。此外,应注意避免信号线的平行分布,以减少交叉干扰。在不可避免的情况下,可以在平行信号线的反面布置大面积的地线来减少干扰。高速信号布线还应避免分枝和树桩,以减少信号的反射和过冲。

时钟信号布线

时钟信号在数字电路中起着至关重要的作用,同时也是电磁辐射的主要来源。在布线时,应优先选择优选布线层,并避免跨分割区布线。时钟信号与其他信号的间距应至少满足3W规则,以减少串扰。对于有EMC要求的设计,较长的时钟线应选择内层布线。时钟信号的端接匹配也非常重要,以减少反射和振荡。此外,应避免使用菊花链结构传送时钟信号,而应采用星型结构,以确保所有时钟负载直接与时钟功率驱动器相连。连接晶振的导线应尽量短,以减少噪声干扰。

差分信号布线

差分信号通过两根极性相反的信号线传输数据,要求这两根线在布线时保持等长、等宽、紧密靠近,并在同一层面。等长是为了保持两个差分信号的相反极性,减少共模干扰。等宽等距则有助于保持信号的一致性和稳定性。在布线时,应尽量为关键信号如时钟信号、高频信号和敏感信号提供专门的布线层,并确保回路面积最小化。通过采用屏蔽和加大安全间距等方法,可以进一步提高信号质量。

在布线过程中,保持清晰的设计思路和严格的布线规则是至关重要的。通过遵循上述原则,可以确保电路的性能和可靠性,同时减少电磁干扰和提高信号完整性。

97

97

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?