介绍

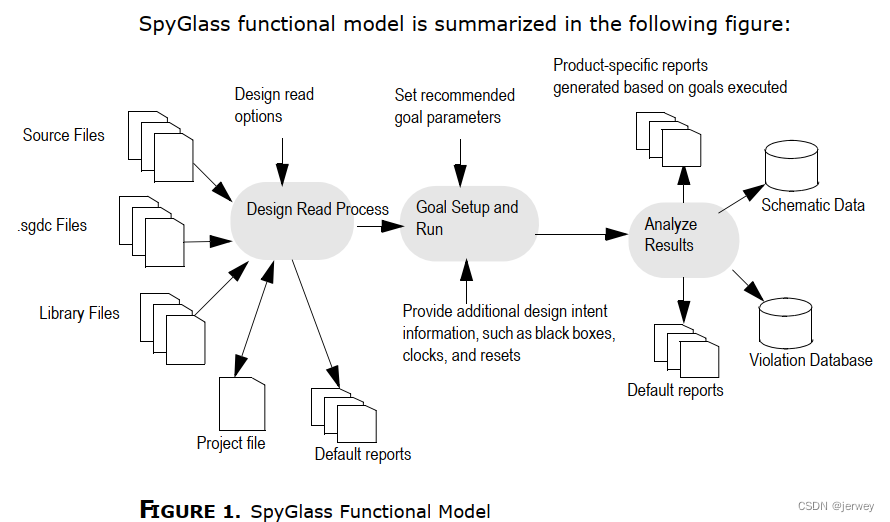

下图为Spyglass的原理流程示意图:

图来自:SpyGlass_Console_Reference.pdf

Spyglass工具的五大功能: lint, CDC(多时钟域检查), LP(低功耗),Constraint(约束),DFT(可测试性)。

lint主要是检查代码的语法,是否是可综合的语言,cdc用于检查跨时钟路径信号是否有问题,以防止出现亚稳态,DFT主要是实现所有的flop clock和reset信号可控。

更多介绍

目的

spyglass lint可对Verilog, VHDL, SystemVerilog等语言进行RTL检查,包括

1)语法检查、代码风格、IP重用规则等

2)位宽不匹配、不完整的case语句,缺少默认条件,缺少else子句、由关系运算符或算术运算符导致的精度损失、缺少驱动

3)可综合性检查

4)仿真过程中可能出现的问题(竞争与冒险、时钟,选择,启用,复位信号设定为常量、未使用的逻辑门、浮空的引脚)

5)结构检查(组合逻辑环路、锁存器及三态输出、控制信号用作数据信号、扇出超过一定数量)

目前包含:SpyGlass Lint, CDC, RDC, DFT ADV, Power. 是业界RTL Signoff 的重要工具.

一些基本概念

-

Rule: 是SpyGlass 进行RTL分析的最小单位.

-

Goal: 是一系列相关Rule的集合,组合起来完成RTL分析的某个特定任务. user可以用GuideWare定义好的Goal, 也可根据工程项目要求来选择一系列rule的集合形成自定义Goal. GUI里面点Goal的button来选择设定, 当然也可在Prj file 里定义.

-

Sub-Methodology: 是一系列相关Goal的集合, 用以达成某方面特定目标, 如完成CDC check.

目前包括 SpyGlass CDC/Constraints/DFT/Power/TXV Methodology -

Methodology : A methodology is a collection of sub-methodologies or a collection of goals.

Each sub-methodology may further contain sub-methodologies or a set of goals where each goal is a collection of rules. -

SGDC : Constraint 文件, 主要包含clock和reset等约束信息.

-

Waiver : 用以过滤一些结果的文件.

-

Severity : report结果中分Fatal, Error, Warning和INFO四等级信息.

-

parameter: 可以在进行RTL分析之前设定某些参数, 对检查过程进行一些约束

启动方式

- To run SpyGlass in the default, GUI mode, type

spyglass or spyglass –project <project name>

- To run SpyGlass in batch mode, type

spyglass –batch –project <project name> \

[-designread|-goals|-showgoals][-group]

GUI模式

- 启动 :source spyglass.env #设置环境变量

spyglaas -gui #启动软件

spyglass &

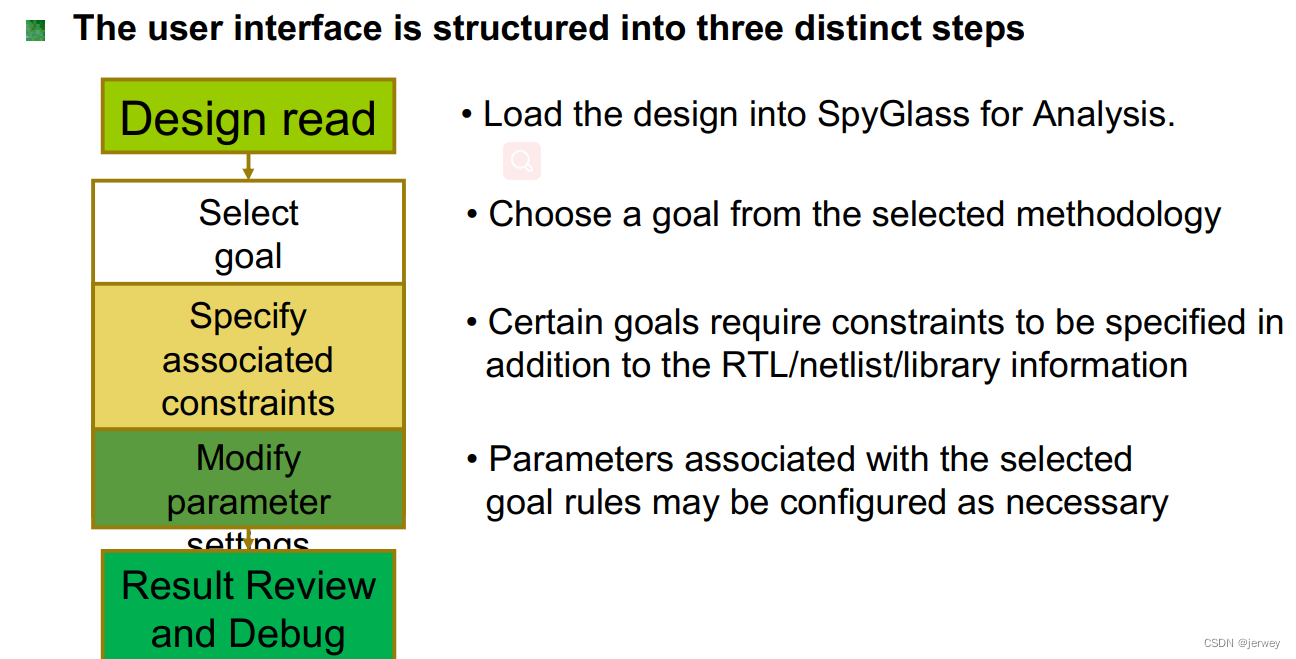

1. Design Setup

点击Design setup 相当于

sg_shell> current_goal Design_Read -top npu_vector

current_goal: info: loading goal `Design_Read' with top `npu_vector' (in progress)

current_goal: info: finished loading goal `Design_Read' (ok)

依次添加file;set option;read design

选中 synthesize netlist相当于

set_option designread_enable_synthesis yes

set_option designread_enable_synthesis no

点击 run design read 相当于:

sg_shell> compile_design -force

把需要的design data准备好,包括网表.v(或者source file list),technology library,sgdc文件(没有的话可以用sdc代替,使用命令set_option sdc2sgdc yes即可

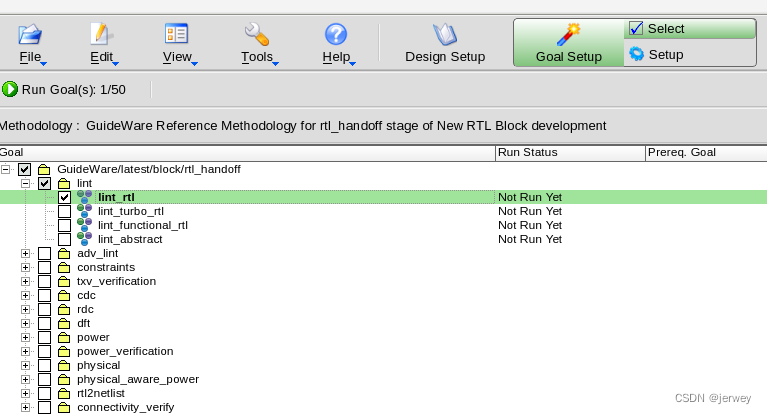

2. Goal Setup

点击Goal setup

sg_shell> current_goal lint/lint_rtl -top npu_vector

current_goal: info: loading goal `lint/lint_rtl' with top `npu_vector' (in progress)

current_goal: info: finished loading goal `lint/lint_rtl' (ok)

select下选择需要检查的Goal

右键编辑该Goal下面的各种rule,点击界面右下角会出现该条rule的解释

点击run goal,相当于

sg_shell> run_goal

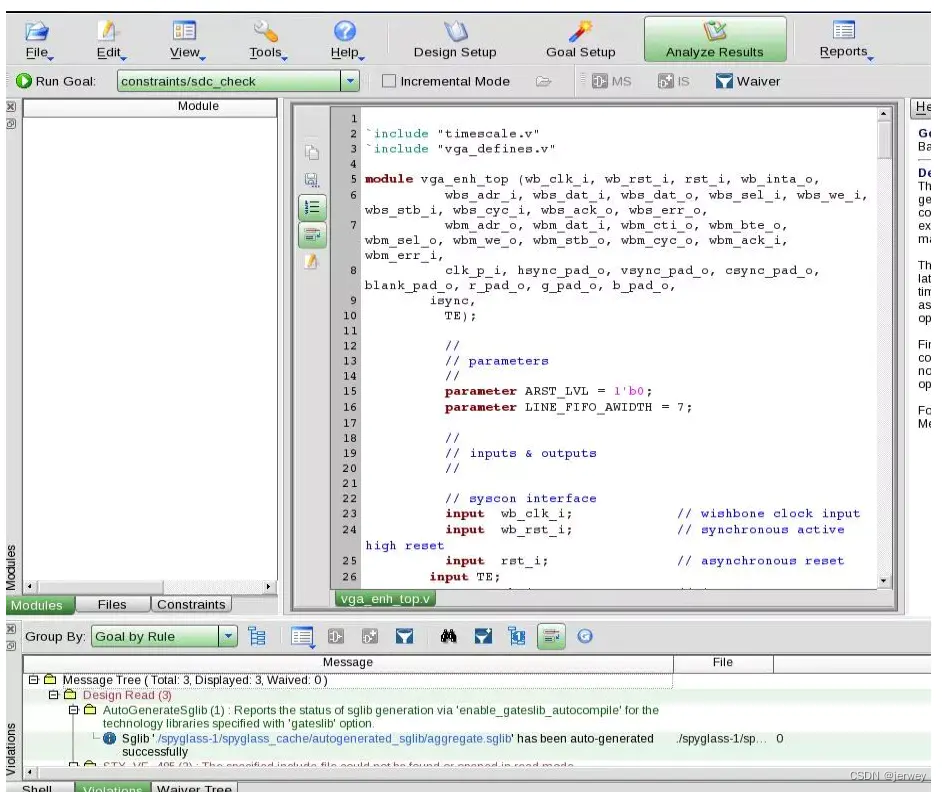

3. Analysis Result

最后,点击Analysis Results就能检查违例的情况

最后,关于CDC检查,这是一个工作量非常大的任务,建议先把顶层的基本约束写好,包括时钟,复位,input,output的时钟域。还有各种需要固定值的case analysis值也设好。一些不方便处理的模块,如IO mux,可以用black box处理assume_path。然后分析每一条报出来的Error,或者添加约束,或者waive。

batch模式

<

SpyGlass是一款功能强大的RTL分析工具,支持lint、CDC、LP、Constraint和DFT等功能。它通过规则、目标和子方法论进行分析,提供GUI和批处理两种模式。在GUI模式中,用户进行设计设置、目标设置和分析结果查看。批处理模式下,通过命令行选项运行目标。SpyGlass使用GuideWare参考方法学,并提供了丰富的TCL命令集进行设计阶段管理和分析。

SpyGlass是一款功能强大的RTL分析工具,支持lint、CDC、LP、Constraint和DFT等功能。它通过规则、目标和子方法论进行分析,提供GUI和批处理两种模式。在GUI模式中,用户进行设计设置、目标设置和分析结果查看。批处理模式下,通过命令行选项运行目标。SpyGlass使用GuideWare参考方法学,并提供了丰富的TCL命令集进行设计阶段管理和分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1725

1725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?