1.TLP中的tag是什么

在PCIe TLP(Transaction Layer Packet)中,tag是分配给特定Non-Posted Request的编号,协议要求CPL/CPLD中的tag 与对应non-post request TLP中的tag保持一致,因此Requester可以使用tag来识别CPL/CPLD是哪个请求对应的完成报文。

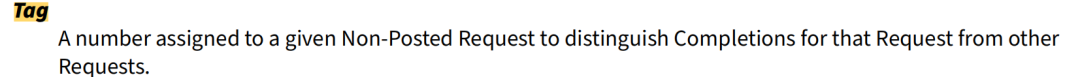

图1 memory请求头格式

如图1(PCIe 5.0协议图2-17和图2-18)所示,当时使用10-bit tag时,{T9,T8,Tag[7:0]}组成10-bit tag。

2.tag size 随着PCIe速率的变化

如果tag数量不足时,则function不允许发送Non-Posted Request,直到之前发起的Non-Posted Request对应的CPL/CPLD返回完成tag回收。

随着PCIe速率的提升,为了能够发挥最佳性能,tag size不断在增加,从8-bit tags、10-bit tags增加到14-bit tags。

| PCIe 版本 | 可使用的最大tag size |

| PCIe 1.0 | 8-bit tags |

| PCIe 2.0 | 8-bit tags |

| PCIe 3.0 | 8-bit tags |

| PCIe 4.0 | 10-bit tags |

| PCIe 5.0 | 10-bit tags |

| PCIe 6.0 | 14-bit tags |

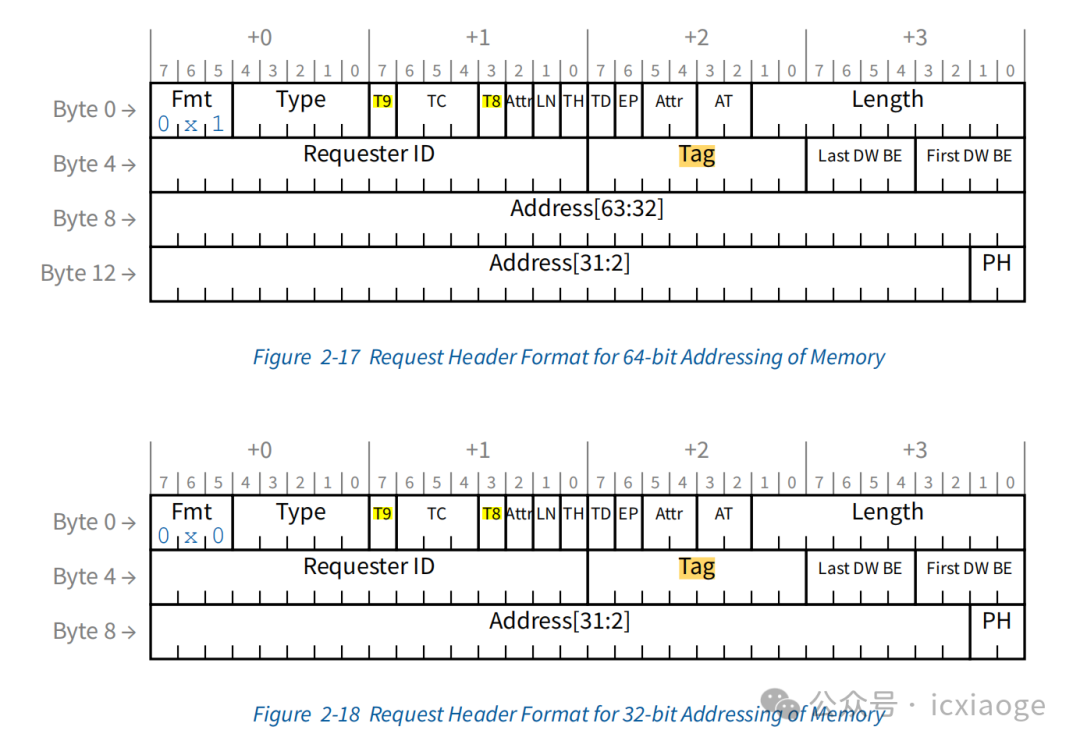

PCIe 6.0 速率提升到64GT/s,为了保证PCIe系统中实现最佳性能,设计人员需要不同round trip time (RTT)的场景下评估所需的outstanding non-posted requests (NPR)最大数量。round trip time (RTT)即往返时间,是PCIe设备从发起non-posted requests开始到接收到CPLD/CPL的时间间隔。随着RTT的增加,必须保证有足够的outstanding non-posted requests,否则数据路径将会存在空拍气泡,无法保证最佳性能。

图2描述了PCIe 4.0, 5.0 and 6.0 在不同round-trip times场景中所需要的tag数量。例如,在RTT为1000ns,16Lane的场景中,Gen4 所需要的tag数量大于10-bit tag limit(768),而在此场景中,Gen4所需要的tag数量大于3500。

可能有同学会说PCIe链路本身的延时并不大,远远不到1000ns,是的如果仅仅考虑PCIe 物理层、链路层、事务层的逻辑确实延时有限,在200ns以内。但是考虑到多级PCIe Switch转发延时,主机内部存储读取延时,MMC地址转换延时等等,平均RRT时间会明显大于200ns。

图2 Number of tags needed to achieve maximum throughput for PCIe 4.0 through PCIe 6.0 links

3.tag size的使用要求

对于tag size的使用,PCIe 6.0提出了明确的要求:

l所有的function必须支持8-Bit Tag Completer capability.

l支持16.0 GT/s及其以上速率的function必须支持10-Bit Tag Completer capability.

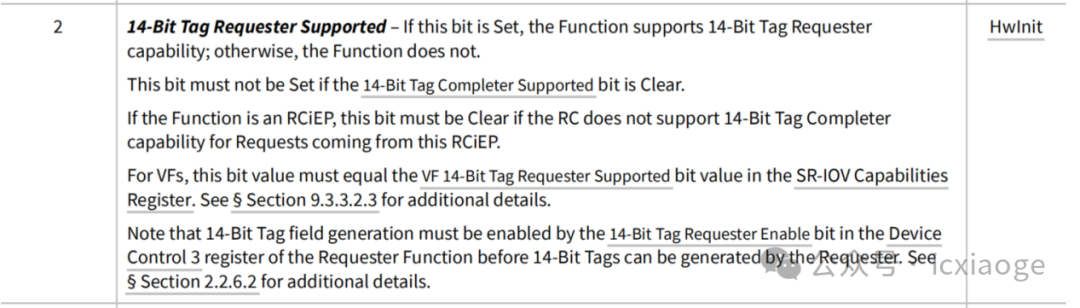

l支持14-Bit Tag Requester capability的前提是必须支持14-Bit Tag Completer capability.

l支持10-Bit Tag Requester capability的前提是必须支持10-Bit Tag Completer capability.

l14-Bit Tags,Tag[13:8]等于6’b0是不合法的数值,Tag[13:8]不等于6’b0是合法数值,即Requester不允许使用数值为0~255的tag。

l10-Bit Tags,Tag[9:8]等于2’b0是不合法的数值,Tag[9:8]不等于2’b0是合法数值,即Requester不允许使用数值为0~255的tag。

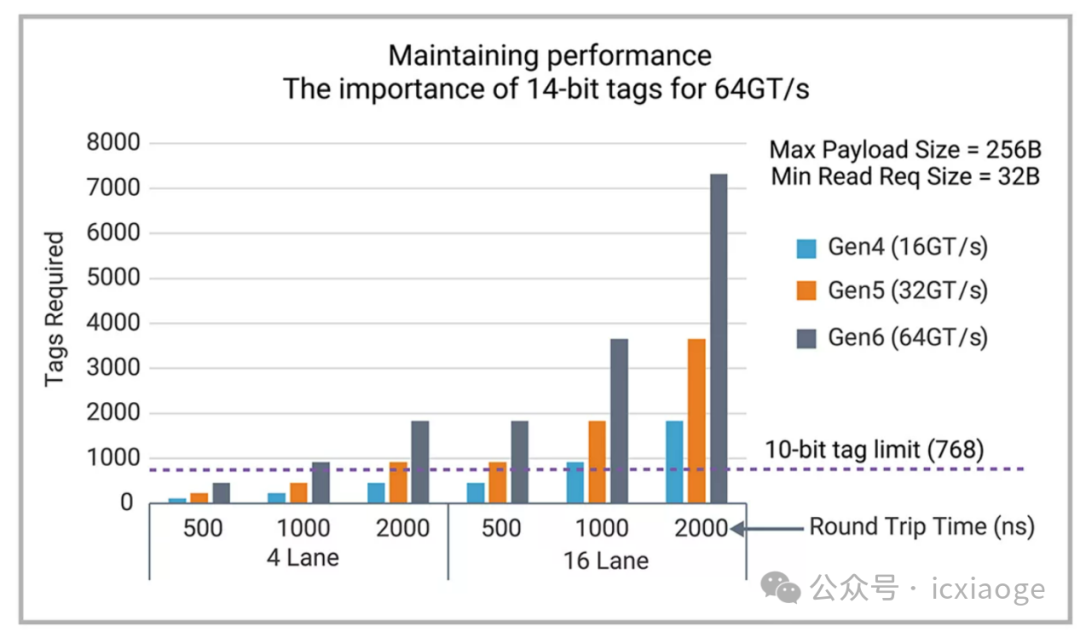

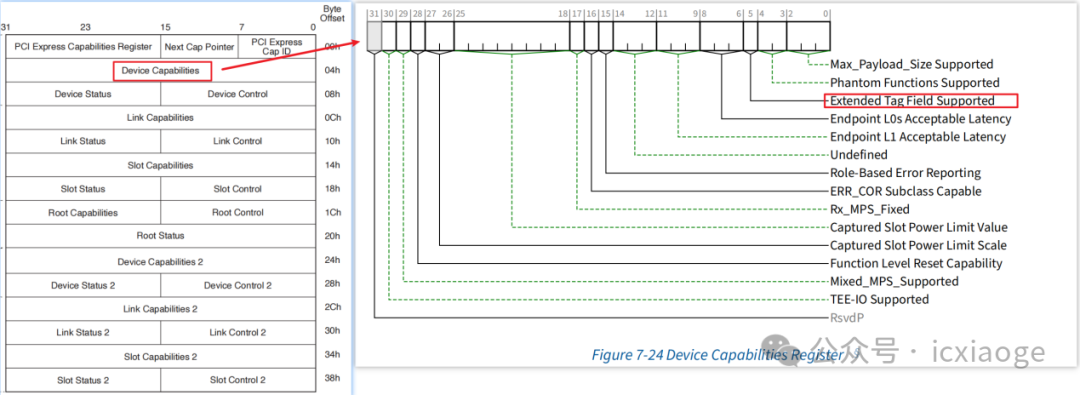

4.tag size相关的配置寄存器

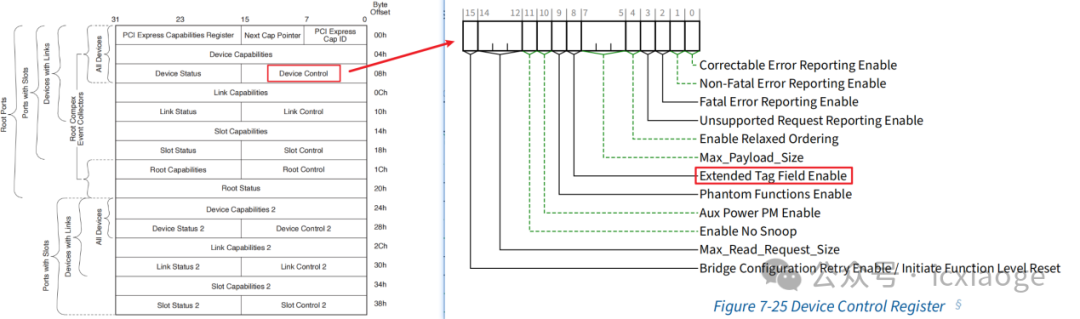

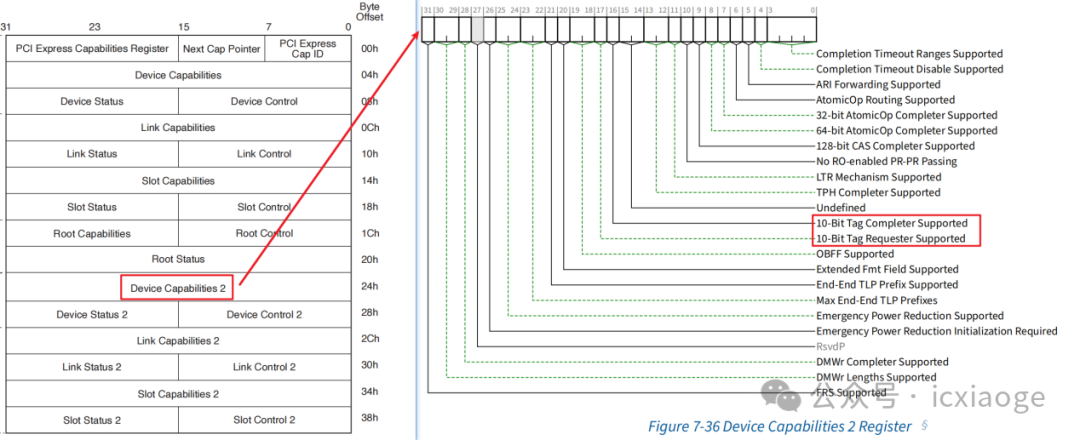

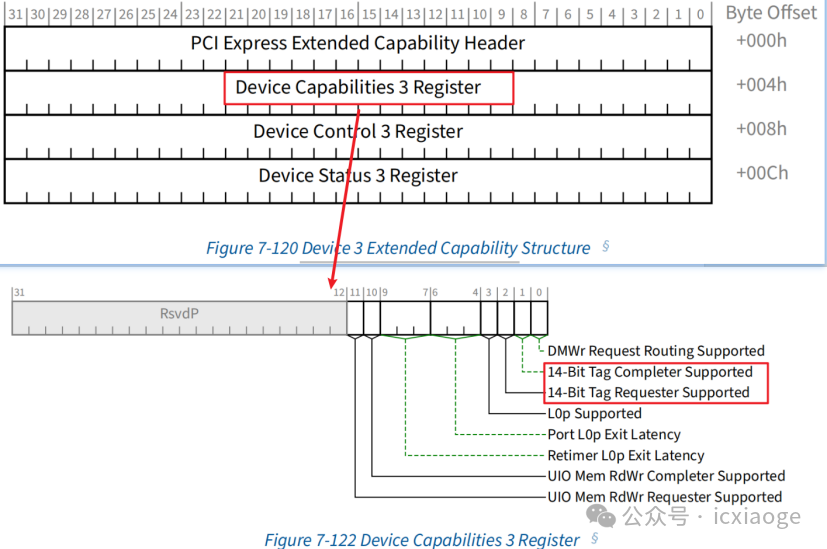

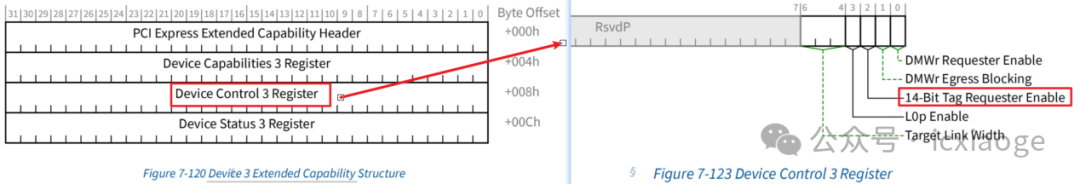

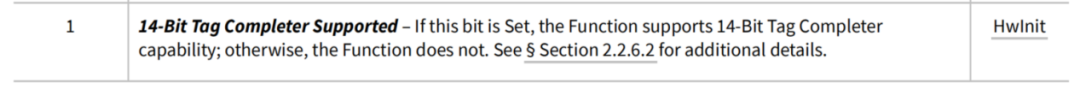

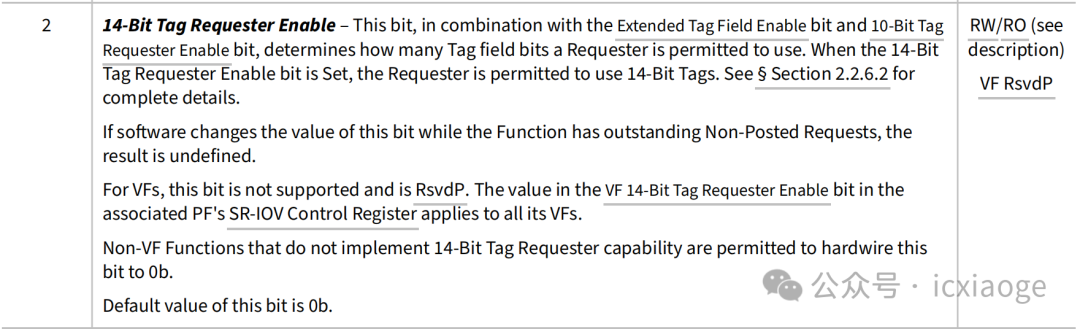

8-Bit Tags和10-Bit Tags相关的配置寄存器均在PCI Express Capability Structure中,而14-Bit Tags相关的配置寄存器均Device 3 Extended Capability Structure中。

相关字段详细描述见本章节截图(截图来自PCI Express® Base Specification Revision 6.2 )

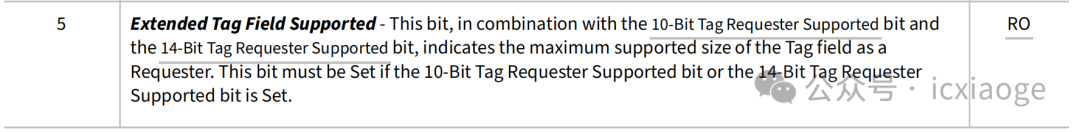

4.1.Extended Tag Field Supported

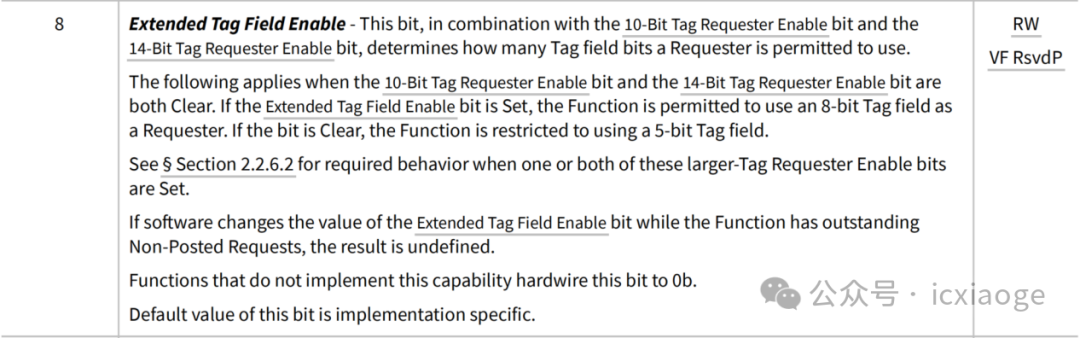

4.2.Extended Tag Field Enable

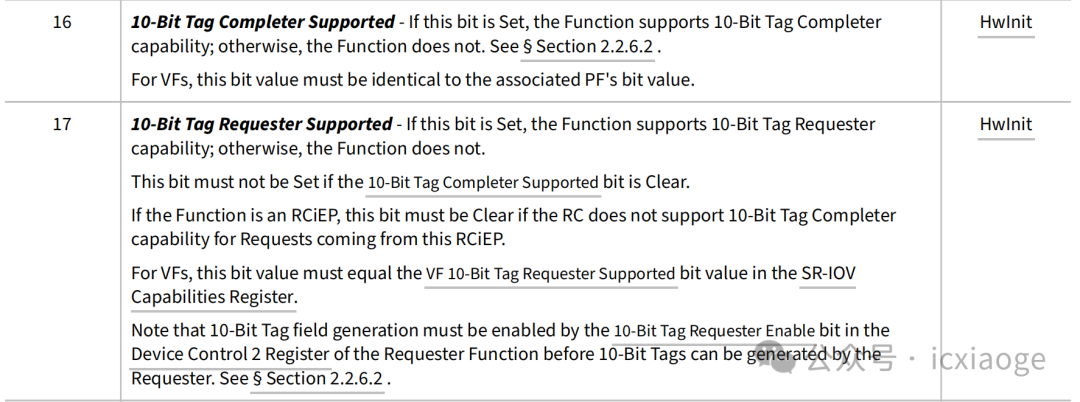

4.3.10-Bit Tag Completer Supported 与10-Bit Tag Requester Supported

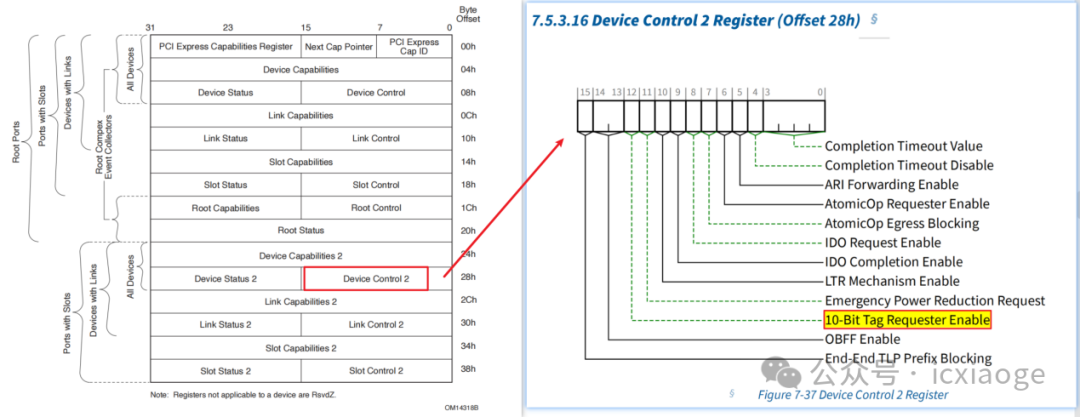

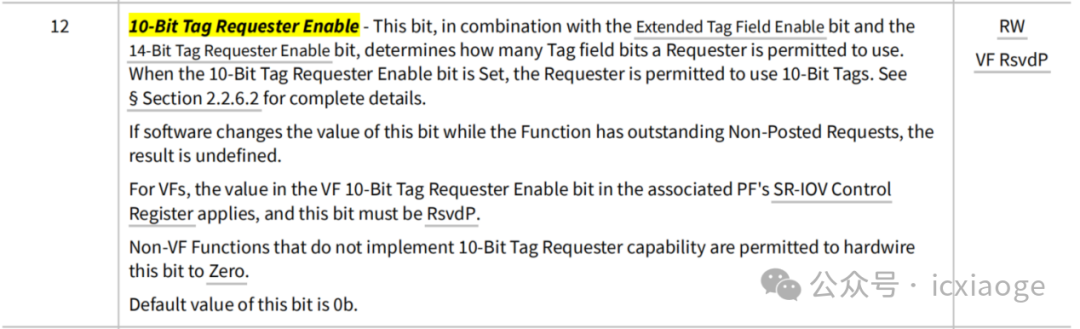

4.4.10-Bit Tag Requester Enable

4.5.14-Bit Tag Completer Supported 与14-Bit Tag Requester Supported

4.6.14-Bit Tag Requester Enable

5.不同tag size的组合

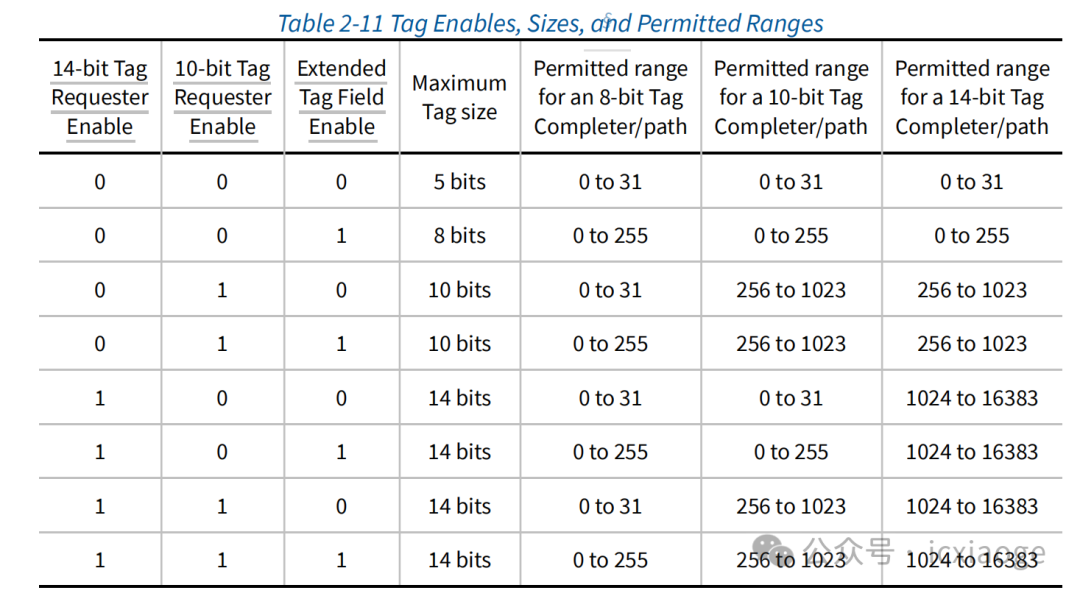

表2-11显示了三个标签使能位如何确定不同Completers和其相关路径的最大tag大小和允许的标签值范围。对于给定的tag使能设置组合,Requester必须使用在完成者和其相关路径的标签能力对应的允许范围内的标签值。

l当前14-bit Tag Requester Enable、10-bit Tag Requester Enable 、Extended Tag Field Enable分别为0、0、0时,最大tag size为5,此时Requester发送TLP时能使用的tag 范围为0~31

l当前14-bit Tag Requester Enable、10-bit Tag Requester Enable 、Extended Tag Field Enable分别为1、1、1时,最大tag size为14bits,如果使用8-bit Tag,则Requester发送TLP能使用的tag 范围为0~255,如果使用10-bit Tag,则Requester发送TLP能使用的tag 范围为256~1023,如果使用14-bit Tag,则Requester发送TLP能使用的tag 范围为1024~16383,

在表格2-11中可以看出,当存在多个Tag Requester Enable为1时,协议将tag范围进行了划分,其中0~255划分给了8-bit Tag,其中256~1023划分给了10-bit Tag,其中1024~16383划分给了14-bit Tag。此种设计的优点很明显,Requester发送memrd请求后收到CPLD时,能够根据CPLD的tag数值判断CPLD是否有效。例如Requester使用的是14-bit Tag,允许的tag 范围为1024~16383,协议要求Completer返回的CPLD中的tag与memrd中的tag保持一致,但是收到的CPLD数值小于1023,此时判断CPLD无效。

6.参考文档

PCIe 6.0 Designs at 64GT/s with IP | DesignWare IP | Synopsys

PCI Express® Base Specification Revision 6.2

2851

2851

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?