时钟门控(Clock Gating)是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

为什么需要时钟门控:大多数SoC都是power constrained,mobile端不能够充更多的电就只能尽可能地降低功耗了(无法开源只能节流呀),也因为时钟门控是降低芯片动态功耗最简单,最常用的方法之一。

时钟门控技术分类:通常,有两种不同的时钟门控实现技术。

combinational clock gating–这种类型的时钟门控由工具在综合时自动识别引入。

sequential clock gating –这种类型的时钟门控作为功能的一部分引入RTL设计中。通常时钟门控策略在系统架构中定义,然后由设计人员进行实现。

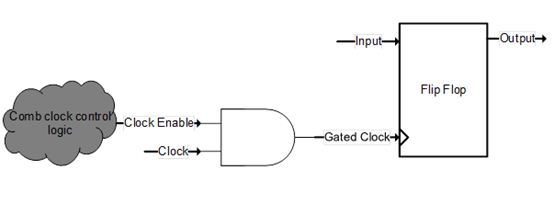

combinational clock gating

最简单的combinational clock gating可以通过AND门实现,如下图所示

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2442

2442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?