之前写过一篇对false_path和异步设置的区别的文章。而对于set_clock_groups中的logical_exclusive和physical_exclusive其实也很容易搞混,所以索性这里针对这四者一起论述一下。

这四者的共同点都是让工具对某些path不进行timing check。如果不考虑SI,其实四者的作用是相同的,也就是说他们的区别在于对于SI的计算方法的区别。

今天在网上找到一篇短文,解释的非常清楚。

原文:

physically_exclusive:

Means Timing paths between these clock domains are false, but only one clock can exist in the design at the same time. ETS/Tempus will filter out the SI interactions of nets/paths between these groups.

To phrase it differently, if the clocks are exclusive, then there should be no SI victim/aggressor interaction at all between nets clocked by physically excluded clocks.

asynchronous

If two clocks are asynchronous, it means that they don't have any phase relationship among them at all. So instead of using definite timing windows based on arrival times/skew etc, the tool will use infinite timing windows when calculating aggressors and victims, therefore you will see maximum SI impact.

logically_exclusive

Logically exclusive means the timing paths between these clock domains are false, but both clocks can exist in the design at the same time, so SI interactions between paths in these domains should still be considered. However crosstalk analysis will be done with regular timing windows based on arrival times/skew etc.

Assume that from your chip two data buses are going to UART module or USART. One of them will transmit, other will recieve. One is triggered by Tclk other by Rclk (same frequency say) Now, they can co-exist but if our design is not duplex (i.e only one of them can exist at a time) then we have to make sure that STA tool does not check for any violation between these two clocks. thats when we set logically_exclusive. Now, say it is duplex... the two clocks can co-exist and work on different paths.. so they might not be having any timing paths in common but during SI analysis it has to be taken into consideration since both of them could be switching at same time (same 0r opposite direction) and thus make an SI impact. So, it cannot be set as physically exclusive.

physically exclusive would be something like two clocks going into a mux and coming out. According to SEL only one of them can exist and thus SI computation on both would be overtly pessimistic.

我这里按照我的理解总结一下:

以两个clock为例,如果他们设在同一个点,那么就是physical exclusive,因为物理上不能共存。如果是设在两个点,就可能是异步或者logical_exlusive。logical exclusive等同于false path,因为对于si的timing window计算方法相同,都是按照同步进行计算。而async则是按照异步进行timing window的计算

从si的角度,async最严格,logical exlusive和false path第二。physical exclusive排在第三。

欢迎大家留言讨论。

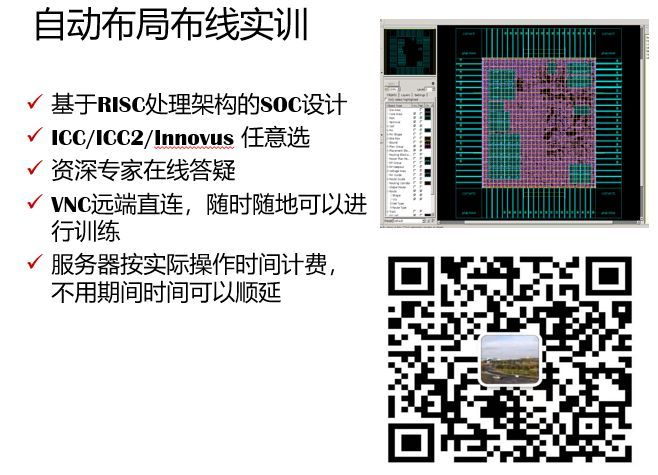

与我联系,拉我入群:

本文总结了physical_exclusive, logical_exclusive, asynchronous 和 false_path 在时序分析中的区别,特别是它们在信号完整性和SI计算方法上的差异。physical_exclusive指路径在物理上不能共存,asynchronous表示无相位关系,logical_exclusive允许路径共存但考虑SI交互,false_path则不进行时序检查。在SI严格性上,async最高,其次是logical_exclusive和false_path,physical_exclusive相对宽松。"

102474443,8506735,Java泛型详解:参数化类型与类型擦除,"['Java', '泛型', '类型安全', '编程概念']

本文总结了physical_exclusive, logical_exclusive, asynchronous 和 false_path 在时序分析中的区别,特别是它们在信号完整性和SI计算方法上的差异。physical_exclusive指路径在物理上不能共存,asynchronous表示无相位关系,logical_exclusive允许路径共存但考虑SI交互,false_path则不进行时序检查。在SI严格性上,async最高,其次是logical_exclusive和false_path,physical_exclusive相对宽松。"

102474443,8506735,Java泛型详解:参数化类型与类型擦除,"['Java', '泛型', '类型安全', '编程概念']

400

400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?