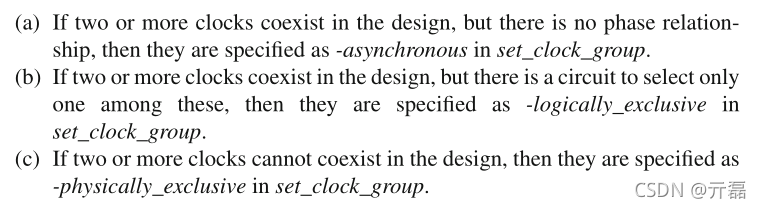

1.asynchronous代表两个异步的clock group,工具会做正常的SI分析。logically_exclusive代表两个clock group在逻辑上相互排斥,比如两个clock经过MUX选择器。

Logically Exclusive Clocks

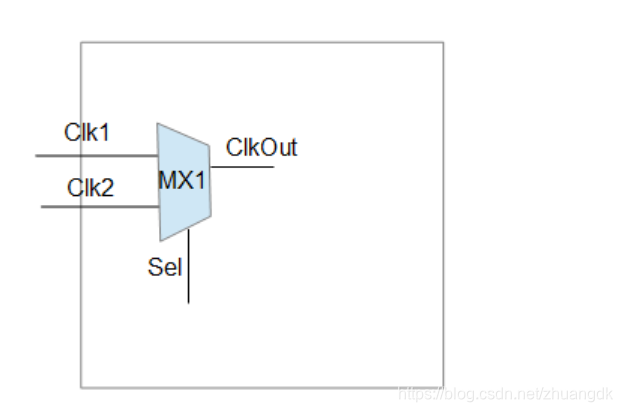

如果两个时钟同时存在但是他们之间没有任何 path,则这两个时钟可以设置为 logically exclusive,典型的情况就是一个 MUX 选择两个或多个时钟。

案例1

时钟 clkOut 通过Mux MX 的 Sel 进行选择,因此 Clk1 和 Clk2 在 MX1 的下游路径上不会逻辑上同时存在。它们在离开 MUX 之后不会相互作用。

set_clock_groups -logically_exclusive -group [get_clocks Clk1] -group [get_clocks Clk2]

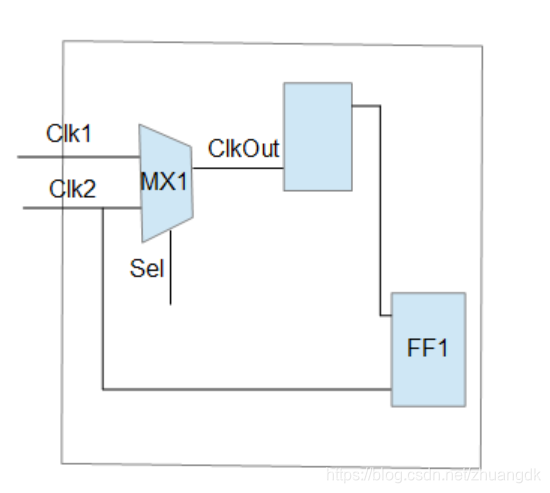

案例2

假如在 MUX 之外存在 Clk2 驱动的 flops,并且与 ClkOut 时钟驱动的 flops 相互作用,这时就不能设置 Clk1 和 Clk2 logically exclusive。

此时必须在 MX1 的 output 处创建 generated 时钟,创建的时钟可以设置为逻辑互斥关系。

create_generated_clk -name genClk1 -source MX1/Y -master Clk1

create_generated_clk -name genClk2 -source MX1/Y -master Clk2

set_clock_groups -logically_exclusive -group [get_clocks genClk1] -group [genClk2]

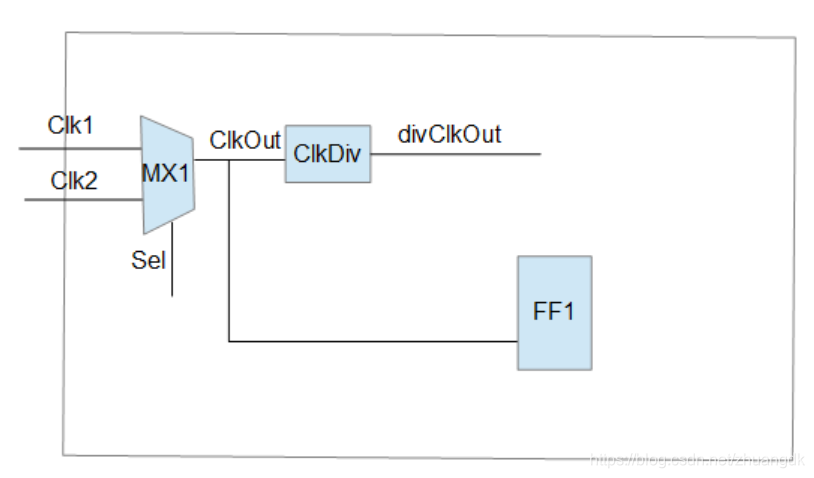

案例3

在 MX1 的输出有一个分频器,这种情况下需要创建两个 generated 时钟分别以 Clk1 和 Clk2 作为 master 时钟。

create_generated_clk -name genDivClk1 -source ClkDiv/Y -master Clk1

create_generated_clk -name genDivClk2 -source ClkDiv/Y -master Clk2

set_clock_groups -logically_exclusive -group [get_clocks {Clk1 genDivClk1}] -group [get_clocks {Clk2 genDivClk2}]

Physically Exclusive Clocks

当两个时钟在同一时刻不可能同时存在时,则这两个时钟就可以设置为 physical exclusive。比如在相同的 primary 端口上创建多个时钟,但是

这两个时钟工作在不同的工作模式,比如TestClk 和 Function Clock。SI 相互作用不会发生在这两个时钟之间。

set_clock_groups -physically_exclusive -group [get_clocks TestClk] -group [get_clocks SysClk]

工具分析SI时,采用 infinite window(信号全部翻转),而不是看具体的timing window,较为悲观。physically_exclusive代表两个clock group在物理意义上相互排斥,比如在一个source pin上定义了两个时钟。这时候,工具会禁止分析SI。

2.当 set_clock_groups 命令中多个 groups 被指定时,同一个时钟不能出现在不同的 group 中,但是可以存在于多次 set_clock_groups 命令使用。

例如 set_clock_groups -asynchronous -group {ClkA ClkB} -group {ClkC} -group { ClkA ClkD},其中ClkA 存在于两个group中是不允许的。但是 set_clock_groups -asynchronous -group {ClkA ClkB} -group {ClkC} set_clock_groups -asynchronous -group {ClkA} -group {ClkD}

上面两个连续声明是合法的。

参考资料链接:(32条消息) 静态时序分析—set_clock_groups_拾陆楼的博客-优快云博客

原文链接:https://blog.youkuaiyun.com/Tao_ZT/article/details/102456839

487

487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?