1.kmap1

module top_module(

input a,

input b,

input c,

output out );

assign out=(a&(~c))|c|(b&(~c));

endmodule2.kmap2

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out=(~a&(~d))|(a&(~b)&(~c)&(~d))|(a&(~b)&c&d)|(b&c&d)|((~b)&(~c)&d);

endmodule3.kmap3

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out=(c&(~b))|(a&b&c)|(a&(~c));

endmodule

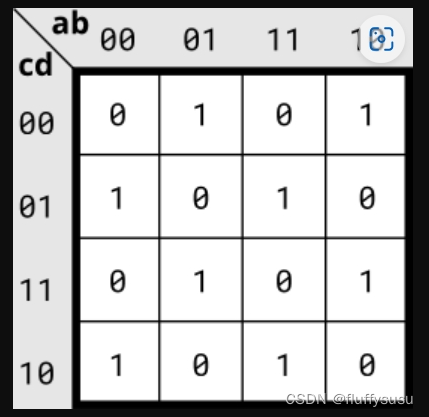

4.kmap4

(记住对应的图和表达式)

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = a^b^c^d;

endmodule5.Exams/ece241 2013 q2

SOP形式是找出所有当输出为1(最小项)的输入组合(乘积和)

POS则是找出所有当输出为0(最大项)的输入组合(和乘积)烙铁 我不会写pos啊

该电路的SOP和POS必须均为化简后的最小值

module top_module (

input a,

input b,

input c,

input d,

output out_sop,

output out_pos

);

assign out_sop = (c & d) | (~a & ~b & c);

assign out_pos = (~a & ~b & c) | (b & c & d) | (a & c & d);

endmodule6.Exams/m2014 q3

module top_module (

input [4:1] x,

output f );

assign f=((~x[1])&x[3])|(x[2]&x[4]&(~x[3]));

endmodule7.Exams/2012 q1g

module top_module (

input [4:1] x,

output f

);

assign f=((~x[1])&x[3])|((~x[4])&(~x[2]))|(x[1]&x[2]&x[3]&x[4]);

endmodule8.Exams/ece241 2014 q3

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in[0]=((~c)&d)|(c&d)|(c&(~d));

assign mux_in[1]=0;

assign mux_in[2]=((~c)&(~d))|(c&(~d));

assign mux_in[3]=c&d;

endmodule

文章详细描述了多个逻辑设计模块,包括KMaps(查找表)如kmap1至kmap4,以及SOP(SumofProducts,和项之和)和POS(ProductofSums,积项之积)转换的实例。这些模块展示了基本的逻辑运算和组合逻辑设计方法。

文章详细描述了多个逻辑设计模块,包括KMaps(查找表)如kmap1至kmap4,以及SOP(SumofProducts,和项之和)和POS(ProductofSums,积项之积)转换的实例。这些模块展示了基本的逻辑运算和组合逻辑设计方法。

7572

7572

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?