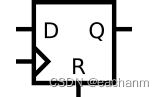

Implement the following circuit:

同步复位

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always@ (posedge clk)

if(r == 1)

q <= 1'b0;

else

q <= d;

endmodule

该文章描述了一个基于同步复位的电路模块设计,模块名为top_module,包括时钟输入clk、数据输入d和同步复位输入r。在时钟的上升沿,如果复位信号r为1,则输出q被复位为0;否则,输出q跟随输入d的值变化。

该文章描述了一个基于同步复位的电路模块设计,模块名为top_module,包括时钟输入clk、数据输入d和同步复位输入r。在时钟的上升沿,如果复位信号r为1,则输出q被复位为0;否则,输出q跟随输入d的值变化。

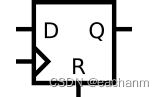

Implement the following circuit:

同步复位

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always@ (posedge clk)

if(r == 1)

q <= 1'b0;

else

q <= d;

endmodule

242

242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?