FPGA芯片电路搭建

一、Xilinx7系列介绍

1、总体介绍:

Xilinx®7系列FPGA包括四个系(Spartan®,Artix®-7,Kintex®-7,Virtex®-7),能够满足系统全部范围的要求,价格低廉,尺寸小,对成本敏感,超高端的连接带宽,逻辑容量及信号处理能力的大量应用,满足了系统对高性能的要求。7系列的FPGA包括:

Spartan®-7系列:价格低廉,供电电源低,I/O性能高。可提供低成本,非常小的外形尺寸封装,以实现最小的PCB占地面积。

Artix®-7系列:针对需要串行收发器以及高DSP和逻辑吞吐量的低功耗应用进行了优化。为高吞吐量、成本敏感型应用提供最低的总物料成本。

Kintex®-7系列:针对最佳性价比进行了优化,与上一代产品相比提高了两倍,支持新一代的FPGA。

Virtex®-7系列:针对最高系统性能和容量进行了优化,系统性能提高了两倍。通过硅堆叠技术(SSI)实现的最高性能器件。

7系列FPGA采用最先进的高性能、低功耗(HPL)、28nm、高k金属栅(HKMG)工艺技术,I/O带宽为2.9TB/s,逻辑单元容量为200万个,DSP定点运算性能为5.3TMAC/s,[其中Virtex-7系列的DSP处理能力为5,335 GMAC/s(GMAC/s:每秒10亿次乘加运算)],实现了无与伦比的性能提升,同时功耗比前一代器件低50%,为ASSP(Application Specific Standard Parts 专用标准产品)和ASIC提供了完全可编程的替代方案。

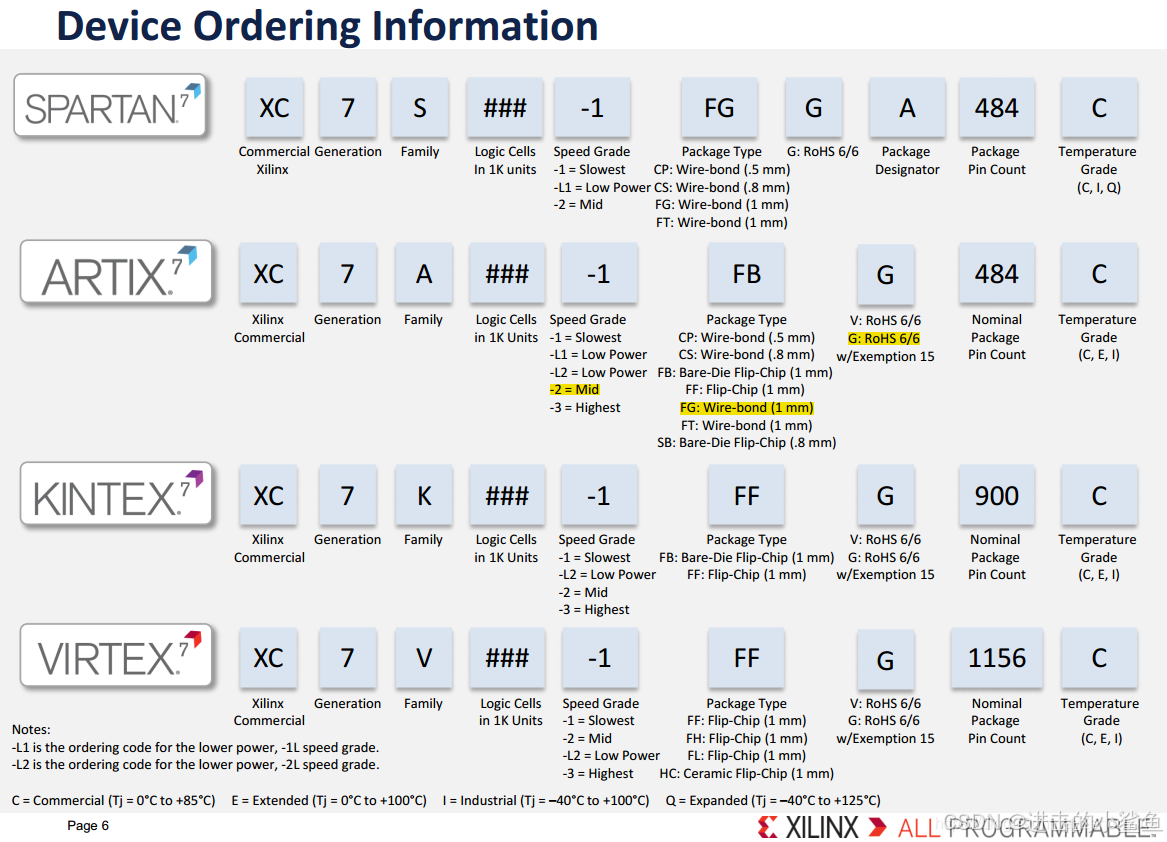

2、命名规则

如XCVU13P-2FHGB2104芯片中,XC代表Xilinx Commercial; VU代表Virtex Ultarscale系列;13代表逻辑资源数,这个数*1000就是这款芯片的大致逻辑资源;-2代表速度等级,数字越大,等级越高,带L代表是低功耗器件;FH代表封装形式;2104代表引脚数。

二、IO的命名

1、物理命名

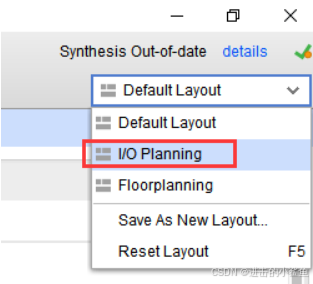

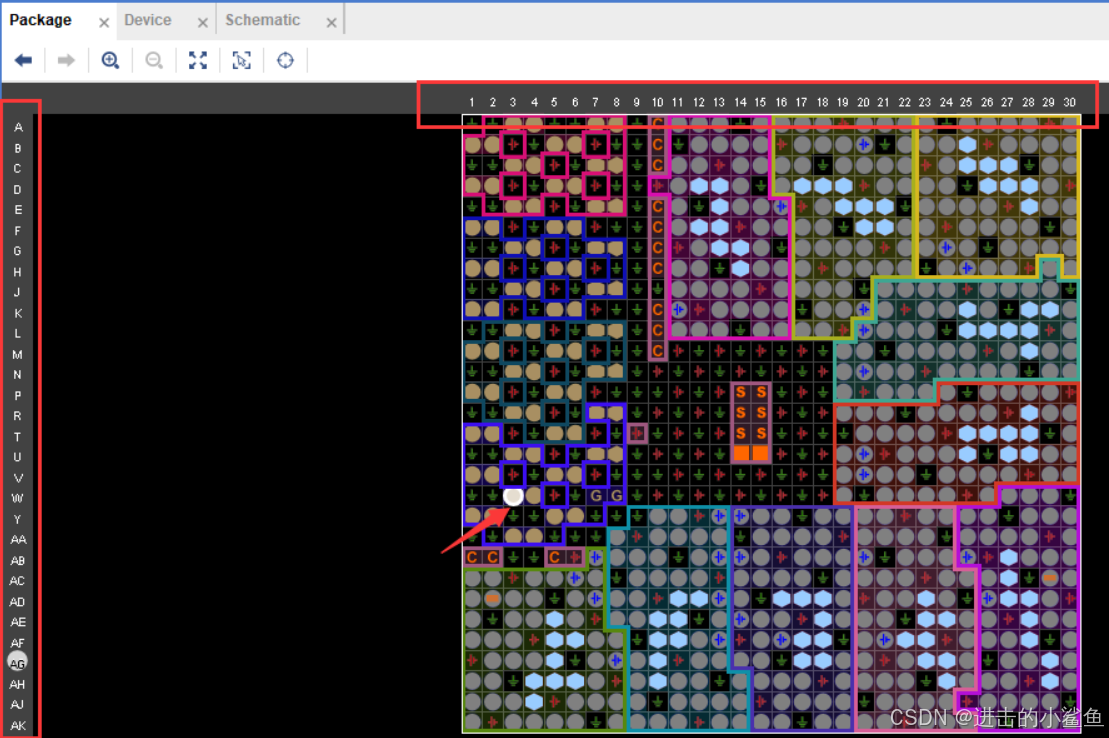

FPGA的IO物理命名规则,也就是我们做管脚约束时候的命名。芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式,从上到下是字母(A,B,C,D…),从左到右是数字(1,2,3…),所以诸如:W3(见下图,在Vivado中右上角选择l/O Planning即可调出封装图),就是图上箭头的位置

2、功能命名

FPGA的功能命名规则。功能命名规则每个厂家都会自己的一套规则,但都大同小异,我们重点来讲述一下xilinx的命名。

Xilinx 7系列FPGA的HR和HP bank,每个bank有50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个bank的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。在差分信号的实现过程中,管脚分配应选择相应电平标准的bank中除首尾以外的其他48个IO。Xilinx 7系列的差分信号的实现主要通过IBUFDS、OBUFDS、IOBUFDS等原语的调用,在程序中直接进行原语的例化。

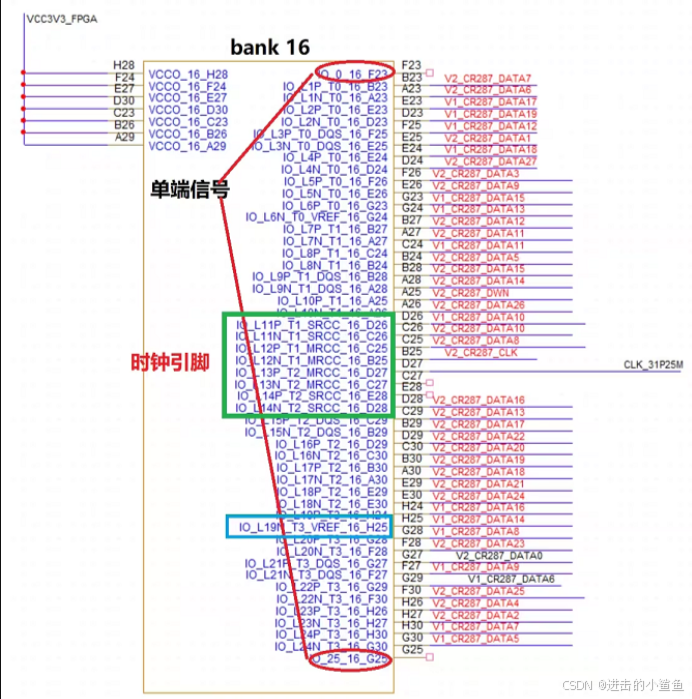

通常xilinx 的功能命名格式为:

差分IO命名:IO_LXXXP_XXXX_#。其中:

(1) IO代表用户IO;

(2) L代表差分,XX代表在当前Bank下的唯一标识号,差分对编号不同的差分对具有不同的编号,P或N表示LVDS信号的差分正端或差分负端;

(3)XXXX位置表示该IO的一些功能;

(4) #表示Bank号,由于FPGA的IO参考电平是按照Bank进行供电的,所以差分对所在的Bank应尤其注意。

举例:IO_L13P_T2_MRCC_12,那通过功能命名的规则我们就可以知道,这是一个用户IO,支持差分信号,是Bank12的第13对差分的P端口,与此同时它也是全局时钟网络输入管脚(MRCC是全局时钟网络)。

单端IO命名:IO_#_#。其中:第1个#代表单端IO的编号;第2个#代表单端IO所在的Bank。

举例:IO_25_12,代表第25个单端IO,IO位于第12BANK。

三、Bank介绍

1、总体介绍

为了便于管理和适应多种电器标准,FPGA 的 IO 部分被划分为若干个组(Bank),Bank是一组物理位置和特性相近的IO的总称, 每个 Bank 的接口标准由其接口电压 VCCIO 决定,一个 Bank 只能有一种 VCCIO,但不同 Bank 的 VCCIO 可以不同。只有相同电气标准和物理特性的端口才能连接在一起,VCCIO 电压相同是接口标准的基本条件。同一Bank的电压的基准是一致的,因此,通常如果我们需要各种不同标准的电压,可以通过给到Bank的电压基准不同的方式来实现多种电平标准的输入输出。通常封装越大,Bank数量也越多,可以支持电压标准也越多。

HP Bank、HR Bank和HD Bank, 这几个概念都是在7系列之后才有的,其中7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Bank和HD Bank,但并不是一个FPGA中会同时包含HP/HR/HD Bank。

| Bank | 说明 |

|---|---|

| HP | High Performance 应用于高性能也就是速度比较高的场景,比如DDR或者其它高速差分总线(不是gtx),由于速率比较高,Bank电压最高也只能到1.8V。 |

| HR | High Range 表示支持wider range of I/O standards,最高能够支持到3.3V的电压。 |

| HD | High Density 应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V。 |

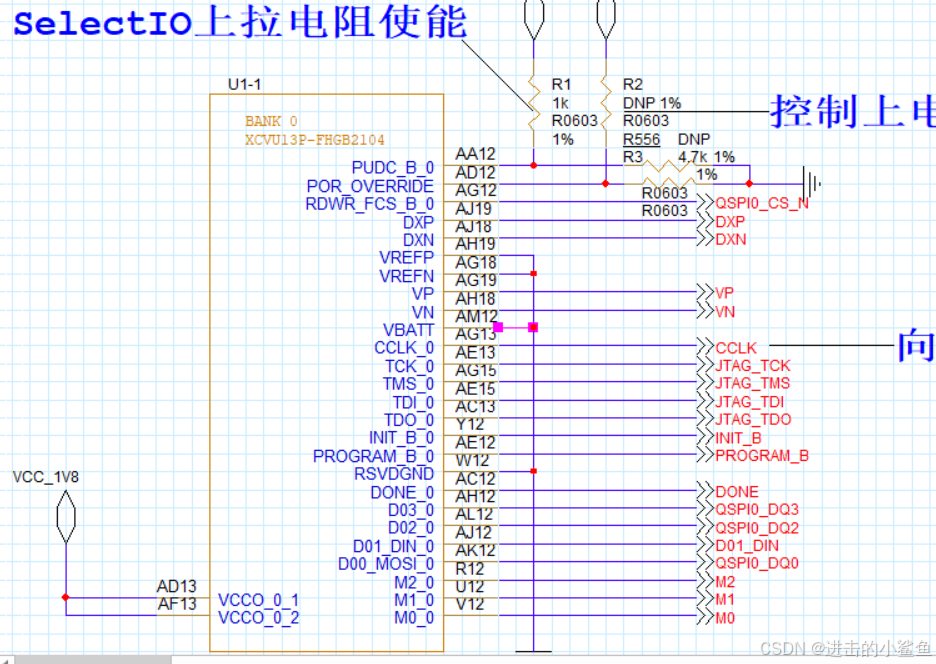

2、Bank0

BANK0是配置BANK

VCCO_0

BANK0中所有IO所遵循的电平标准,可连接3V3/2V5/1V8/1V5等电压。

POR_OVERRIDE

引脚(Power-On Reset Override)在FPGA上的功能,是用来让用户能够让FPGA在上电复位后继续保持在复位状态,而不是让设备立即开始运行。换句话说,当POR_OVERRIDE引脚被激活(通常是高电平)时,FPGA的Power-On Reset(POR)将被阻止或者说被覆盖,FPGA不会开始运行,直至该引脚被去激活(通常是低电平)。

一般来说,POR_OVERRIDE引脚在FPGA设计中的主要应用场景有:

在一些需要精确控制FPGA上电启动时间的系统设计中,比如与其他硬件配合启动的场景。

系统需要在FPGA初始化完成之前完成一些操作,比如配置某些外部设备等。

在系统调试阶段,有时也会使用POR_OVERRIDE引脚来帮助分析和定位问题。

PUDC_B

引脚(Pull-up During Configuration)在FPGA上的功能是控制配置过程中对未使用的I/O引脚的处理。

在许多FPGA中,可以通过设置PUDC_B引脚的状态,决定在配置过程中,FPGA对未使用的I/O引脚是设置为上拉电阻还是让其为三态(浮动状态)。

如果PUDC_B引脚被配置为高电平(通常是接 VCC),那么在配置过程中,未使用的I/O引脚将被连接到内部的上拉电阻中。如果PUDC_B引脚被配置为低电平(通常是接地GND,也是默认情况),那么未使用的I/O引脚将被配置为三态。

此功能一般在系统设计时,基于对电源消耗、噪声影响等因素的考虑进行配置。例如,一般来说,将未使用的I/O引脚设置为上拉可以避免引脚由于浮动而引起的噪声。而在有限的电源条件下,可能会选择让未使用的I/O引脚保持三态以节省功耗。

CFGBVS引脚

bank0电压范围选择引脚,该引脚用于确定bank0的供电电源的范围。

如果该引脚接VCC,则bank0使用2.5V或者3.3V供电。

如果接GND,则bank0供电电压小于等于1.8V。

PROGRAM_B引脚

低电平有效,复位配置整个器件。在下降沿时配置复位初始化,上升沿时配置时序开始启动。开始于下降沿,上升沿开始配置,上电会先检测电平。

平时连接一个外部≤4.7KΩ的电阻到VCC_0确保稳定的高电平输入。

这个引脚可以清除FPGA内部的所有配置信息,让FPGA回到配置状态,重新进行配置,延迟配置的时间需要使用INIT_B信号配合完成。

INIT_B

初始化引脚或配置错误信号,低电平有效。

当 FPGA 处于配置复位状态或当 FPGA 正在初始化(清除)其配置存储器(PROGRAM_B信号为低电平)时或当 FPGA 检测到配置错误时,FPGA 会将该引脚驱动为低电平。

在上电期间,可以通过该引脚拉低,来延迟上电配置程序的时间。

当完成初始化后,该引脚被释放,外部上拉电阻将该引脚拉高,当检测到该信号上升沿之后,FPGA会读取M[2:0]引脚状态,从而确定后续采用哪种配置方式进行配置。

该引脚外部也需要通过4.7KΩ的电阻上拉到VCC。

DONE

配置完成信号。该信号高电平表示FPGA配置序列完成, 默认情况下,该引脚为开漏输出,内部有一个大约10KΩ的上拉电阻。

外部需要通过一个330Ω的电阻上拉即可。

VCCBATT

该引脚是FPGA内部易失性存储器RAM的电池备用电源,用于存储AES解密器的密钥,如果不需要使用AES易失性密钥存储区域中的解密器密钥,那么将该引脚接地就行,该引脚不是I/O,不受VCCO_0的影响。

一般都用作接地处理。或者VCCAUX。

M 2:0

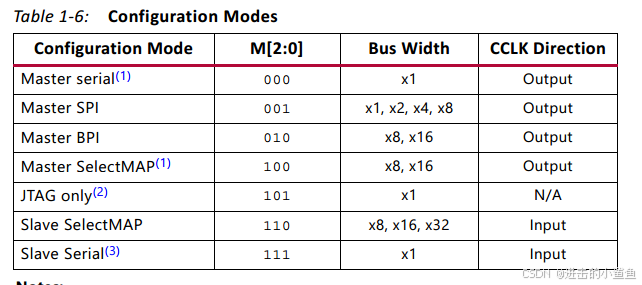

模式配置管脚,配置方式见配置设计那一章。主SPI对应001,主BPI对应010,JTAG对应101。决定了FPGA的启动模式。

这些引脚可以直接接到VCC或GND,也可以通过一个≤1KΩ的电阻连接到VCC或GND。

CCLK(configuration clock_输入/输出)

配置时钟。

在主模式下,configuration clock由FPGA提供,CCLK是输出时钟;

在从模式下,CCLK是输入需要连接到外部时钟源;

在JTAG模式下,CCLK是高阻状态可以悬空不连接。

主BPI模式下不使用,可以悬空;

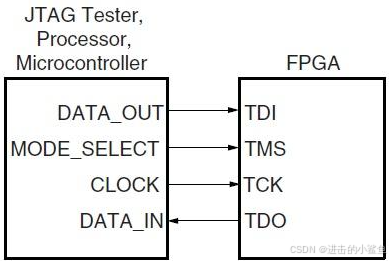

TMS、TCK、TDI、TDO: JTAG下载管脚

其中TMS、TCK需要在输入处连接一个弱上拉电阻10KΩ。

TCK_0:测试时钟输入,

TMS_0:测试模式输入,

TDO_0:测试数据输出,

TDI_0:测试数据输入,

下面这些管脚都属于XADC模块

1、VCCADC_0

XADC 中ADC 和其他模拟电路的模拟电源引脚,电压和VCCAUX保持一致。建议单独供电或通过滤波电路(电感等)连到VCCAUX上,以保证尽量减少信号的干扰,从而影响采集的精度,不使用时也需要接VCCAUX。

2、GNDADC_0

XADC的模拟接地引脚,应该通过磁珠连接到系统GND。在一个混合信号系统中,如果可能的话,此引脚应该连到在一个模拟的接地平面上,在这种情况下就可以不需要铁氧体磁珠。即使XADC 不用,也应始终将此引脚连接到GND。

3、VP_0/VN_0

XADC专用差分输入引脚,专用是对比其他XADC模拟输入来说,该引脚不能用作普通IO,其他的都可以,不使用时接GND; 获得高共模抑制比。

4、VREFP_0

电压基准,此引脚可连接到外部1.25V,以获得ADC 的最佳性能。

5、VREFN_0

电压基准GND,该引脚应与外部1.25V的地引脚相连,以获得最佳的ADC 性能。与VREFP 信号一起提供差分1.25V 电压。即使没有提供外部参考,此引脚也应始终连接到GNDADC。

6、DXP_0/DXN_0

DXP、DXN 为内部热敏二极管温度传感器引脚,在BANK0热二极管被允许接入使用DXP和DXN引脚,结合外部温度监控电路可实现对FPGA芯片温度的监控,不用时接系统GND。

电路图举例:

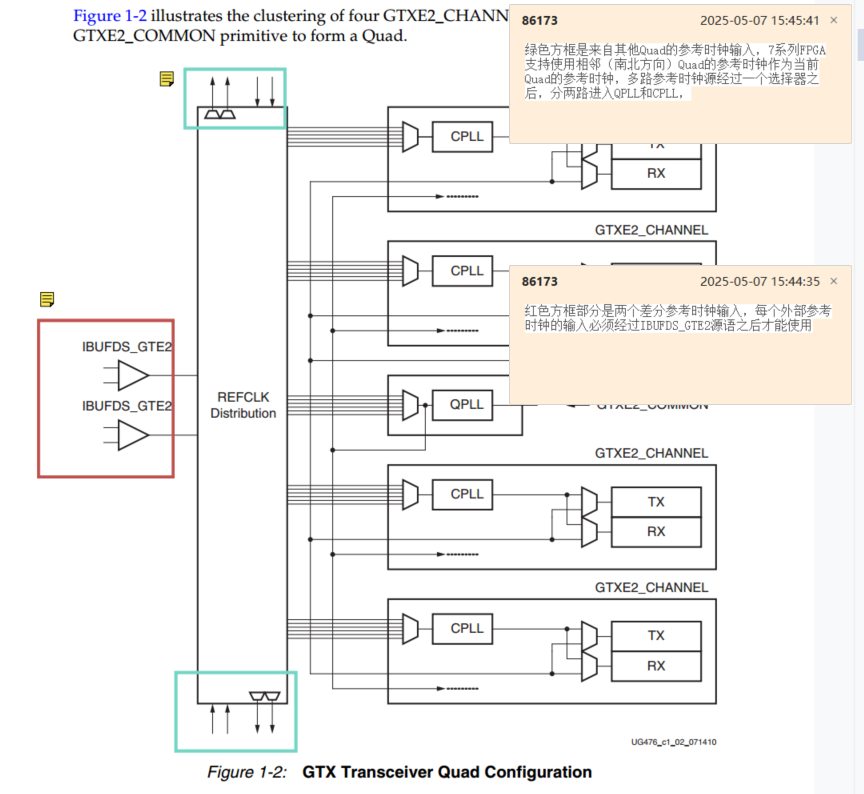

3、GTX、GTH

UG476

一个GTXbank构成如下:

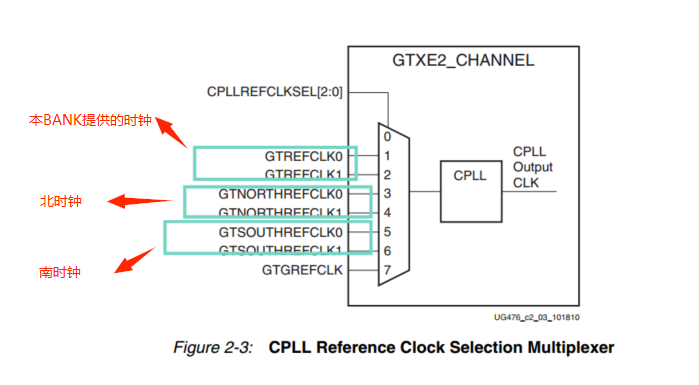

每个CHANNEL可以选择本时钟和南北时钟。当然每个CHANNEL里面的RX和TX时钟必须一样。

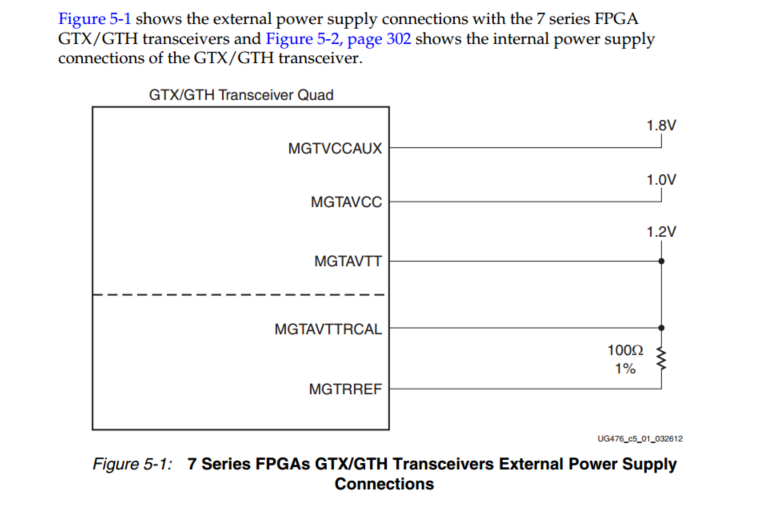

7系列GTX和GTH外部电源连接

4、普通BANK

Vref引脚

当该BANK的IO引脚速率比较高,比如DDR4,使用外部参考电压Vref=1/2VCCO。

Vref引脚没上拉到1/2VCCO,使用的是内部参考。

VRN、VRP

四、画原理图步骤

1、官方文档

xilinx的官方文档算是不错的资料,只要有耐心,收获是斐然的。

以下是关于FPGA片上资源的相关文档。【ug4*】开头是7系列的,【ug5*】开头是UltraScale系列的,两者文章都很有不少相似性。

01、ug470/ug570

如何控制FLASH来实现在线升级?如何实现动态重加载?看完这个文档就有答案了,而且也介绍了程序烧写的几种方案,FPGA启动的几个步骤,烧写文件的组成格式等等,有没有感觉能收获不少。

02、ug471/571

这是硬件工程师和逻辑工程师都值得看的一篇文档,介绍了不同系列FPGA支持的电平标准。如何对引脚做约束,该选用哪个BUFIO,看完第一章自然就知道了。而且不止如此,像ISERDES、OSERDES如何使用、如何配置都有详细的介绍。普通的IO也可以实现1.25Gbps的通信速率,怎么实现,这篇文章就是基础。

03、ug472/ug572

这篇是关于FPGA时钟架构的介绍。就拿7系列来说,BUFG、BUFH是如何分布的?时钟架构是如何搭建的?时钟BUF该如何使用?都有介绍,此外还有MMCM、PLL的结构、原语使用的介绍。看完此文可以直接拿原语来实现IP核的功能了,这可不少炫技,蛮有用得。

04、UG473/ug573

这篇是关于片上资源的介绍,主要介绍了BRAM、FIFO,还有UltraScale系列的URAM是如何分布,结构是怎样的,我们该如何使用,这也是蛮有用的。例如在解决BRAM读写冲突时的模式设置,以及不同位宽、深度对BRAM资源的评估。

05、ug474/ug574

这篇是关于 SLICEM以及其中的LUT、FF的介绍,也就带我们了解CLB的组成和使用,很多文章关于资源介绍也是来源于此。

06、ug475/ug575

这篇是关于引脚属性引脚分布的介绍,说实话我没咋看,感觉用处不大。

07、ug476,ug478,ug482、ug576,ug578

这篇强烈推荐大家看一看了,是关于高速接口的介绍,包括时钟结构、复位逻辑,收发器的PMA、PCS层所包含的内容等。很多时候我们例化个IP就能使用了,但如果想深入的了解,这篇文章必读。

其中ug482介绍GTP,ug476介绍GTX和GTH,ug478介绍GTZ,ug576介绍UltraScale系列的GTH,ug578介绍GTY,看似挺多,都大差不大。

08、ug477

PCIE是由两个硬核组成,一个是高速接口,另一个就是实现链路层和事务层的硬核,这篇文章就是介绍这部分,结合pg054是PCIE核的介绍,看起来更事半功倍。等PCIE协议相关文章更完了应该就会更新对这篇文章的介绍。

09、ug479

DSP相关资源的介绍,看了更知道咋用了,要不不知道咋优化都

10、ug480

主要介绍XADC,我们可以例化XADC来试试检测温度电压等,有点用。

看这些文章需要技巧,因为有些内容太啰嗦还没用,所以最好带着问题去看。看这些文章也需要耐心,静下心会迎来豁然开朗收获满满的时候。

2、搭建最小系统

一个典型的FPGA最小系统通常可以包括:

FPGA芯片

外部晶振(时钟源)

复位电路(在系统启动时需要对FPGA进行复位,确保FPGA内部逻辑和外部接口处于已知的初始状态)

电源电路(如LDO稳压器)

配置存储(如SPI Flash)

JTAG或其他编程接口(用于调试或配置)

2.1芯片配置

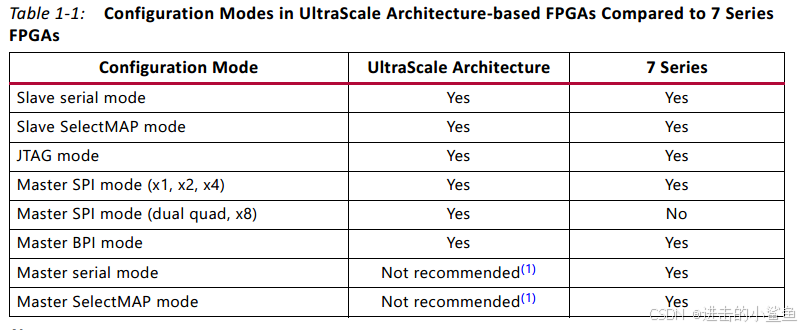

FPGA有7种配置模式,由模式输入引脚M[2:0]决定。常用的是主SPI和JTAG或者主BPI和JTAG。

7种模式可分为3大类,

1、JTAG模式(可归为从模式);

2、主模式;

3、从模式。

主模式分为Master Serial模式、Master Parallel模式;

从模式分为Slave Serial模式、Slave Parallel模式。

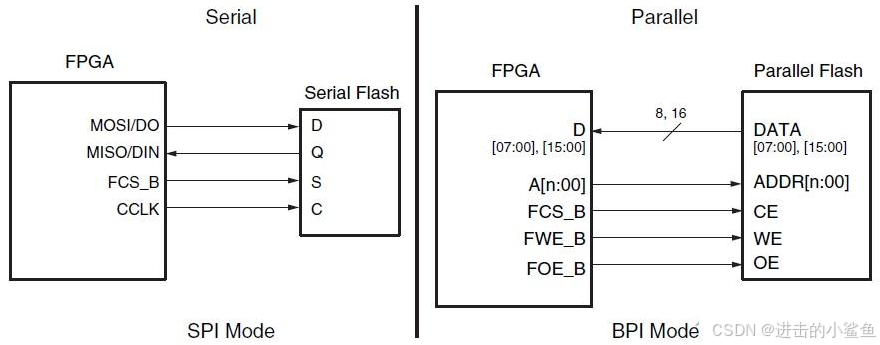

主模式:

自加载FPGA配置模式,通常称为主模式,可用于串行或并行数据传输路径。在主模式下,FPGA的配置位流通常驻留在同一板上的非易失性存储器中。FPGA内部产生称为称为CCLK的配置时钟信号,FPGA通过闪存发送时钟或地址来控制配置过程。其框图如下所示。

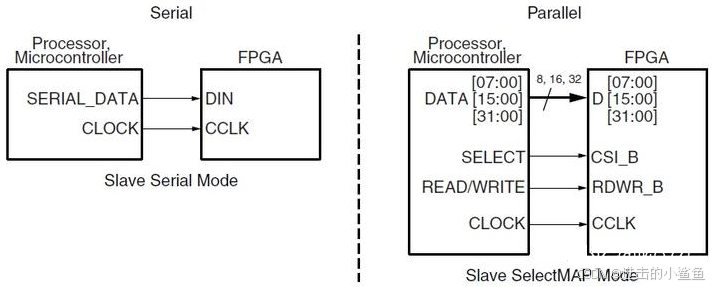

从从模式:

从从模式:

外部控制加载FPGA配置模式,通常称为从模式,也可用于串行或并行数据传输路径。在从模式下,外部处理器、微控制器、DSP处理器或测试器将配置图像下载到FPGA中,如下图所示。从配置模式的优点是FPGA比特流几乎可以驻留在整个系统的任何地方。比特流可以与主机处理器代码一起驻留在闪存中,驻留在硬盘中或者通过网络连接的某个地方。

从串行模式是一个简单的接口,由时钟和串行数据输入组成。从SelectMAP模式是x8、x16或x32位宽处理器的外围接口,包括芯片选择输入和读写控制输入。

JTAG连接:

JTAG模式同样是串行配置模式,广泛用于原型制作和板测试。四引脚JTAG边界扫描接口在板载测试设备和调试硬件很常见。Xilinx基于UltraScale架构的FPGA编程电缆使用JTAG接口进行原型下载和调试。如下图所示。

总结:

- 在设计电路图时,为选择最优的FPGA配置方案,需主要考虑以下4个方面:总体设置,下载速率,成本,配置灵活性。

- 在主模式下,FPGA自动加载配置文件数据,该配置文件数据存储于板载ROM里;从模式下,通过外部MCU/处理器将配置文件数据加载到FPGA中。

- 用作配置FPGA的专用管脚在配置完成后不能够被用作普通IO管脚,而非专用管脚在配置完毕后即被释放,可用做普通IO管脚。

- 电路设计时,一定要对M[2:0]管脚进行正确的电平设定。为了今后扩展需要或者暂时不确定为FPGA选择何种配置模式,可为M[2:0]管脚同时预留上拉和下拉电阻,便于灵活选择。

2.2供电电源电路

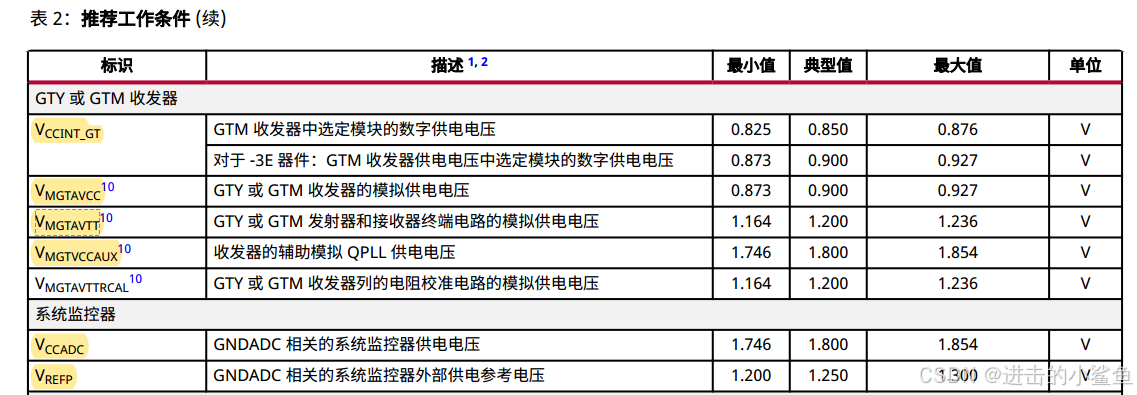

以XCVU13P-2FHGB为例:供电需要注意电压(DS923),电流(DS923),上电顺序和参考滤波电容(UG583),以减少输入纹波。

2.3.1普通电源

VCCINT:

VCCINT是FPGA芯片的内核电压,是用来给FPGA内部的逻辑门和触发器上的电压。即芯片的晶体管开关是由核心电压提供。当内部逻辑工作时钟速率越高,使用逻辑资源越多,则核心电压供电电流会更大,可高达几安,此时芯片必然会发烫,需要散热装置辅助散热。

VCCAUX:

FPGA并非一个单纯的数字逻辑芯片,内部也带有一些模拟组件,比如Xilinx的DCM数字时钟管理组件、高档点的FPGA还有高速串并转换器serdes、温度监控器件等这些模拟器件,这些模拟器件对电源噪声要求很高,所以需要一个独立稳定的电源进行供电。Vccaux就是为这些模拟器件提供电压,另外Vccaux还可以给部分IO供电,像JTAG等。

VCCBRAM:

VCCBRAM为FPGA Block RAM的供电引脚,FPGA内嵌的块RAM存储器的供电电压,因为FPGA片上RAM存储器由内部PL端逻辑负责控制,对芯片内部逻辑数据暂时存储。

VCCBATT

加密电源,用不到可以接地或者和VCCAUX一个电源。

VCCO:

FPGA的BANK供电,表示该引脚的输入电压就是I/O端口电压。

VCCAUX_IO:

IO辅助电压。根据不同的速率要求,辅助电压可以选择为1.8V或者2.0V,只有HP BANK 有。

VIN:

VIN引脚电压输入引脚应该作用于VCCO电压钳位,VREF和差分I/O的I/O输入电压(当VCCO = 3.3V时)

IIN :

IIN正向偏置钳位二极管,作用在(PS或PL)端电流输入,保证最大电流输出的钳位,注意每个PS或PL组总电流不应超过200MA,连接4.7K上拉电阻限制电流(应该是原理图和官方手册有轻微出入)。

2.3.2MGT电源 高速串行收发器模块

VMGTAVCC

收发器模块的收发供电。

VMGTAVTT

收发器模块的端接电源。

MGTVCCAUX

收发器的辅助电源。

MGTAVTTRCAL/MDTRREF

收发器的校正电压。

VCCADC

XADC的供电电压。

电路注意事项:

MGTAVCC和MGTRREF之间串一个100R 1%精度的0603电阻,用于端接阻抗校准。

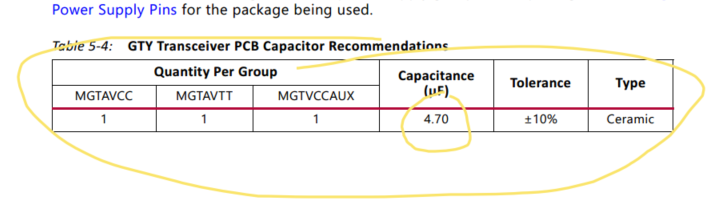

MGTAVCC:滤波电容推荐使用1个4.7uF电容,外加每个PIN都要一个0.1uF电容。(由PCB Design文档获得,不同芯片要求可能不一样)

MGTAVTT:滤波电容推荐使用1个4.7uF电容,外加每个PIN都要一个0.1uF电容。

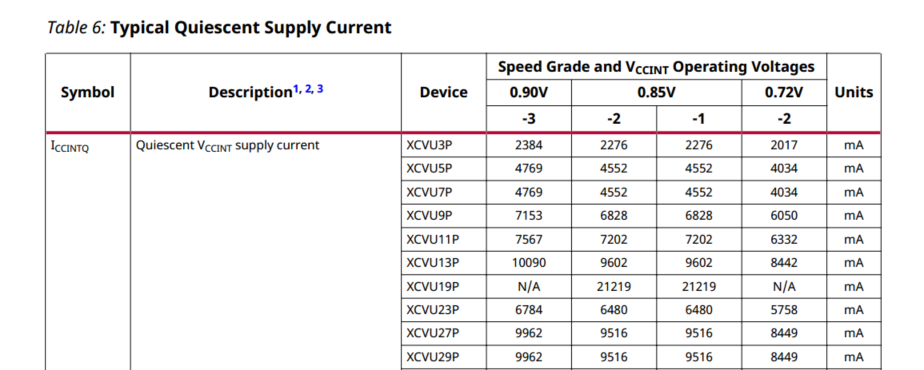

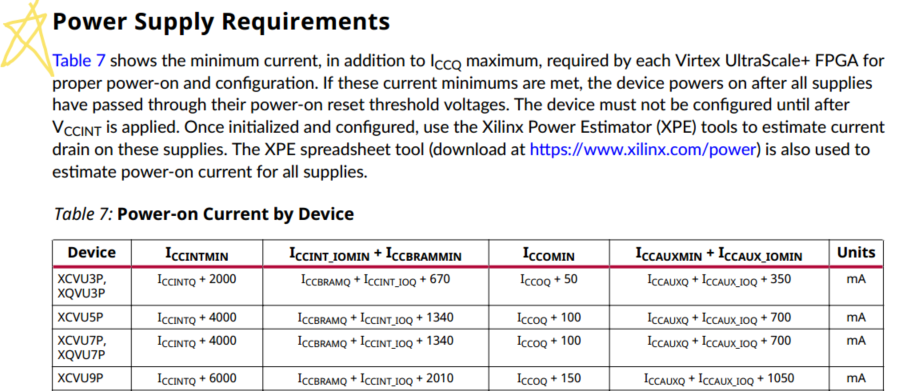

2.3.3电流要求

DS923中有各芯片静态电流要求,和启动和配置最小电流要求。

2.3.4上电顺序

普通电源:【从低到高】

一般上电顺序依次是VCCINT->VCCBRAM->VCCAUX->VCCO->VCCAUX_IO

(内核、RAM、辅助、IO电源)

推荐上电顺序为 VCCINT、VCCINT_IO/VCCBRAM、VCCAUX/VCCAUX_IO 和 VCCO,这样即可实现最低电流汲取并确保上电时 I/O 处于三态。推荐的断电顺序与上电顺序相反。如果 VCCINT 和 VCCINT_IO/VCCBRAM 的推荐电压电平相同,那么可使用相同电源为其供电并同步执行缓升。VCCINT_IO 必须连接到 VCCBRAM。如果 VCCAUX/VCCAUX_IO 和 VCCO 的推荐电压电平相同,那么可使用相同电源为其供电并同步执行缓升。VCCAUX 和 VCCAUX_IO 必须连接在一起。VCCADC 和 VREF 可随时上电,无上电顺序要求。

MGT电源

为 GTY 或 GTM 收发器实现最小电流汲取的推荐上电顺序为 VCCINT、VCCINT_GT、VMGTAVCC、VMGTAVTT 或 VMGTAVCC、VCCINT、VCCINT_GT 和 VMGTAVTT。针对 VMGTVCCAUX 不存在推荐的排序。VMGTAVCC 和 VCCINT 均可同时执行电源缓升。当 VCCINT 和 VCCINT_GT 处于相同的推荐工作条件下时,VCCINT 和 VCCINT_GT 可连接到相同的电源调节电路。当 VCCINT 和 VCCINT_GT 连接到不同调节电路时,VCCINT_GT 必须处于推荐的工作条件范围内才能执行器件配置。推荐的断电顺序与实现最小电源汲取的上电顺序相反。如果不满足这些推荐的顺序,那么上电和断电期间从 VMGTAVTT 汲取的电流可能高于相应的规格。

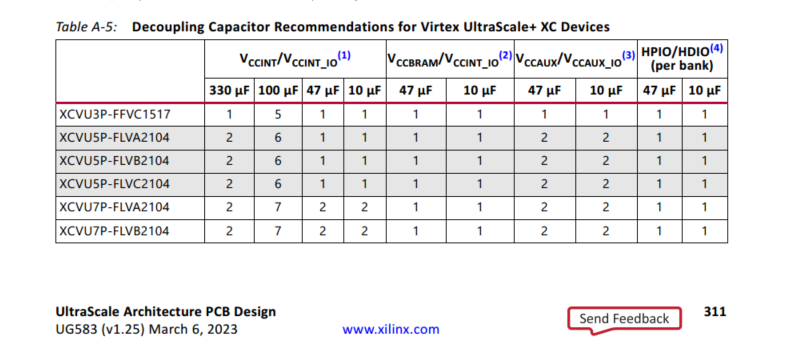

2.3.5去耦电容

要以ug583等官方文档中推荐的去耦电容数量为最少标准。

附录A中的去耦电容表没有提供GTY或GTH收发器电源所需的去耦网络。有关此信息,请参阅《UltraScale架构GTH收发器用户指南》(UG576)[参考文献6]或《UltraScale体系结构GTY收发器用户指南(UG578)》[参考文献7]。

UG578:

3757

3757

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?