基础介绍

Zynq UltraScale+ MPSoC 系列是 Xilinx 新一代 Zynq 平台,PS升级成了四核 Cortex-A53 处理器加双核 Cortex-R5 处理器。该芯片包含PS和PL两部分,PS就是Processing System,说白了就是ARM部分;PL就是Programable Logic,说白了就是FPGA。两者在内部可以通过AXI、GPIO或其他专用信号通信互联。

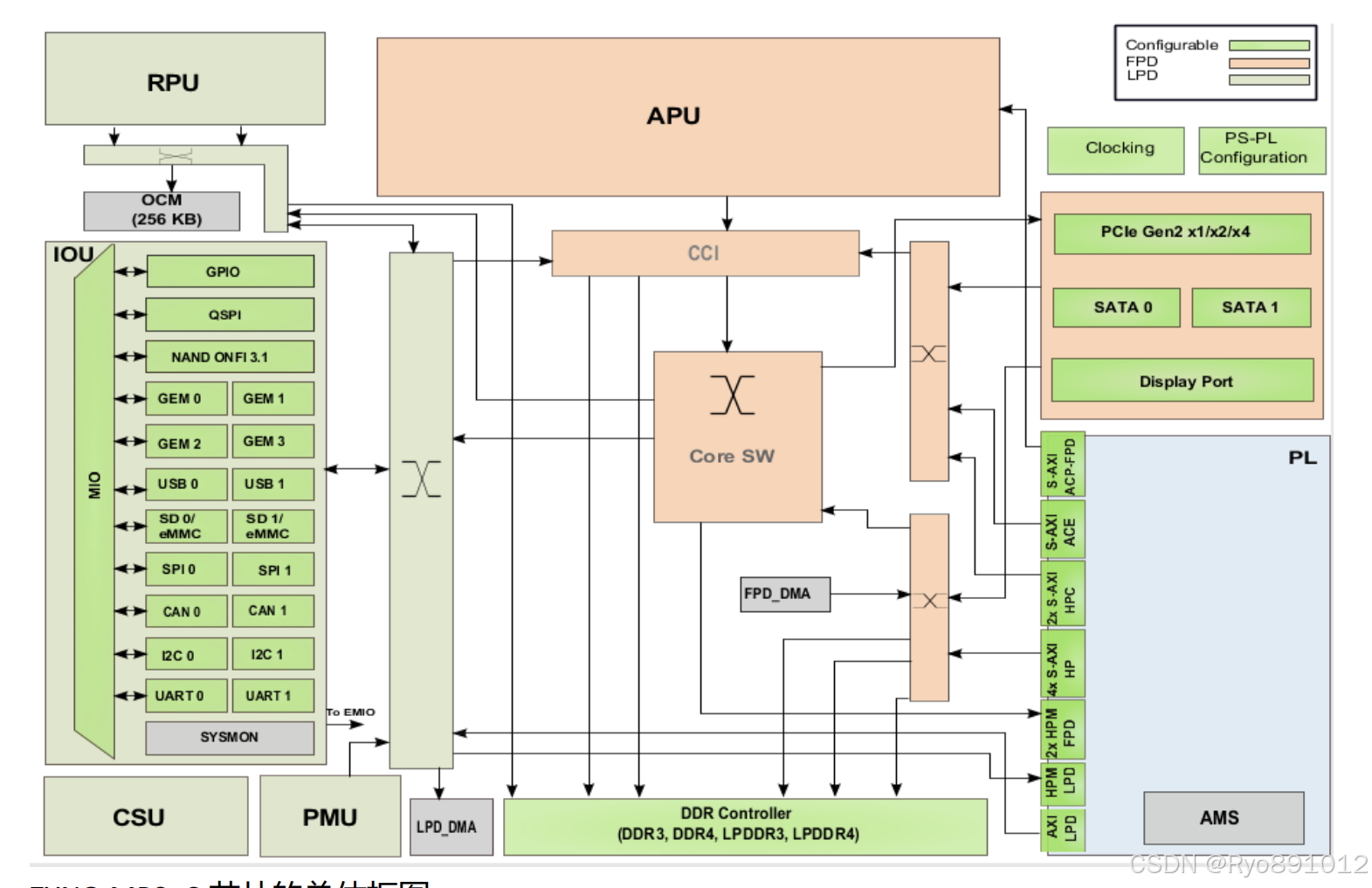

来,瞅一眼芯片的框图:

AXI互联

PS和PL主要通过AXI交互数据,一共有12个AXI接口:

S_AXI_HP{0:3}_FPD:是高性能AXI接口,同旧版zynq7000的HP类似,PL做master访问PS用;

S_AXI_HPC{0,1}_FPD:是高性能AXI接口,相比上面4个,可以访问到cache;

S_AXI_LPD:直接连到LPD区域,低延迟访问低速外设,也是PL去访问PS;

M_AXI_HPM{0,1}_FPD:PS访问PL的高性能口,用于CPU推送大量数据到PL;

M_AXI_HPM0_LPD:PS访问PL的低延迟口,常用于PS访问PL的寄存器,类似zynq7000的GP口;

S_AXI_ACE_FPD:

S_AXI_ACP_FPD:

这两个口常用来搞啥?我也搞求不懂,可能比较少用吧。。。

启动流程

zynq系列和传统fpga启动有很大不一样,传统fpga主要是上电后自己去flash读取bit位流,然后开始工作;而zynq系列因为有ARM,芯片通道后,先是ARM启动,然后ARM去加载FPGA;FPGA就成了一个被动设备。

所以哪怕你开发一个简单的点led的fpga功能,要实现上电启动,也得走一遍PS的开发过程,让ARM启动起来。

所以,如果你只想做一些简单的逻辑功能,一点不好玩 。。。

5083

5083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?