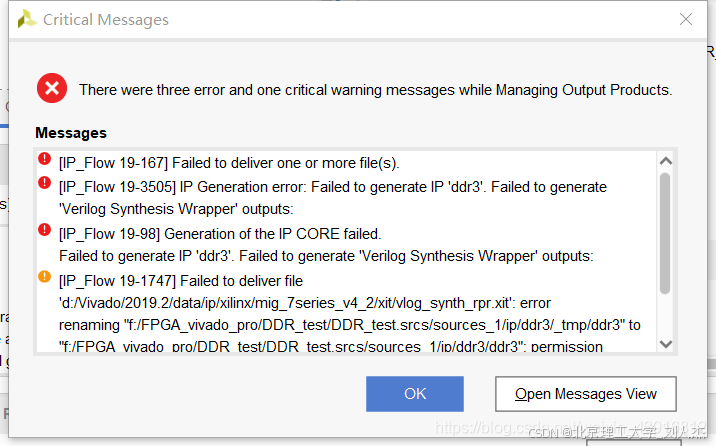

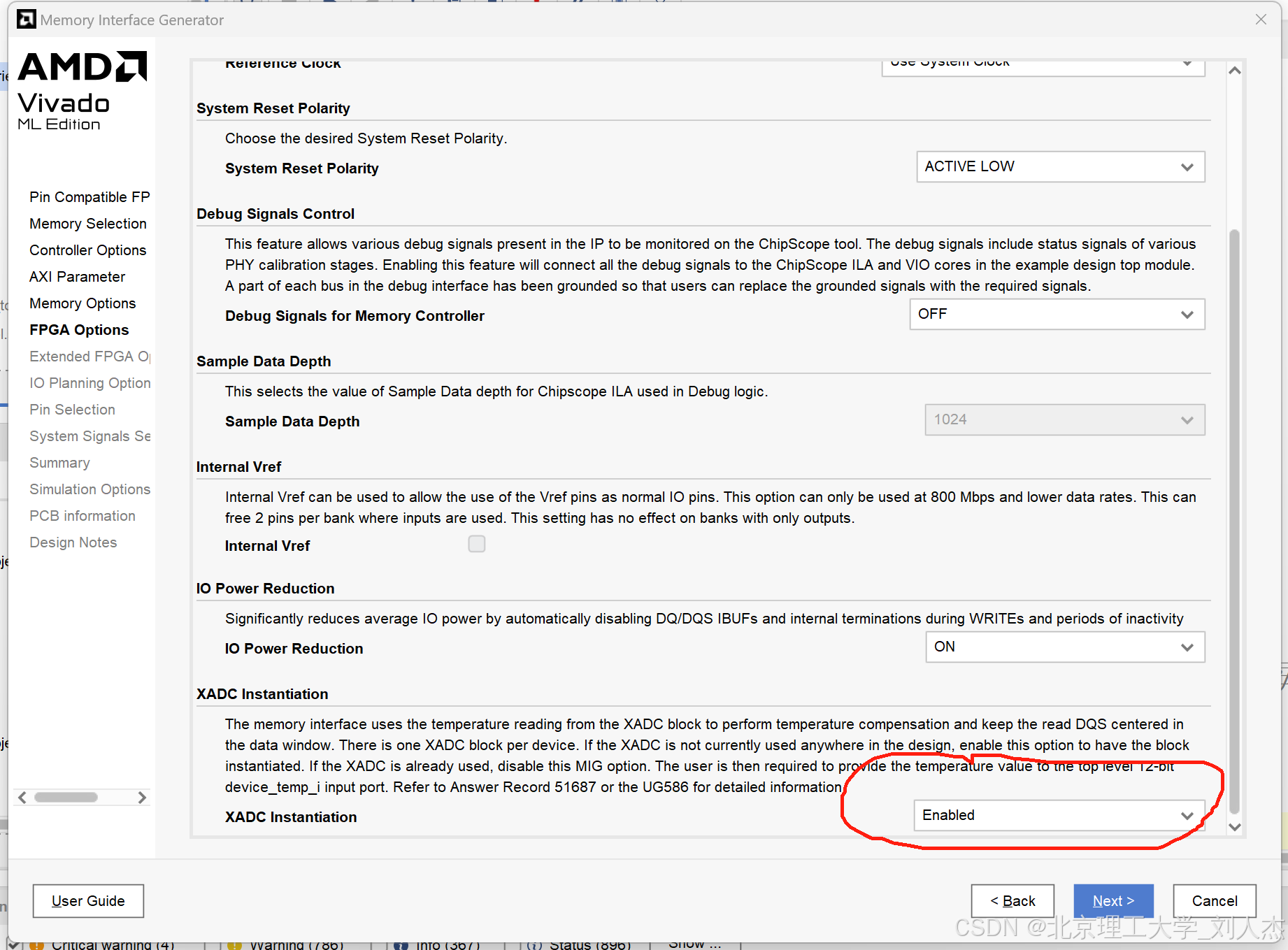

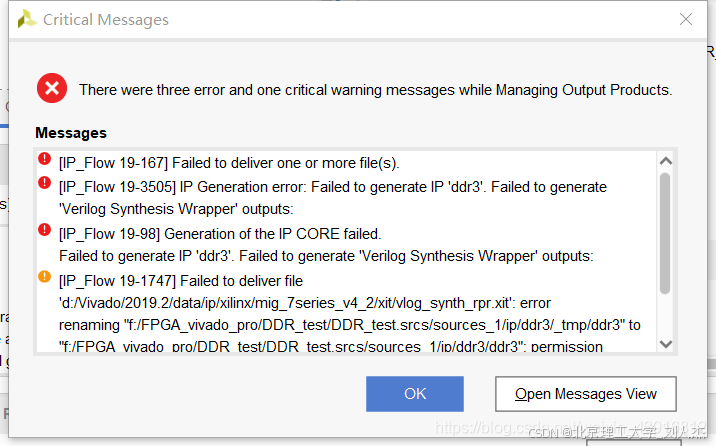

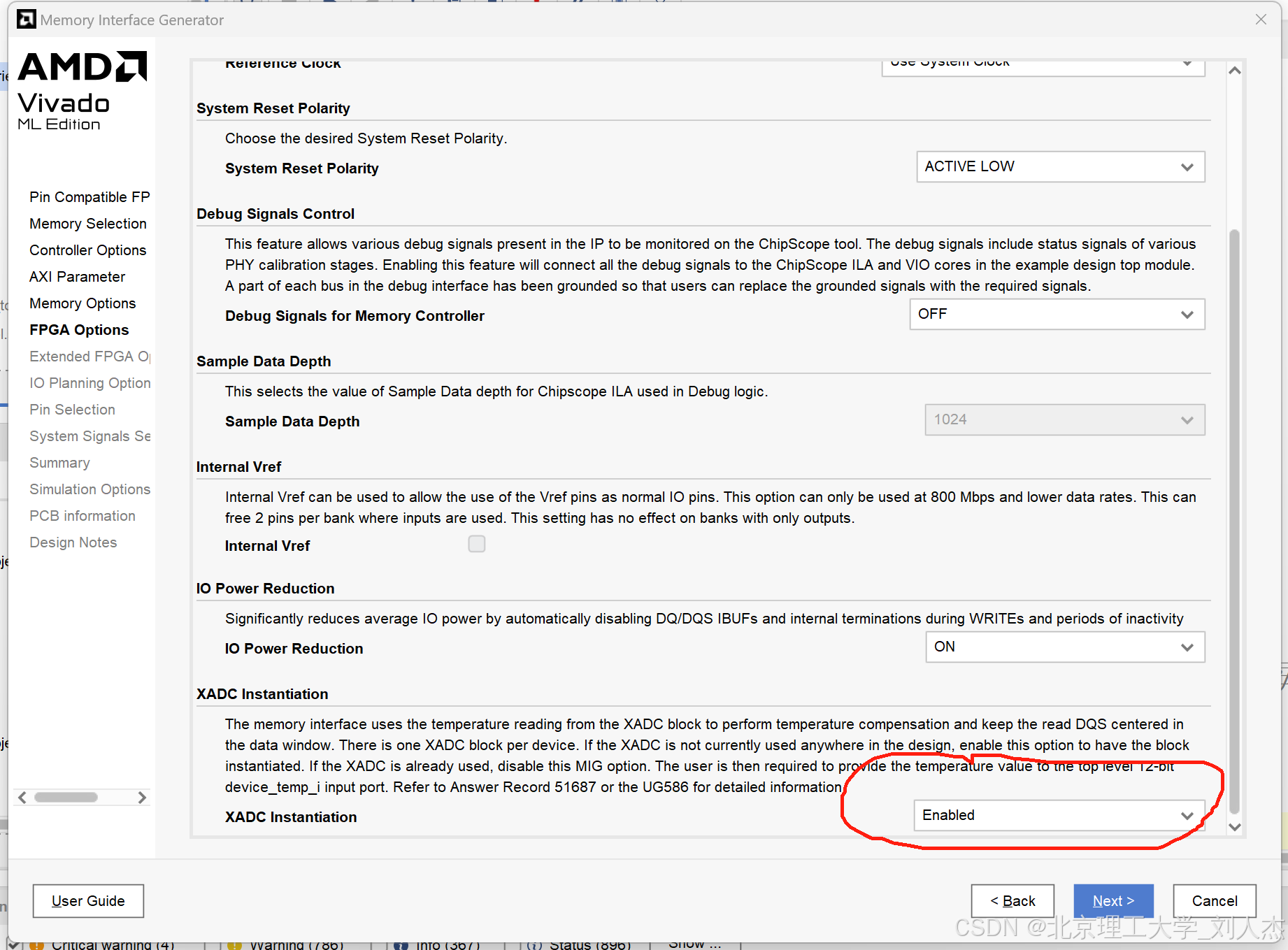

我重新生成了好几次都有这个问题,最后发现是IP设置这里 XDAC这里的温度检测得“Enabled”

Vivado MIG IP生成报错

最新推荐文章于 2024-12-22 09:43:16 发布

我重新生成了好几次都有这个问题,最后发现是IP设置这里 XDAC这里的温度检测得“Enabled”

5141

5141

1413

1413

7028

7028

4804

4804

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?