STM32L4x系列芯片运行的主频最高可达80MHz,但芯片内部自带的振荡器或外部晶体均达不到这么高的频率,为了最大限度发挥芯片的性能,需要提供一种机制,将这些时钟源的频率倍频到接近或等于80MHz,以充分发挥芯片的性能。所以STM32L4x系列芯片内部提供了一种倍频电路,即PLL。

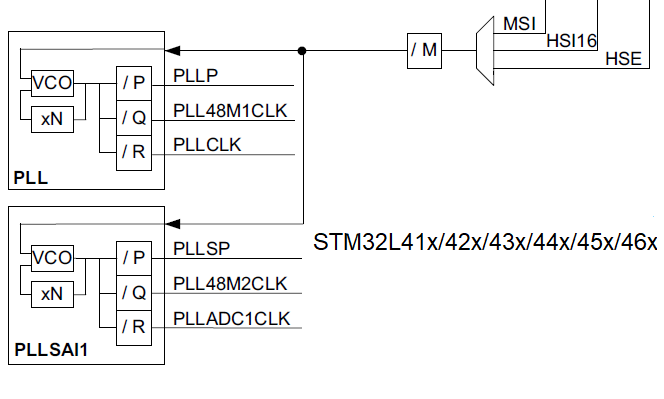

STM32L41x/42x/43x/44x/45x/46x系列芯片内部嵌入了2个PLL:PLL、PLLSAI1。每个PLL最多提供三个独立的输出,如下图:

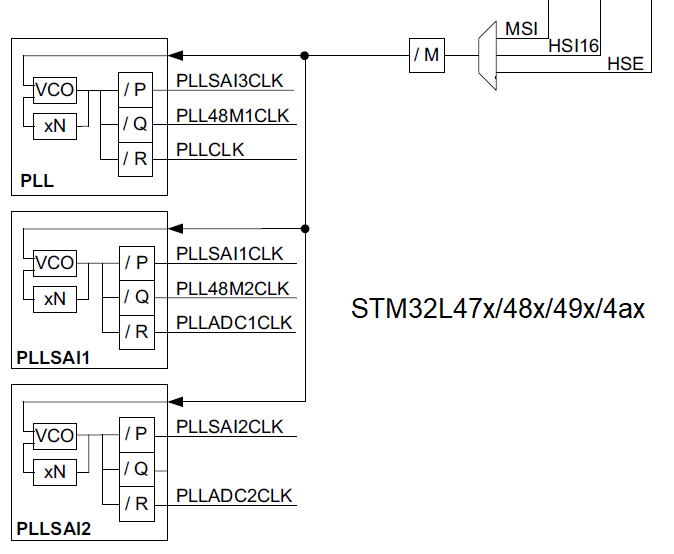

STM32L47x/48x/49x/4ax系列芯片内部嵌入了3个PLL:PLL、PLLSAI1、PLLSAI2。每个PLL最多提供三个独立的输出,如下图:

可以用作PLL输入时钟的时钟源包括:

- MSI :内部多频率时钟,时钟频率可以设定,频率范围从100kHz到48MHz

- HSI16:内部高速16MHz

- HSE:外部高速晶体振荡器,频率范围是4MHz到48MHz

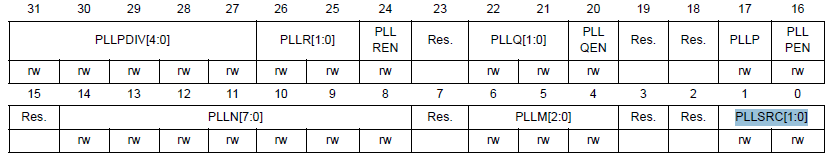

这三个时钟通过寄存器(RCC_PLLCFGR)的(PLLSRC[1:0])位(图1)来选择其中一个作为PLL的输入时钟。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1087

1087

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?