什么是PLL锁相环

解决一个单片机需要多个晶振的问题

它有一个电压或者电流驱动的振荡器

可以不断调整来匹配输入信号的相位

所以PLL用来进行频率控制

可以配置成频率乘法、除法、解调器戚、跟踪生成器或者时钟恢复电路

实现一共晶振达到等多种频率的效果 随时可变/稳定的效果

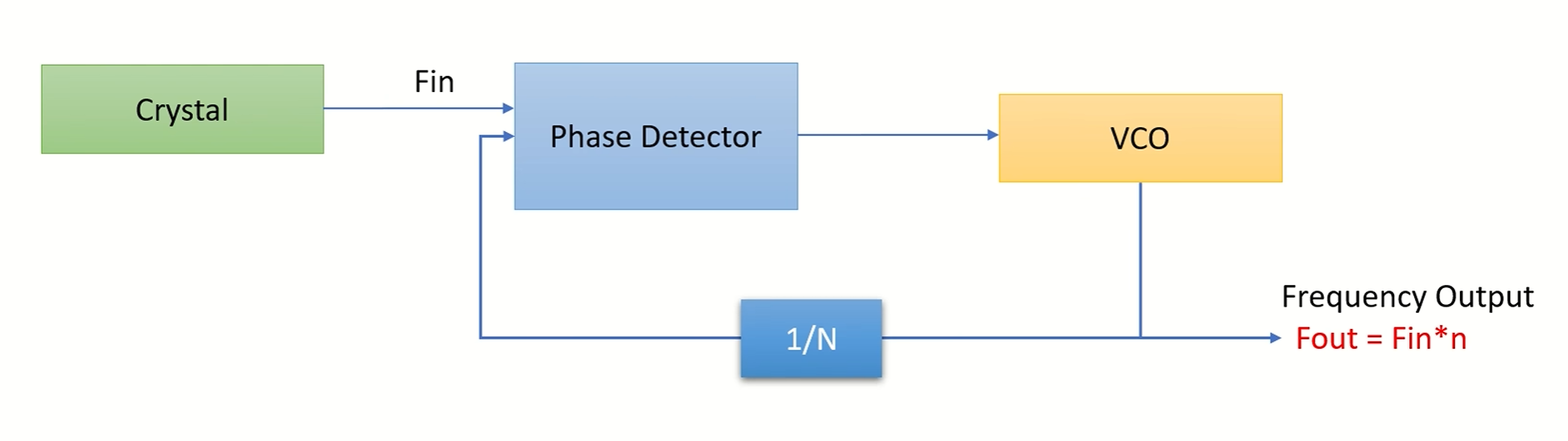

工作原理:

- 晶体输出

Fin到鉴相器; - VCO 输出

Fout,同时反馈回鉴相器; - 鉴相器比较

Fin和反馈的Fout,若存在相位 / 频率差,就输出控制信号调整 VCO; - 最终让

Fout的频率锁定到Fin(图中Fout = Fin),实现精准的频率同步。

- VCO 输出

Fout,并送入1/N分频器,得到Fout/N的反馈信号;

2.将晶体输出的 Fin 进行 1/M 分频,得到 Fin/M 的信号

3.最终让 Fin/M = Fout/N(锁相环的 “锁定” 条件),因此推导得 Fout = Fin * N/M,实现了输入频率的 N/M 倍调节(可倍频、分频或保持频率,取决于 N 和 M 的数值关系)。

- Loop Filter(环路滤波器):对鉴相器输出的误差信号进行滤波和整形,去除高频噪声和毛刺,输出平滑的控制电压 / 电流给 VCO。它是保障 PLL 稳定性的

PLL锁相环原理解析

PLL锁相环原理解析

8722

8722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?