二进制编码

R进制相互转换

(1) 十进制 → 二进制(整数 + 小数分开转换)

- 整数部分:除 2 取余,逆序排列(直到商为 0,余数从最后一个到第一个)。

- 例:十进制 13 → 二进制13÷2=6 余 1,6÷2=3 余 0,3÷2=1 余 1,1÷2=0 余 1 → 逆序得 1101。

- 小数部分:乘 2 取整,顺序排列(直到小数部分为 0 或达到精度要求,整数从第一个到最后一个)。

- 例:十进制 0.625 → 二进制0.625×2=1.25 取 1,0.25×2=0.5 取 0,0.5×2=1.0 取 1 → 顺序得 0.101。

- 组合:13.625₁₀ = 1101.101₂。

(2) 十进制 → 十六进制

- 方法 1:先转二进制,再按 “4 位二进制→1 位十六进制” 分组(整数从右分组,小数从左分组,不足补 0)。

- 例:13.625₁₀ = 1101.101₂ → 整数 1101=D,小数 1010(补 0)=A → D.A₁₆。

- 方法 2:除 16 取余(整数)、乘 16 取整(小数),直接转换。

(3) 二进制 / 十六进制 → 十进制

按位权展开求和:

- 二进制 1101.101₂ = 1×2^3 + 1×2^2 + 0×2^1 + 1×2^0 + 1×2^-1 + 0×2^-2 + 1×2^-3 = 8+4+0+1+0.5+0+0.125 = 13.625₁₀。

- 十六进制 D.A₁₆ = 13×16^0 + 10×16^-1 = 13 + 0.625 = 13.625₁₀。

(4) 二进制 ↔ 十六进制(快速转换)

- 二进制→十六进制:4 位一组,不足补 0,每组对应 1 位十六进制(0000=0,1111=F)。

- 例:1101101.101₂ → 0110 1101 . 1010 → 6D.A₁₆。

- 十六进制→二进制:1 位拆 4 位,不足补 0。

- 例:3F.8₁₆ → 0011 1111 . 1000 → 111111.1₂。

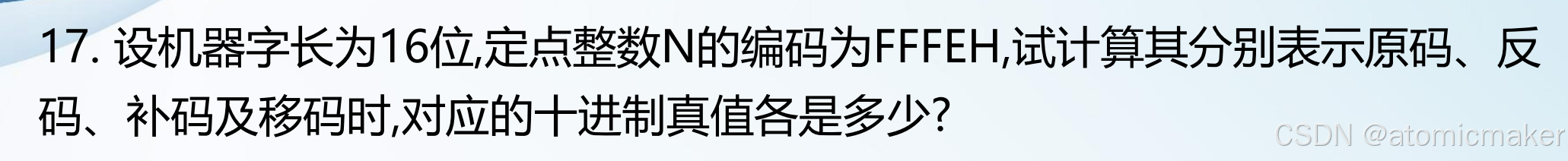

机器码与真值的相互转换

| 机器码类型 | 正数(真值 X>0) | 负数(真值 X<0) |

|---|---|---|

| 原码 | 符号位 0 + 数值位(X 的二进制) | 符号位 1 + 数值位(X 的二进制) |

| 反码 | 同原码 | 符号位 1 + 数值位(X 的二进制按位取反) |

| 补码 | 同原码 | 反码 + 1(符号位不变,取反加一) |

| 移码 | 补码的符号位取反 | 补码的符号位取反 |

补充:[X]补 按位取反加一(符号位也取反) -> [-X]补

综合应用

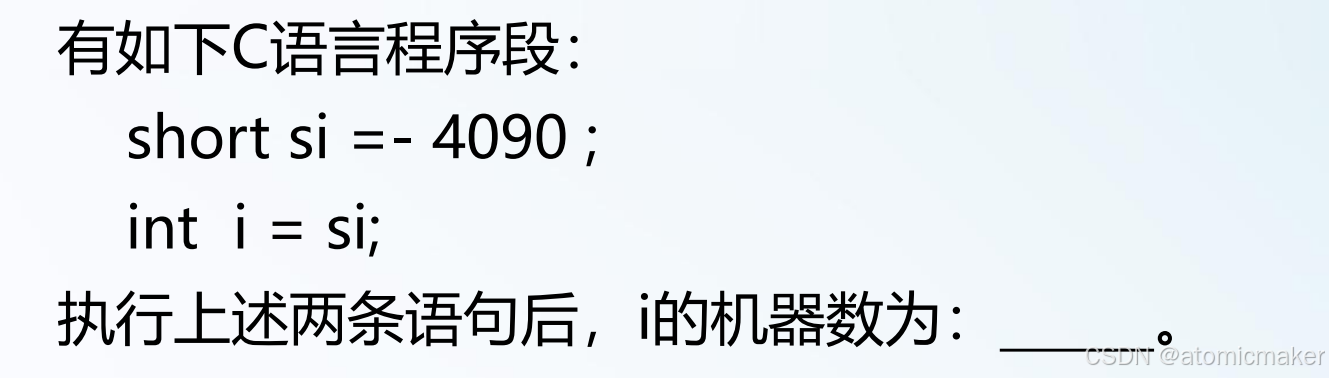

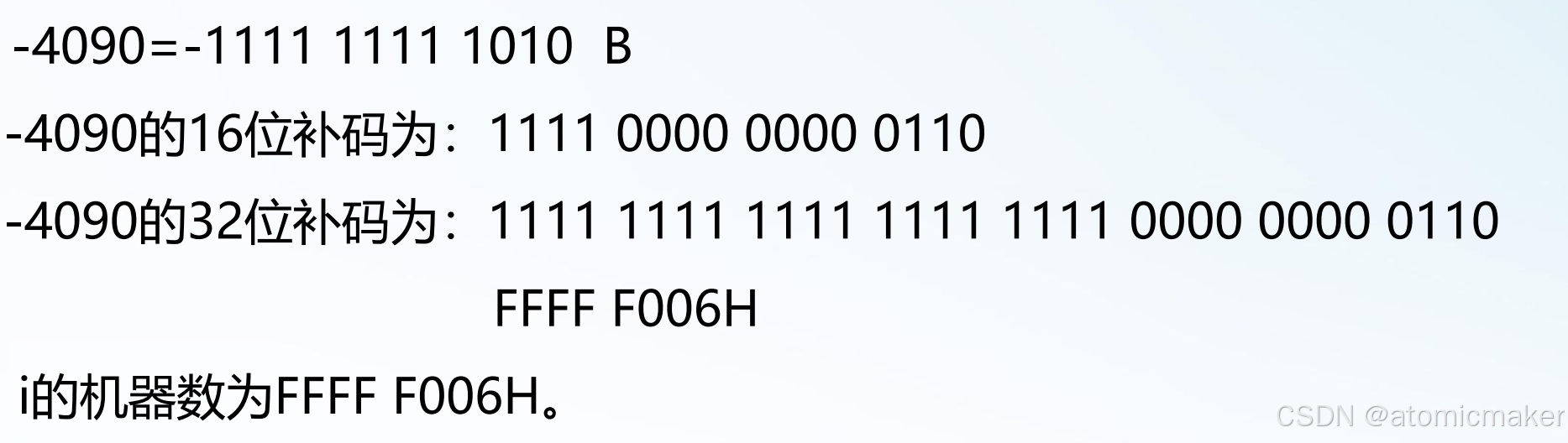

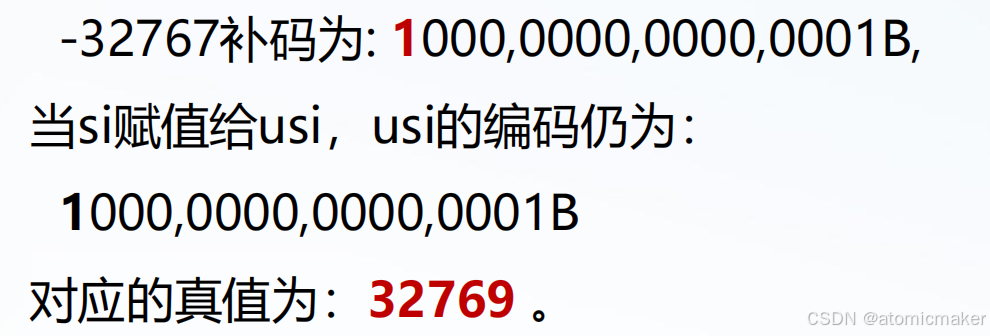

1.有符号数

C语言中有符号整数为补码形式。

补码符号扩展:添符号位

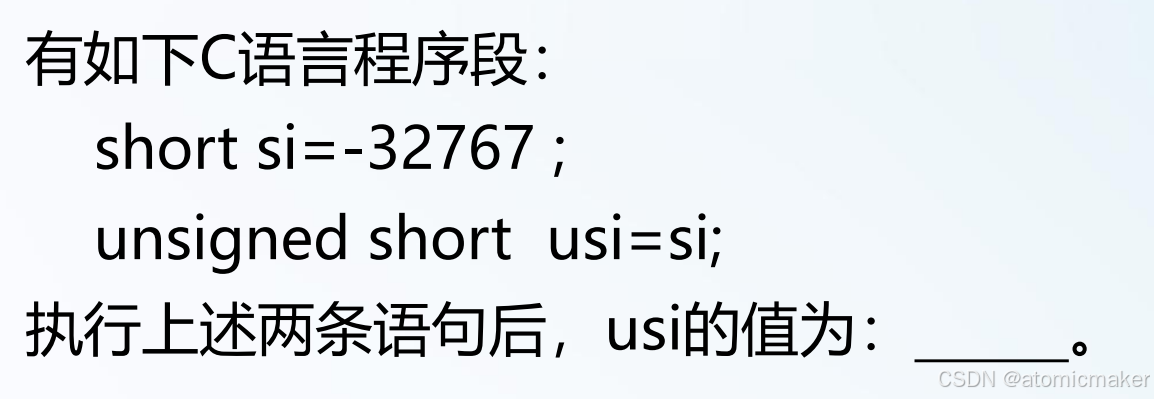

2.无符号数

无符号数全部位为数值位,直接转换(把符号位也算进去作数值位)。

单精度 IEEE754 浮点数标准(32位)

单精度浮点数将32为分为3部分:

| 符号位(S) | 阶码位(E) | 尾数部分(M) | 总位数 |

|---|---|---|---|

| 1 位(第 31 位) | 8 位(第 30-23 位) | 23 位(第 22-0 位) | 32 位 |

- 符号位 S:0 = 正数,1 = 负数。

- 阶码位 E:采用移码表示,偏移量 = 127(即阶码真值 = E 的二进制值 - 127)。

- 尾数部分 M:隐含整数位 1(即尾数实际值 = 1.M),采用二进制小数表示。

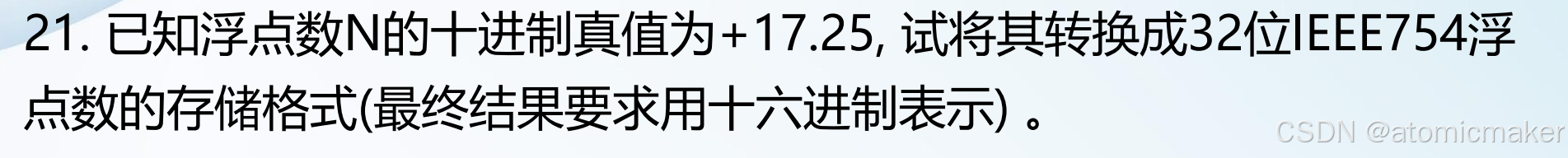

真值 ↔ 32 位 IEEE754 转换规则

1) 真值→IEEE754

- 将真值转换为二进制科学计数法:X = (-1)^S × (1.M) × 2^e(e 为阶码真值)。

- 计算阶码位 E:E = e + 127(转换为 8 位二进制,不足补 0)。

- 截取尾数部分 M:取 1.M 的小数部分,保留 23 位(超出截断,不足补 0)。

- 组合:S(1 位)+ E(8 位)+ M(23 位)。

2)IEEE754 →真值

- 拆分 32 位为 S、E、M 三部分。

- 计算阶码真值 e:e = [E]十进制 - 127。

- 计算尾数实际值:1.M = 1 + [M]十进制。

- 计算真值:X = (-1)^S × (1.M) × 2^e。

运算方法和运算部件

基本运算部件

运算部件种类(了解)

1.串行进位加法器

由n 个全加器(FA) 级联构成,每一位全加器的进位输出 Ci 作为下一位全加器的进位输入Ci+1,进位信号从最低位(LSB)向最高位(MSB)逐位传递。

2.并行进位加法器

通过进位生成逻辑提前计算每一位的进位 Ci,无需等待低位进位,所有位的进位和和值可并行计算,核心是推导进位的 “生成项” 和 “传递项”。

3.带标志位加法器

在并行进位加法器基础上,增加标志位生成电路,运算后输出反映运算结果特征的标志位,支持程序判断和异常处理

4.算术逻辑部件(ALU)

通用运算部件,可通过控制信号选择实现算术运算(加减、移位)或逻辑运算(与、或、非、异或),是 CPU 运算器的核心。

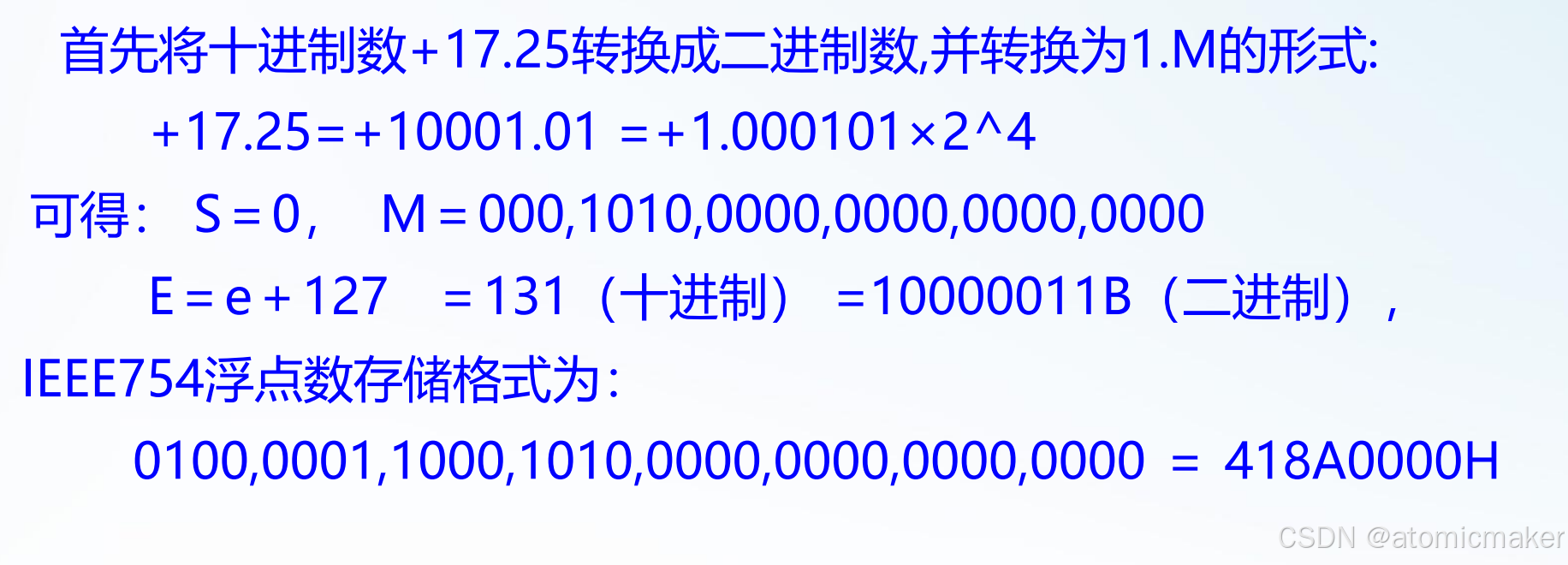

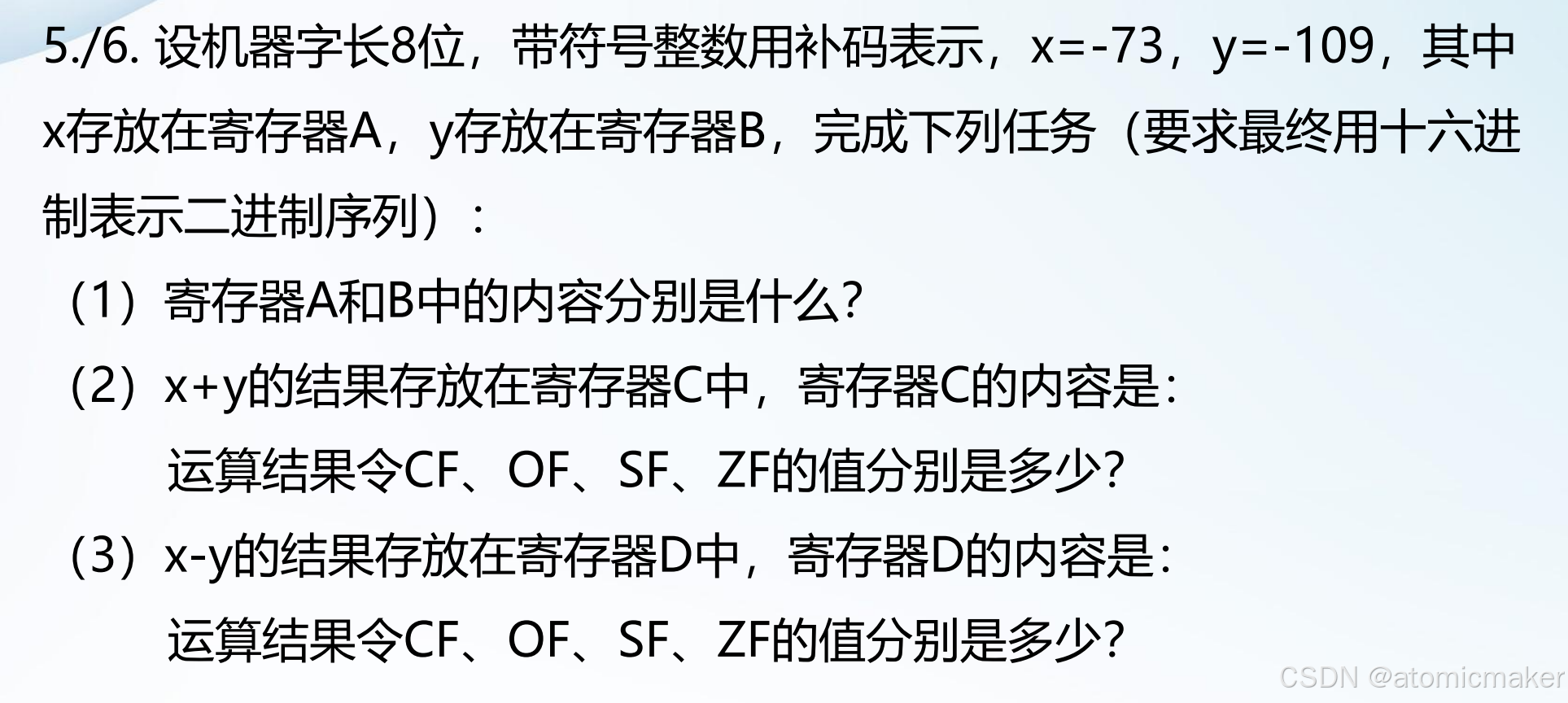

核心标志位(主)

| 标志位 | 符号 | 含义 | 判断规则(以 n 位补码加法为例) |

|---|---|---|---|

| 进位标志 | CF | 运算的进位 / 借位 | 有进位/借位 -> 1 |

| 零标志 | ZF | 运算结果是否为 0 | 结果为0 -> 1 |

| 符号标志 | SF | 运算结果的符号(补码) | 负数 -> 1 |

| 溢出标志 | OF | 有符号数运算是否溢出 | 溢出 -> 1 |

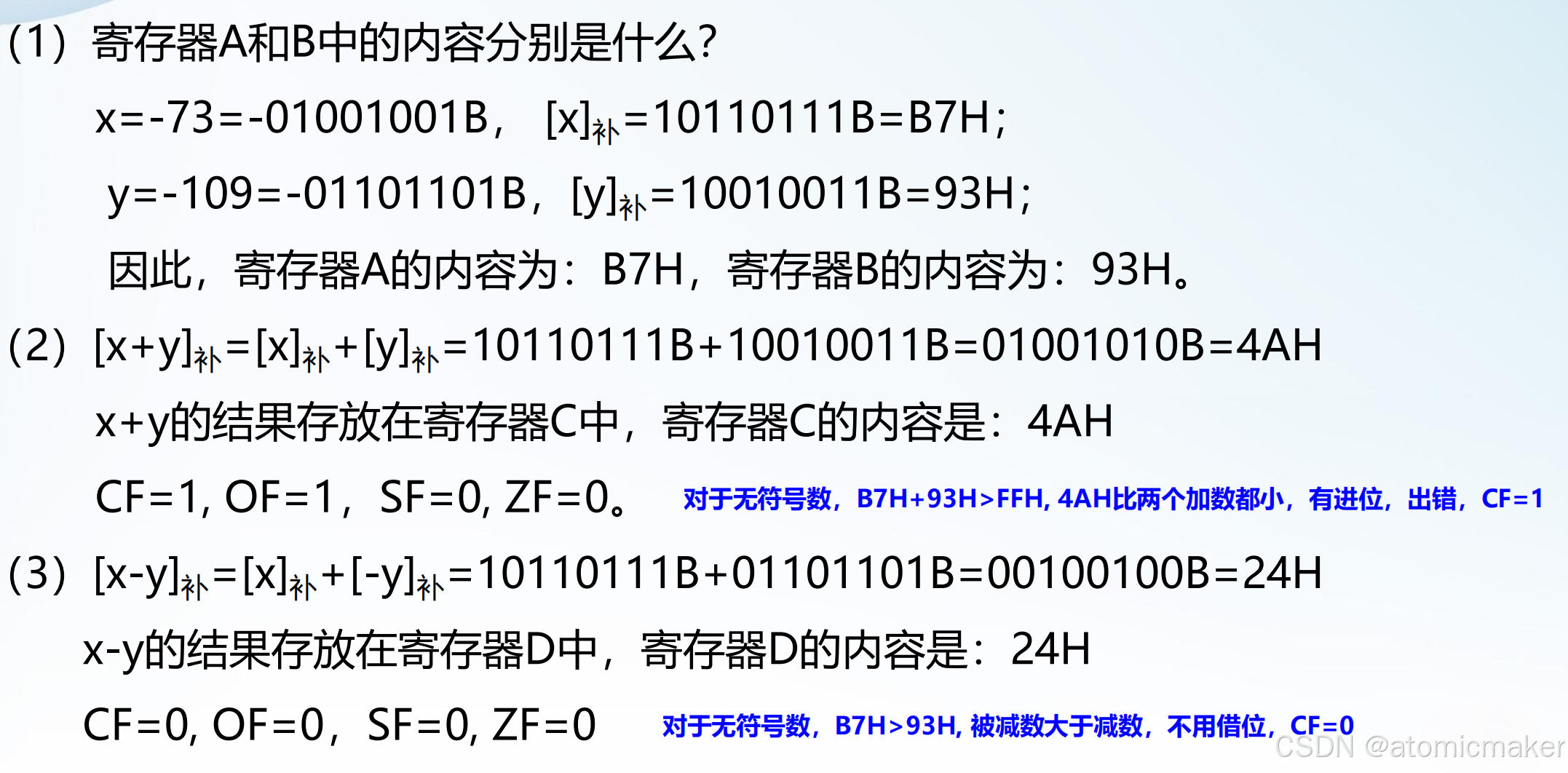

要先看下面的定点数运算再回来做这道例题

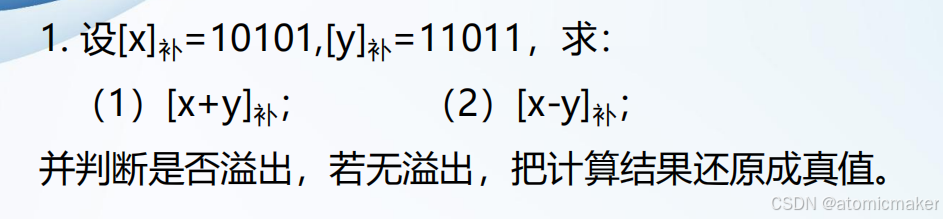

定点数运算

1.补码加减运算

基本规则(注意要忽略最高位进位):

- 补码加法:[X + Y]补 = [X]补 + [Y]补

- 补码减法:[X - Y]补 = [X]补 + [-Y]补

判断是否溢出:

通常可以先算真值来判断是否溢出

| 判断方法 | 规则 | 举例(8 位:64+65=129,超出范围) |

|---|---|---|

| 单符号位法 | 最高位进位C_7 ≠ 次高位进位C6 → OF=1 | [64]补=01000000,[65]补=01000001 相加:01000000+01000001=10000001 C7=0,C6=1 → OF=1(溢出) |

| 进位值法 | 符号位进位Cs ≠ 数值位最高进位Cn → OF=1 | 同例:符号位(第 7 位)进位Cs=0,数值位最高(第 6 位)进位Cn=1 → OF=1 |

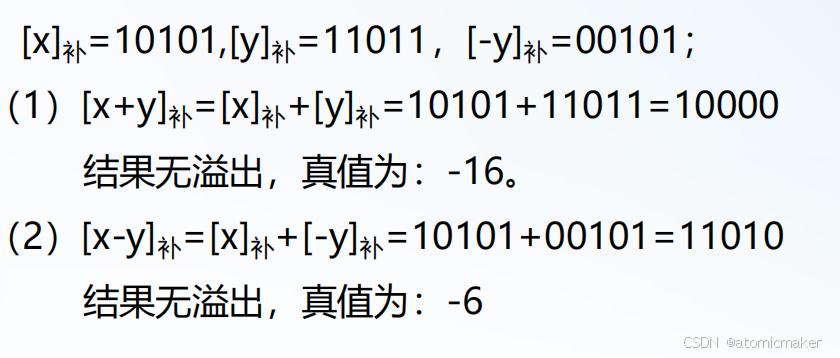

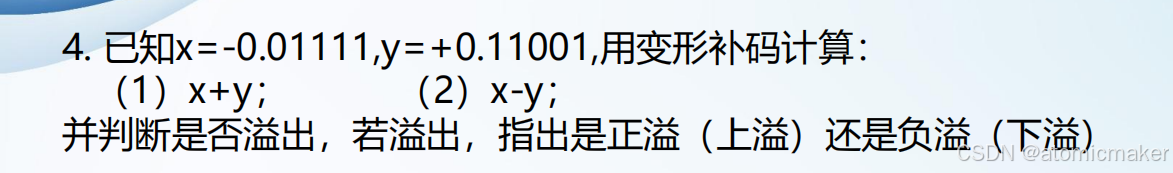

| 双符号位法(变形补码) | 补码扩展为双符号位(00 = 正,11 = 负),运算后双符号位不同(01/10)→ OF=1 | [64]补=001000000,[65]补=001000001 相加:001000000+001000001=010000001 双符号位 01 → OF=1(正溢出) |

双符号补充:01 = 正溢出,10 = 负溢出,00/11 = 无溢出

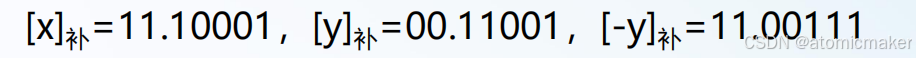

单符号位例题:

双符号位例题:

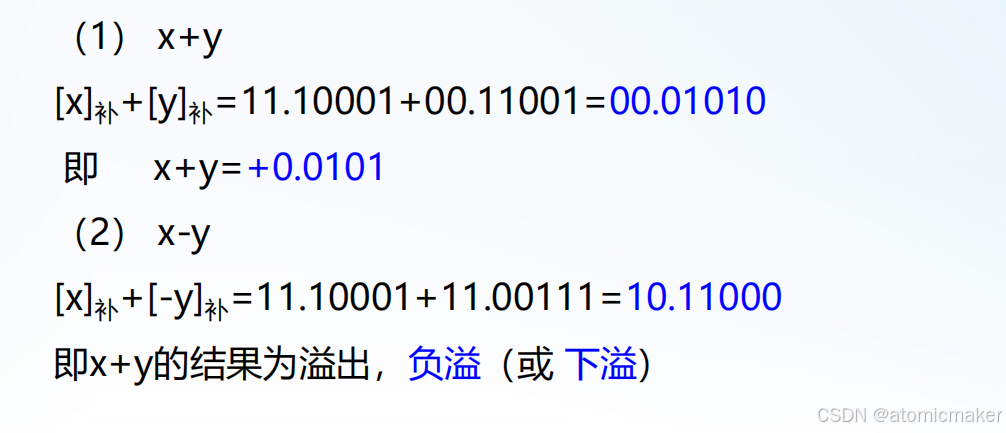

2.原码乘法运算(原码一位乘法)

[X]原 = 01011,[Y]原 = 10101

C表示前面补0;

判断 Y 的最后一位,1 -> P + X,0 -> P + 0;

n位乘数就要加n次,最后取 无符号X位数+无符号Y位数 再补上符号位。

存储器层次结构

存储器概述

1. 存储器的分类(了解)

存储器是计算机存储数据和程序的核心部件,可从多个维度分类:

| 分类维度 | 类型 | 特点 / 示例 |

|---|---|---|

| 存储介质 | 半导体存储器 | 基于半导体器件(MOS 管 / 双极型管),速度快、体积小,分为易失性(RAM)和非易失性(ROM) |

| 磁介质存储器 | 硬盘、磁带,容量大、成本低、非易失,速度慢 | |

| 光介质存储器 | CD/DVD/ 蓝光光盘,非易失,便携性好 | |

| 存取方式 | 随机存取存储器(RAM) | 任意地址单元可随机读写,访问时间与地址无关(如 SRAM、DRAM) |

| 只读存储器(ROM) | 正常工作时只读,非易失(如掩膜 ROM、EPROM、Flash) | |

| 顺序存取存储器(SAM) | 按顺序读写,访问时间与地址相关(如磁带) | |

| 直接存取存储器(DAM) | 寻址分两步(寻道 + 顺序读写),如硬盘 | |

| 层次结构 | 高速缓冲存储器(Cache) | 位于 CPU 与主存之间,速度最快、容量小,缓解 CPU 与主存速度差距 |

| 主存储器(内存) | 计算机核心存储,速度较快、容量适中,易失性 | |

| 辅助存储器(外存) | 容量大、成本低,非易失,用于长期存储 | |

| 易失性 | 易失性存储器 | 断电后数据丢失(SRAM、DRAM、Cache) |

| 非易失性存储器 | 断电后数据保留(ROM、Flash、硬盘、光盘) |

2.性能参数指标(了解)

存储器的核心性能指标决定了读写效率和使用体验:

| 参数 | 定义 | 说明 |

|---|---|---|

| 存储容量 | 存储器可存储的二进制位数 / 字节数 | 常用单位:B(字节)、KB(1KB=1024B)、MB(1024KB)、GB(1024MB)、TB(1024GB)核心公式:容量 = 地址线位数对应的单元数 × 数据线位数(如 10 根地址线 + 8 根数据线→2^10×8=8192位 = 1KB) |

| 存取时间TA | 从发出读写命令到完成操作的时间 | 衡量存储器的读写速度,Cache(ns 级)< 主存(ns~μs 级)< 外存(ms 级) |

| 存取周期TM | 连续两次独立存取操作的最小间隔时间 | TM ≥ TA,包含存储器恢复时间(如 DRAM 刷新) |

| 带宽 | 单位时间内可传输的最大数据量 | 公式:Bm = 存储容量/存取周期,单位:B/s、bit/s |

| 可靠性 | 用平均无故障时间(MTBF)衡量 | MTBF 越长,可靠性越高 |

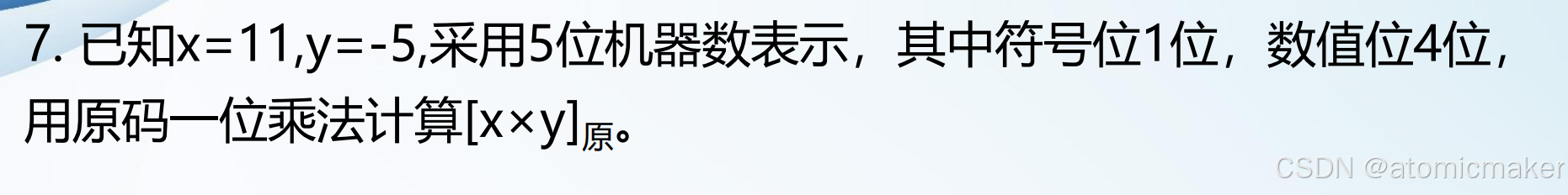

主存储器的基本结构

(1) 位扩展(增加数据线位数,字数不变)

- 适用场景:芯片字数满足需求,但位数不足(如用 8K×1 位芯片组成 8K×8 位存储器)。

- 连接规则:

- 所有芯片的地址线、控制线并联;

- 各芯片的数据线分别作为存储器的不同位(如第 1 片接 D0,第 2 片接 D1,…,第 8 片接 D7)。

(2) 字扩展(增加地址单元数,位数不变)

- 适用场景:芯片位数满足需求,但字数不足(如用 8K×8 位芯片组成 32K×8 位存储器)。

- 连接规则:

- 所有芯片的数据线、读写控制线并联;

- 新增地址线通过译码器产生片选信号,选中不同芯片(如 32K 需 15 根地址线,8K 需 13 根,新增 A13、A14 经 2-4 译码器产生 4 个片选信号,对应 4 片 8K 芯片)。

(3)地址范围分析(主)

高速缓冲存储器(主)

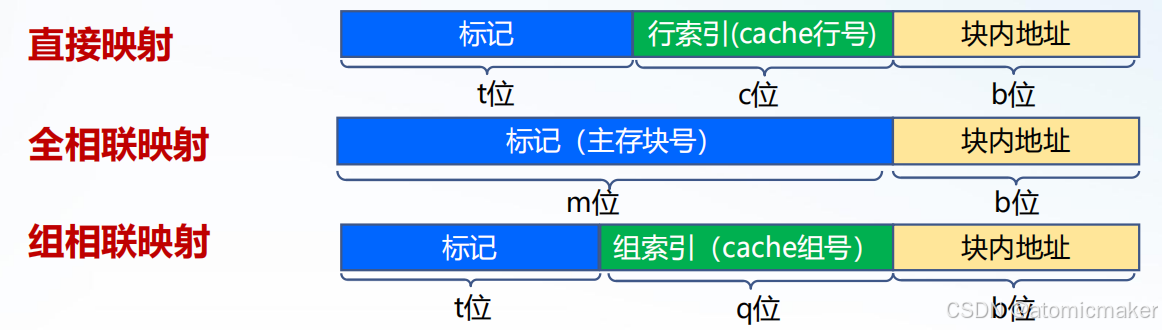

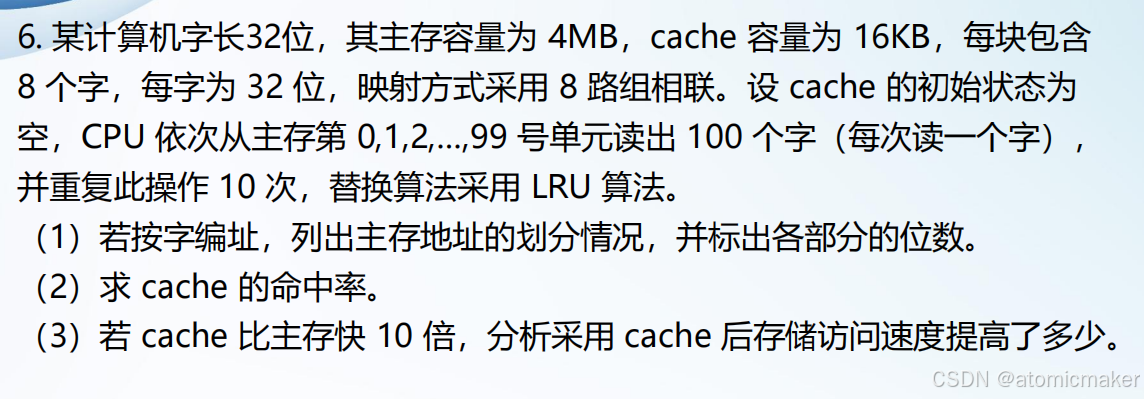

Cache 与主存的映射方式

1)直接映射(一对一)

2)全相联映射(多对多)

3)组相联映射(分组的直接映射)

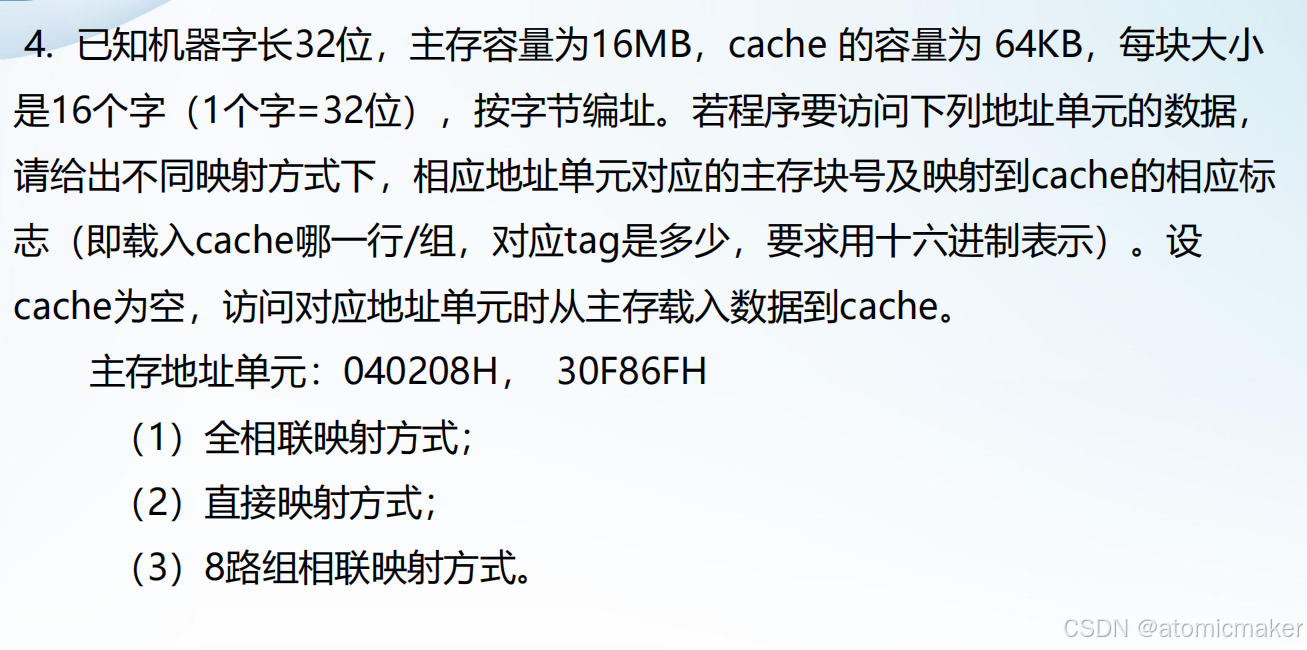

注意:主存块号的表示都是一样的。

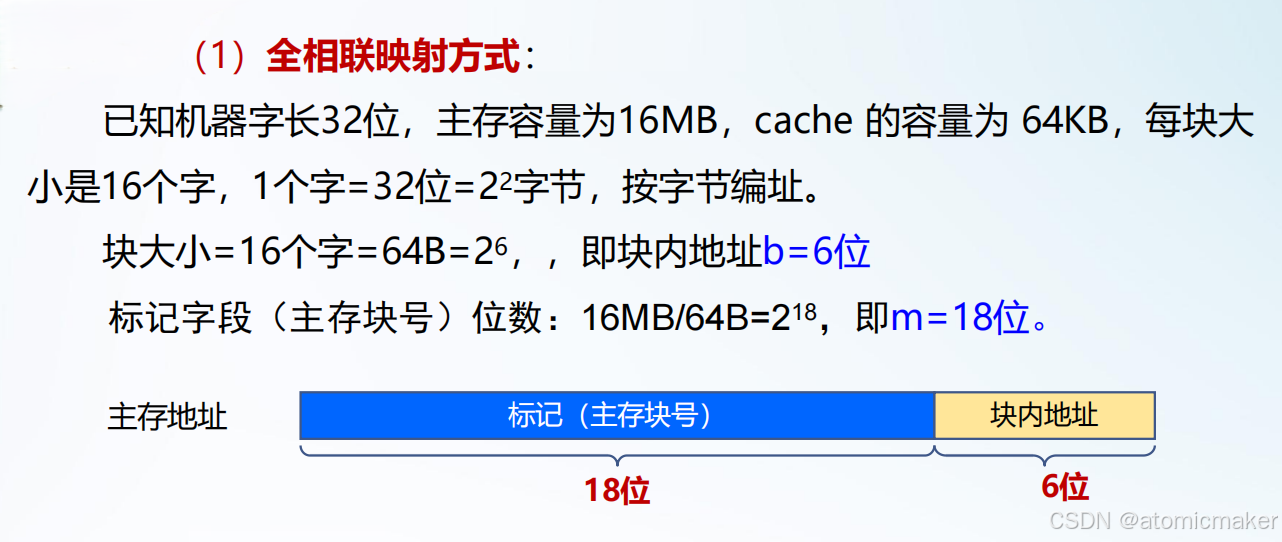

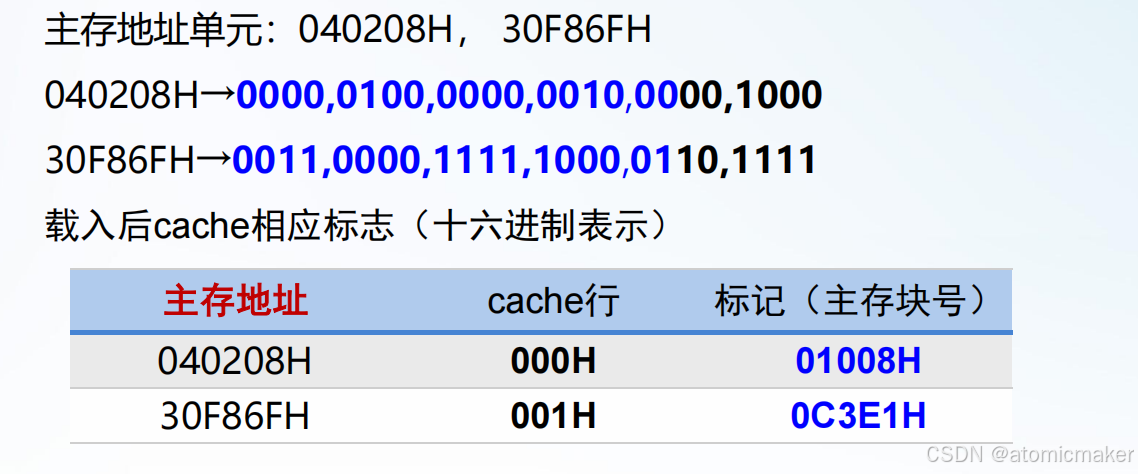

全相联映射方式:

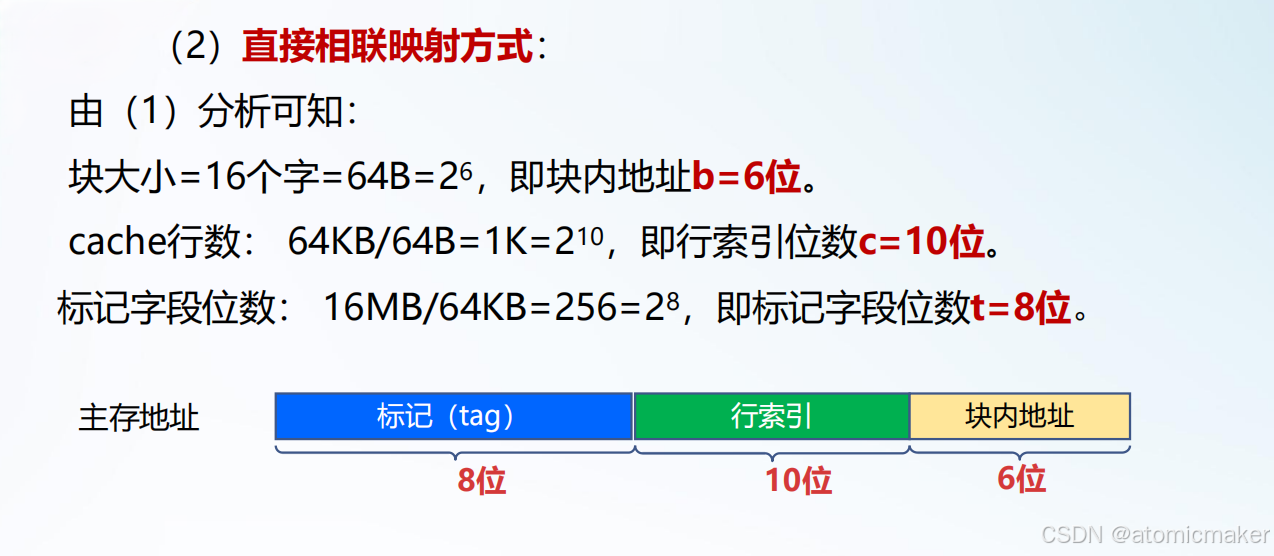

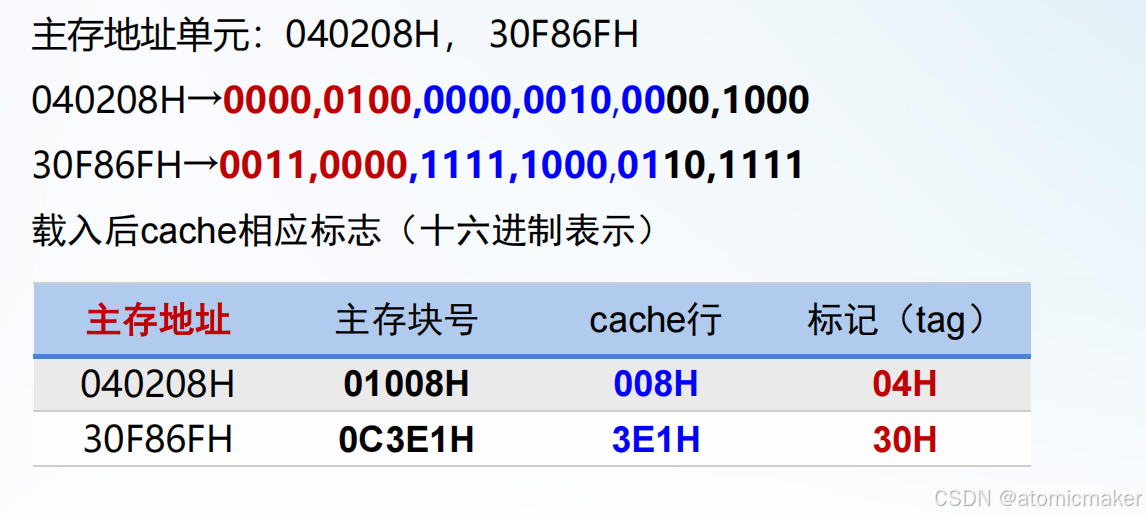

直接相联方式:

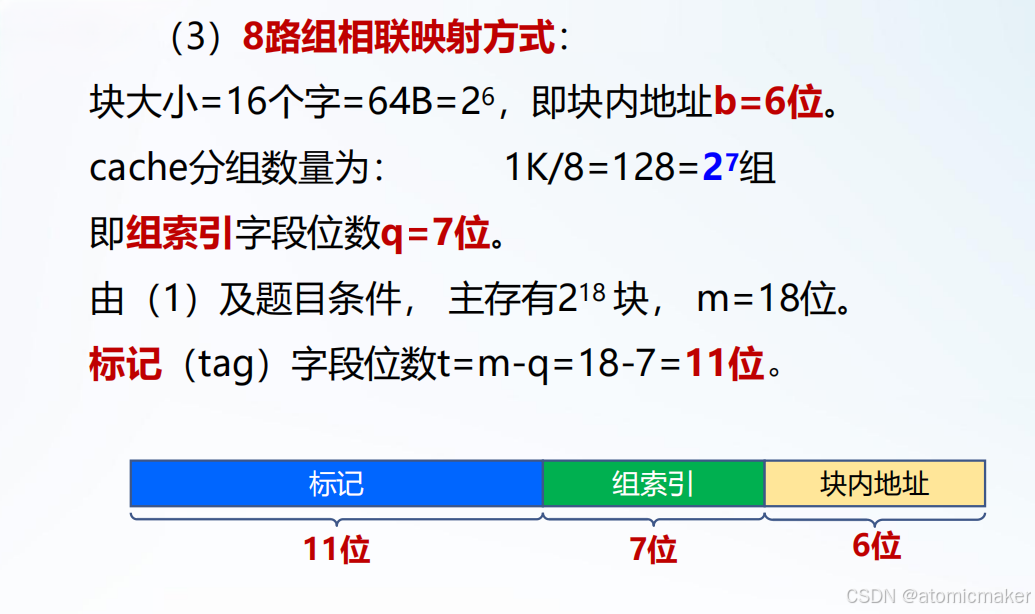

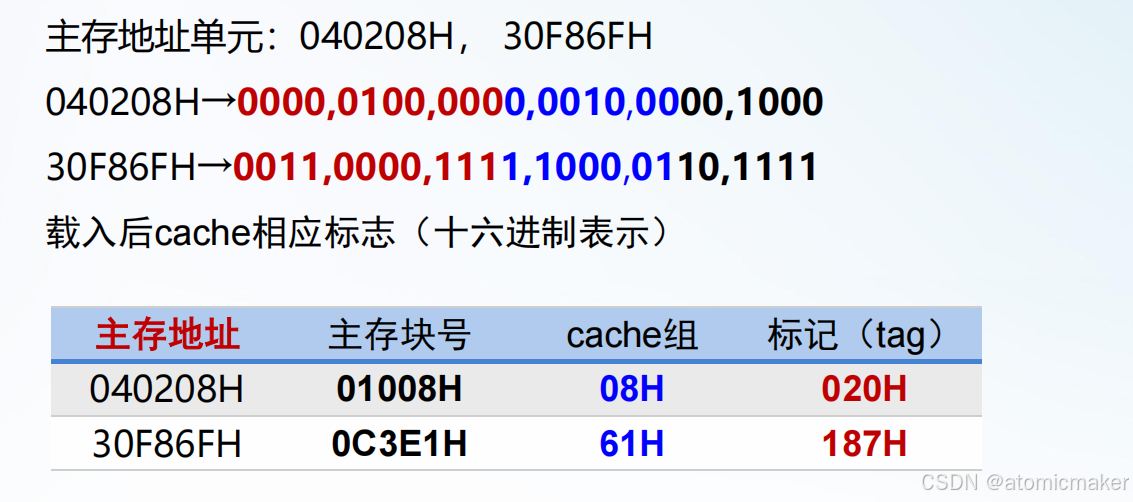

8路组相联映射方式:

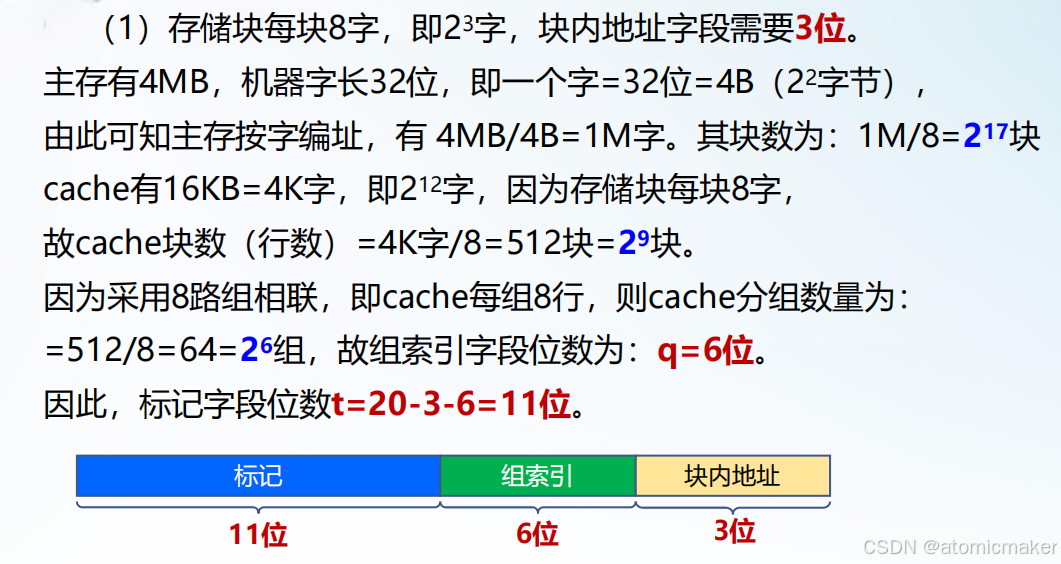

Cache 性能参数

1)命中率

CPU 访问的信息在 Cache 中的概率,是 Cache 性能的核心指标:

- Nc:Cache 命中的访问次数;Nm:Cache 未命中(缺失)的访问次数。

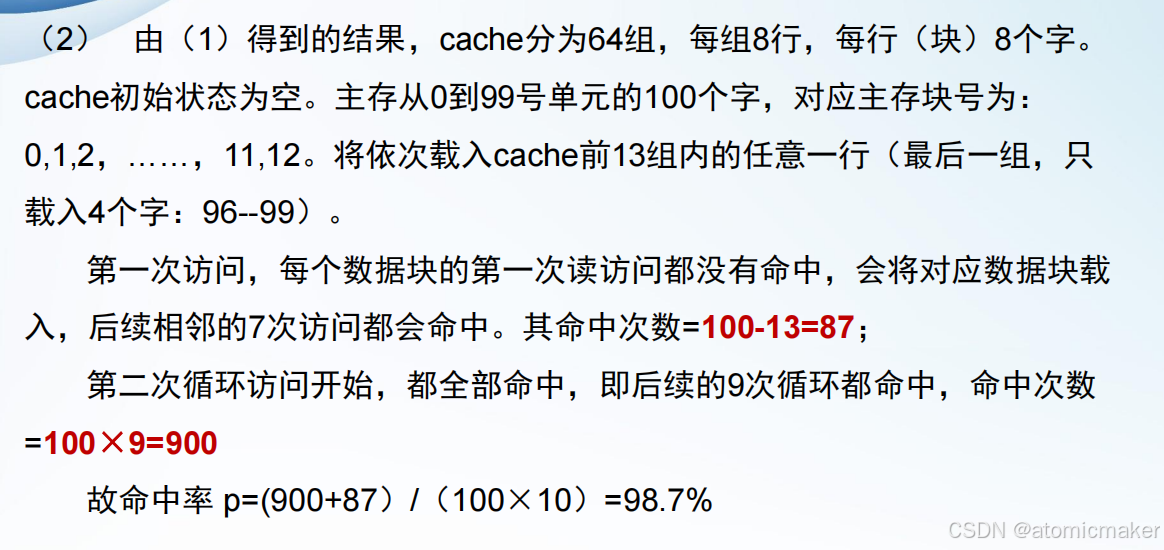

2)平均访问时间

CPU 访问储存器的平均时间,综合 Cache 和主存的访问时间:

- Tc:Cache 访问时间;Tm:主存访问时间。

3)访问效率

Cache 的有效利用率,反应 Cache 对访问速度的提升效果:

速度快10倍,则所需时间为 1/10

指令系统

指令系统设计

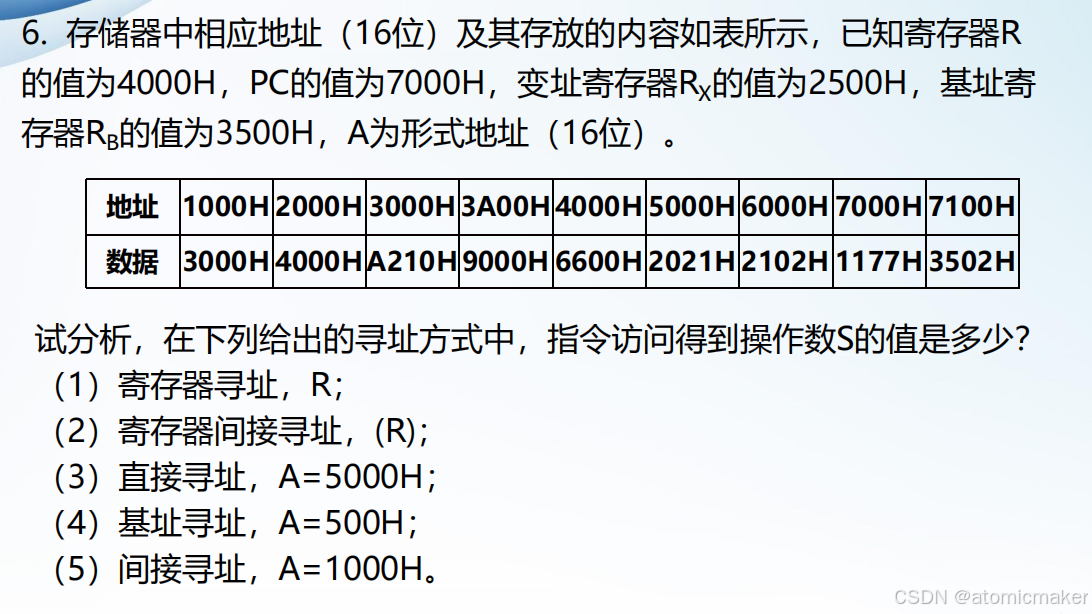

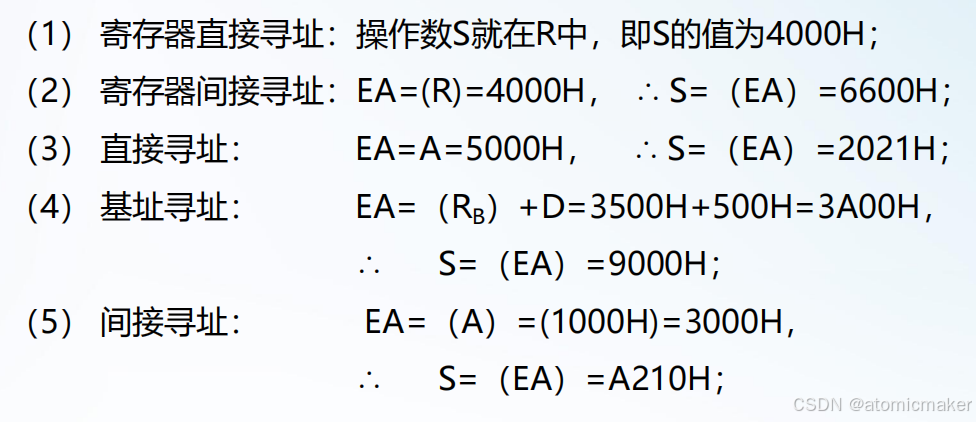

寻址方式

机器字长:n位,形式地址A:m位。

真正的操作数 S = (EA)。

| 寻址方式 | 有效地址(EA)计算 | 寻址范围 |

|---|---|---|

| 立即寻址 | A 就是操作数 | 由立即数字长决定 |

| 寄存器寻址 | EA= R | 由寄存器位数决定(如 5 位寄存器编号支持 32 个寄存器) |

| 直接寻址 | EA= A | |

| 间接寻址 | EA= (A) | |

| 寄存器间接寻址 | EA= (R) | |

| 变址寻址 | EA= (R)+A(R 为变址寄存器) | |

| 基址寻址 | EA= (R)+A(R 为基址寄存器) | |

| 相对寻址 | EA= (PC)+A(PC 为程序计数器) |

注意:R 表示的是寄存器,(R) 才是寄存器的值。

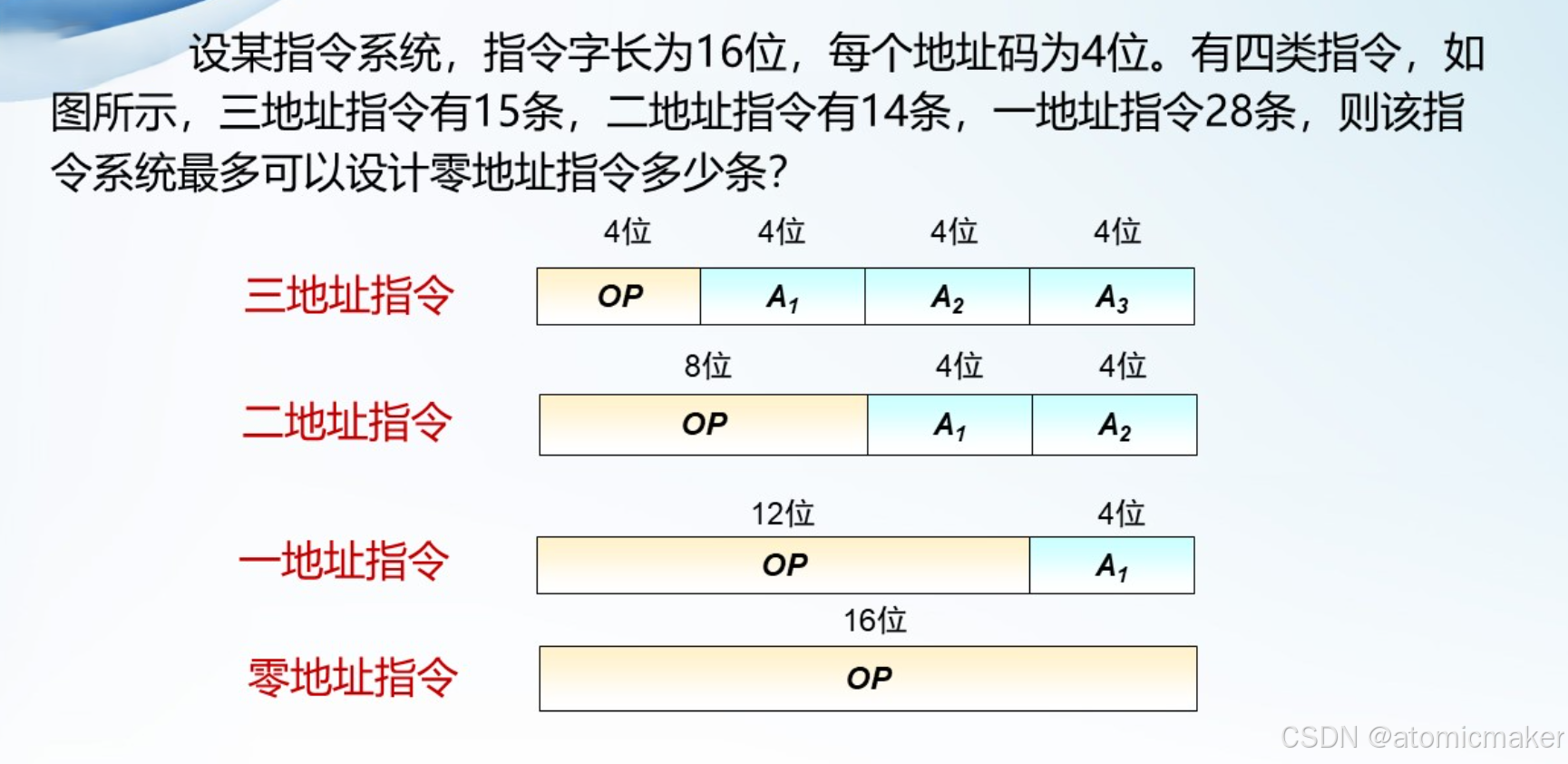

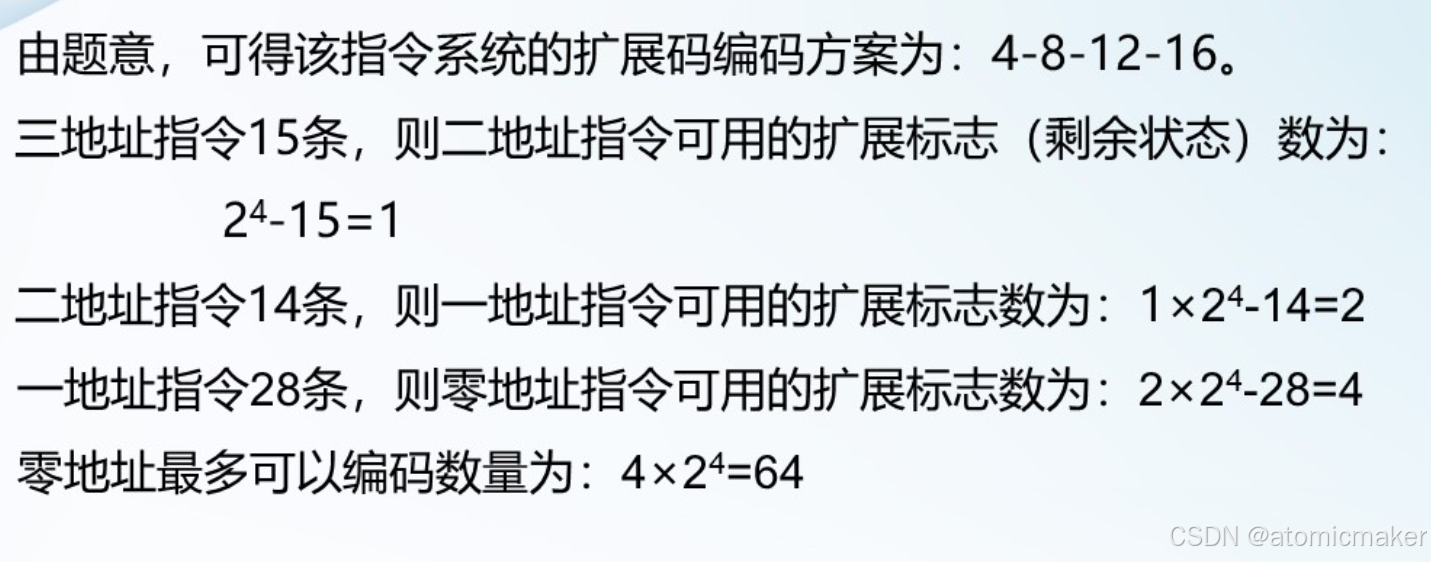

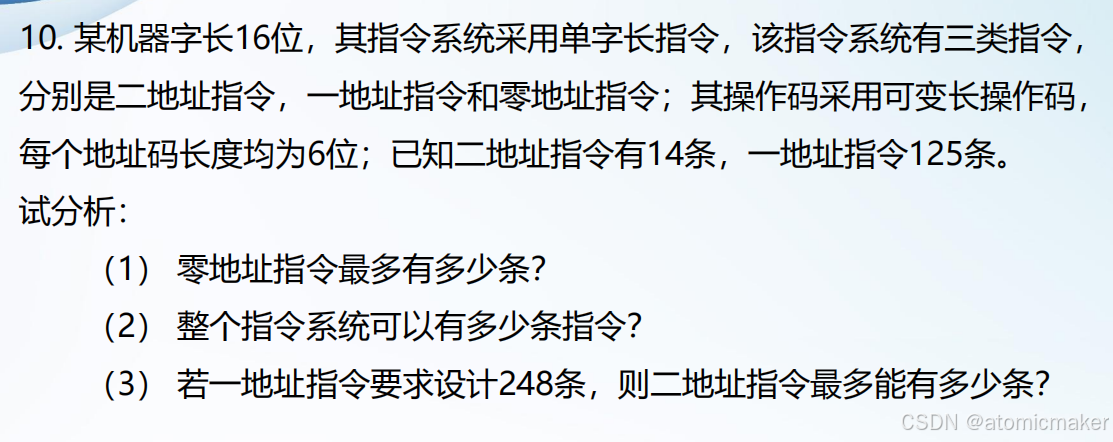

扩展操作码

基本原则:地址码位数越少,操作码位数越多。

中央处理器

CPU 是计算机的核心部件,负责指令的读取、译码、执行以及数据的运算和处理,其性能直接决定计算机的整体运行效率。

CPU概述(了解)

CPU 的核心功能

- 指令控制:从主存中按顺序读取指令(取指),保证指令按正确顺序执行。

- 操作控制:对指令进行译码,产生完成指令功能所需的控制信号,控制运算器、存储器、I/O 设备等协同工作。

- 数据加工:通过运算器(ALU)完成算术运算(加减乘除)和逻辑运算(与、或、非、移位)。

- 异常与中断处理:响应程序异常(如除零错误)和外部中断(如键盘输入),暂停当前程序并执行处理程序。

CPU的基本组成

| 组成部分 | 核心子部件 | 功能说明 |

|---|---|---|

| 运算器(ALU) | 算术逻辑单元、通用寄存器、移位器、状态寄存器 | 执行算术 / 逻辑运算; 暂存运算数据和结果; 记录运算状态标志(ZF、SF、OF、CF) |

| 控制器 | 程序计数器(PC)、指令寄存器(IR)、指令译码器、控制信号发生器 | PC:存放下一条要执行的指令地址; IR:存放当前正在执行的指令; 控制信号发生器:根据译码结果产生控制信号 |

| 寄存器组 | 通用寄存器(如 RISC-V 的 x0~x31)、专用寄存器(PC、IR、MAR、MDR) | 通用寄存器:高速暂存数据,减少访存次数; MAR(存储器地址寄存器):存放访存地址;MDR(存储器数据寄存器):存放访存数据 |

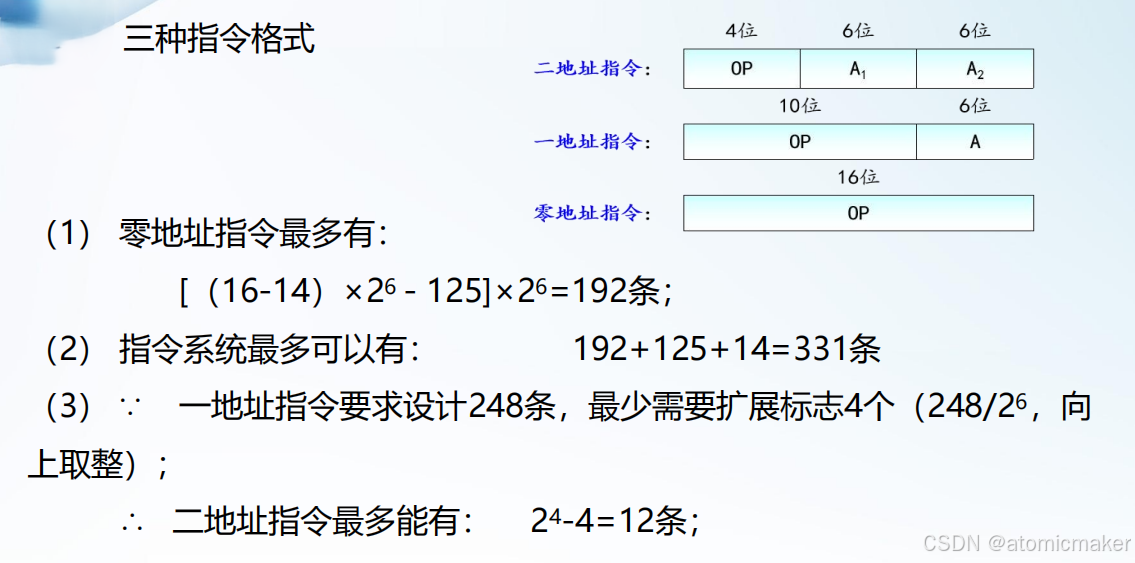

单周期CPU设计

9 条核心指令

关键控制信号说明

| 控制信号 | 说明 |

|---|---|

| Branch | 分支 |

| Jump | 跳转 |

| ALUASrc | 控制 ALU 的第二个操作数来源 |

| MemtoReg | 控制写回寄存器堆的数据来源 |

| RegWr | 寄存器堆写使能 |

| MemWr | 主存写使能 |

9 条指令对应的控制信号值

| 指令 | add | slt | sltu | ori | lui | lw | sw | beq | jal | |

|---|---|---|---|---|---|---|---|---|---|---|

| 控制信号 | ||||||||||

| Branch | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| Jump | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| ALUASrc | 0 | 0 | 0 | 0 | x | 0 | 0 | 0 | 1 | |

| MemtoReg | 0 | 0 | 0 | 0 | 0 | 1 | x | x | 0 | |

| RegWr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | |

| MemWr | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |

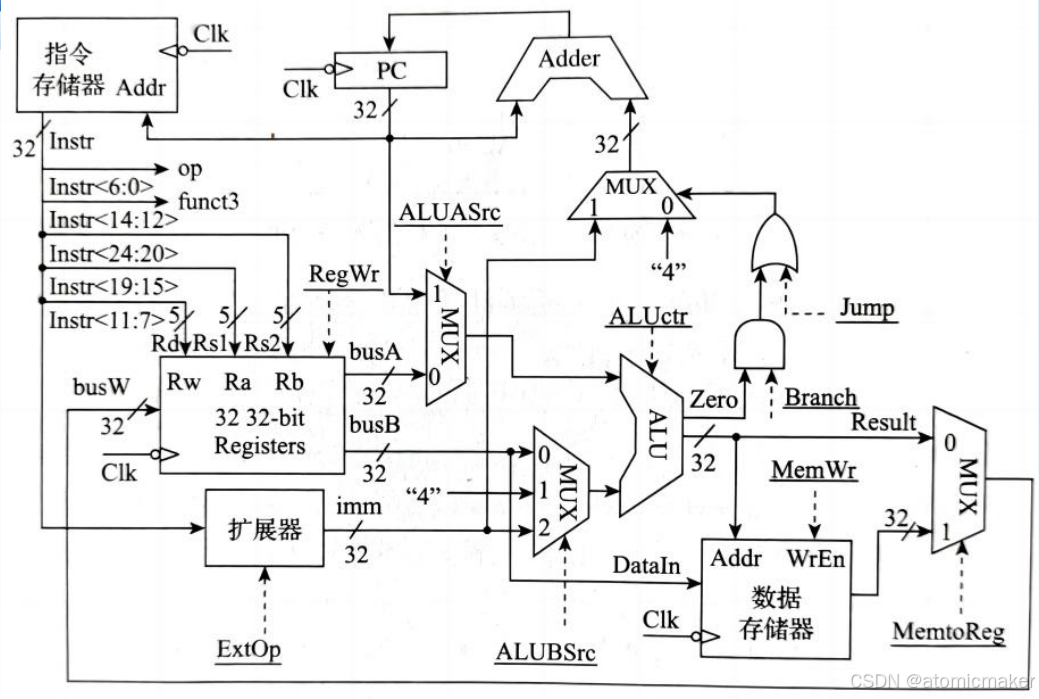

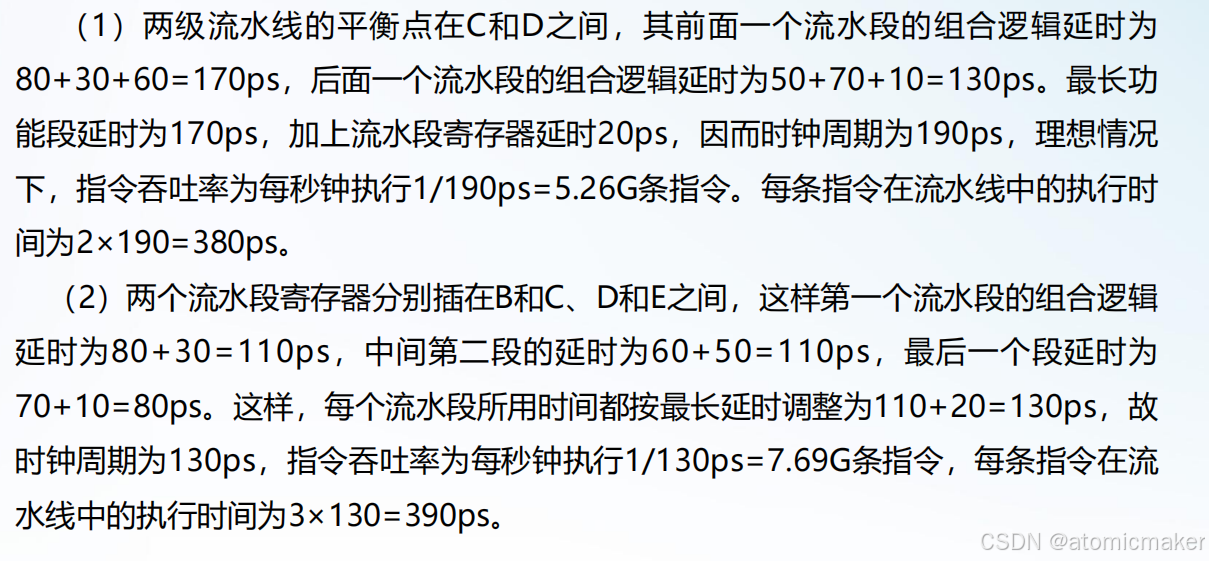

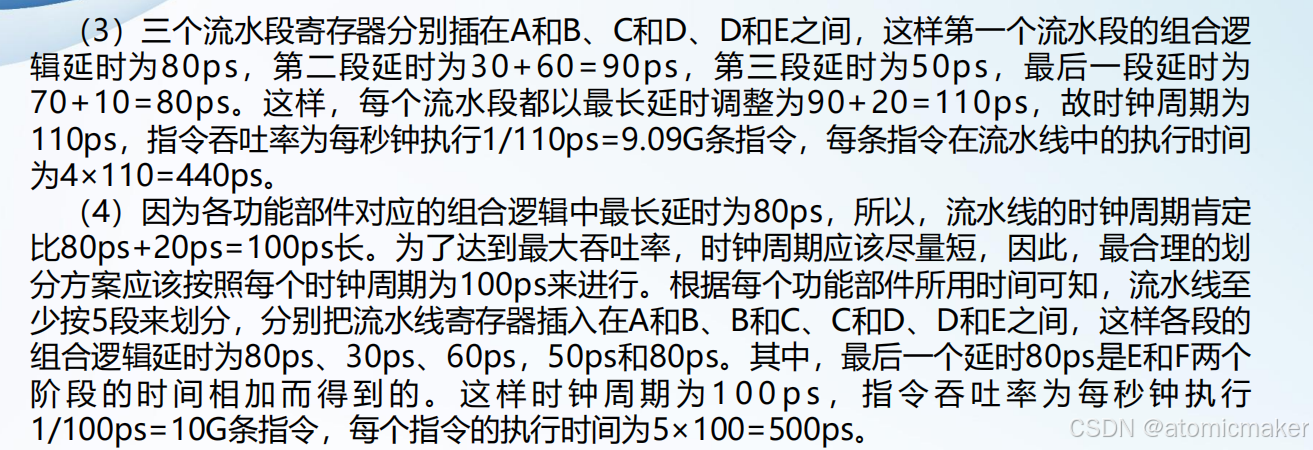

流水线CPU设计

流水线 CPU 的核心思想是将指令执行阶段重叠进行(划分为多个"流水段",段间插入寄存器,用于暂存中间结果),类似于工厂的流水线作业,从而提升 CPU 的指令吞吐量。

流水线性能指标

1)时钟周期

最长段延时 + 寄存器延时,是流水线的基本时间单位。

2)指令吞吐率

单位时间内完成的指令数,吞吐率 = 1/时钟周期

3)指令执行时间

执行时间 = 时钟周期 × 流水线级数

1792

1792

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?