注:本文为 “SPI 与 QSPI” 相关合辑。

图片清晰度受引文原图所限。

略作重排,如有内容异常,请看原文。

一、SPI 及衍生协议的基础定义

SPI(Serial Peripheral Interface,串行外围设备接口)是由 Motorola 公司提出的一种高速、全双工、同步串行通信总线,在嵌入式系统与外设通信场景中应用极为普遍。该总线采用主从架构,通信过程由主设备发起并控制,通过 4 组信号线完成数据交互,广泛应用于 EEPROM、Flash、RTC(实时时钟)、ADC(模数转换器)、DSP(数字信号处理器)以及数字信号解码器等外设。

SPI 协议包含 Standard SPI、Dual SPI 与 Queued SPI 三种接口类型,分别对应 3‑wire、4‑wire 与 6‑wire 硬件连接方式,Dual SPI 与 QSPI 均为 SPI 的衍生协议,通过扩展数据线宽度或复用引脚实现传输速率提升。

- Standard SPI:常规表述中的 SPI 即 Standard SPI,包含 4 根信号线,分别为 CLK、CS、MOSI 与 MISO,数据线工作在全双工模式,单个时钟周期内传输 1bit 数据。

- Dual SPI:仅适用于 SPI Flash 外设。SPI Flash 应用场景中,全双工传输模式的使用频率较低,因此对 MOSI 与 MISO 引脚功能进行扩展,使其工作在半双工模式。向 Dual SPI Flash 发送特定命令字节后,设备进入 dual mode,此时 MOSI 引脚切换为 SIO0(serial io 0),MISO 引脚切换为 SIO1(serial io 1),单个时钟周期内可完成 2 bit 数据的传输,实现数据传输速率的翻倍。

- QSPI:全称 Queued SPI,基于 Dual SPI 的扩展逻辑,针对 SPI Flash 外设新增 2 根 I/O 线(SIO2、SIO3),使单个时钟周期内的数据传输量提升至 4 bit,硬件架构为 6 线制。此外,Queued SPI 是一种集成队列功能的 SPI 衍生协议,允许主设备在 SPI 总线上预先排队多个数据传输请求,控制器将按照请求在队列中的先后顺序依次执行数据传输操作。

二、SPI 及衍生协议的硬件架构与引脚定义

2.1 SPI 硬件架构与引脚功能

SPI 硬件架构为 4 线全双工架构,主设备负责生成 SCLK 时钟信号与 CS 片选信号,通过 MOSI 向从设备发送数据,通过 MISO 接收从设备反馈数据;从设备被动响应主设备控制,仅在被选中(CS 低电平)时进行数据收发。MOSI 与 MISO 为单向引脚,避免收发冲突,硬件设计简单,适配多数通用外设。

各信号线的功能如下:

- SCK (Serial Clock):串行时钟线,由主设备向从设备传输时钟信号,用于控制数据交换的时机与速率。

- MOSI (Master Out Slave In):在 SPI 主设备端也被称为 Tx-channel,功能为 SPI 主设备向 SPI 从设备发送数据。

- CS/SS (Chip Select/Slave Select):片选信号线,功能为 SPI 主设备选择待通信的 SPI 从设备,低电平表示从设备被选中(低电平有效)。

- MISO (Master In Slave Out):在 SPI 主设备端也被称为 Rx-channel,功能为 SPI 主设备接收 SPI 从设备传输的数据。

2 个芯片利用 SPI 总线进行通信的结构示意图如下:

单主设备多从设备的典型结构如下图所示:

2.2 Dual SPI 硬件架构

Dual SPI 复用 SPI 的 MOSI 与 MISO 引脚为 SIO0 与 SIO1 双向引脚,无需新增硬件引脚(仍为 4 线)。通过模式切换命令,使 SIO0 与 SIO1 可同时发送或接收数据,实现单时钟周期 2 bit 传输。半双工模式下,同一时刻仅进行单向传输,避免双向冲突,硬件改动最小且速率翻倍。

2.3 QSPI 硬件架构

QSPI 在 Dual SPI 基础上,进一步复用 WP ‾ \overline{\text{WP}} WP(写保护)引脚为 IO2、 HOLD ‾ \overline{\text{HOLD}} HOLD(保持)引脚为 IO3,形成 4 路双向数据通道(IO0~IO3),硬件架构扩展为 6 线。专用 QSPI 控制器支持 SDR(单倍速率)与 DDR(双倍速率)模式,DDR 模式下时钟上升沿与下降沿均传输数据,速率较 SDR 模式再翻倍。

以某款 SPI FLASH 的引脚接口为例,该芯片同时支持 SPI、DSPI 与 QSPI 三种通信方式,其引脚接口示意图如下:

该芯片共包含 8 个功能引脚,各引脚的功能定义如下所示:

各引脚的详细功能描述如下:

- 片选信号(/CS):作用为使能或禁止设备的操作。当 CS 信号为高电平时,设备处于未选中状态,串行数据输出线(DO 或 IO0、IO1、IO2、IO3)均处于高阻态;当 CS 信号为低电平时,设备处于选中状态,FPGA 可向 QSPI Flash 发送数据,或从 QSPI Flash 接收数据。

- 串行数据输入信号(DI)与串行输出信号(DO):标准 SPI 协议中,串行时钟信号(SCLK)上升沿将串行输入信号(DI)上的数据写入 QSPI Flash,串行时钟信号(SCLK)下降沿将 QSPI Flash 内部数据串行化,并通过单向 DO 引脚输出。在 Dual SPI 与 Quad SPI 模式下,DI 与 DO 引脚均为双向信号,兼具数据输入与输出功能。

- 写保护信号(/WP):作用为防止 QSPI Flash 状态寄存器被写入错误数据,/WP 信号为低电平有效。当状态寄存器 2 的 QE 位被置 1 时,/WP 信号的写保护功能失效,该引脚切换为 Quad SPI 模式下的双向数据传输信号。

- 保持信号(/HOLD):作用为暂停 QSPI Flash 的操作。当 /HOLD 信号为低电平且 CS 信号为低电平时,串行输出信号(DO)处于高阻态,串行输入信号(DI)与串行时钟信号(SCLK)被 QSPI Flash 忽略;当 /HOLD 信号被拉高后,QSPI Flash 可继续执行读写操作。当多个 SPI 设备共享同一组 SPI 总线信号时,可通过 /HOLD 信号切换信号流向。与 /WP 信号类似,当状态寄存器 2 的 QE 位被置 1 时,/HOLD 信号的保持功能失效,该引脚同样切换为 Quad SPI 模式下的双向数据传输信号。

- 串行时钟线(SCLK):用于为串行输入输出操作提供同步时钟信号。

以 W25Q128BV 型号的 Quad SPI Flash 存储器为例,其顶视图(Top View)如下图所示:

该芯片共包含 8 个功能管脚,各管脚的功能定义如下图所示:

W25Q128BV 芯片的内部结构框图如下图所示:

开发板上 QSPI Flash 的硬件原理图如下图所示:

2.4 三种协议硬件参数对比

| 参数维度 | SPI(标准) | Dual SPI(DSPI) | QSPI(Quad SPI) |

|---|---|---|---|

| 信号线配置 | 4 线:CS(片选)、SCLK(时钟)、MOSI(主出从入,单向)、MISO(主入从出,单向) | 4 线:CS、SCLK、SIO0(双向)、SIO1(双向) | 6 线:CS、SCLK、IO0(双向)、IO1(双向)、IO2(双向,复用 WP ‾ \overline{\text{WP}} WP)、IO3(双向,复用 HOLD ‾ \overline{\text{HOLD}} HOLD) |

| 通信模式 | 全双工,单时钟周期传输 1 bit | 半双工,单时钟周期传输 2 bit | 半双工,单时钟周期传输 4 bit;支持 DDR 模式(时钟上下沿均传输,速率再翻倍) |

| 理论传输速率 | 1×时钟频率(如 10 MHz 时钟对应 10 Mbps) | 2×时钟频率(如 10 MHz 时钟对应 20 Mbps) | 4×时钟频率(如 10 MHz 时钟对应 40 Mbps);DDR 模式可达 8× |

| 模式切换方式 | 无需切换,默认工作模式 | 主设备发送专用命令字节进入 Dual 模式 | 主设备发送专用命令字节,且需将状态寄存器 QE 位置 1 启用 4 线传输 |

| 硬件资源需求 | 普通 SPI 控制器即可 | 支持半双工的 SPI 控制器 | 专用 QSPI 控制器,支持 4 线时序与内存映射等扩展功能 |

| 数据传输方向 | 收发独立,同时双向传输 | 同一方向并行传输,仅支持半双工 | 同一方向并行传输,仅支持半双工 |

| 协议复杂度 | 低,命令格式简单,无额外周期要求 | 中,需处理双线指令解析与数据对齐 | 高,需处理四线指令、dummy 周期、FIFO 配置及内存映射等 |

| 典型应用场景 | 通用外设(ADC、DAC、传感器、LCD 等)、低速率 SPI Flash 读写 | SPI Flash 批量读取、中等速率存储访问、成本敏感型高速需求场景 | 高速 NOR Flash、XIP(执行在原地)内存映射、双闪存并行访问、大容量快速存储 |

三、SPI 及衍生协议的时序特性

3.1 SPI 总线传输模式

SPI 总线传输共包含 4 种模式,由时钟极性(CPOL)与时钟相位(CPHA)两个参数共同定义。其中,CPOL 参数规定 SCLK 时钟信号空闲状态的电平,CPHA 参数规定数据在 SCLK 时钟的上升沿还是下降沿被采样。4 种模式的时序图如下图所示:

4 种传输模式的具体定义如下:

- 模式 0: CPOL = 0 \text{CPOL}=0 CPOL=0, CPHA = 0 \text{CPHA}=0 CPHA=0。SCK 串行时钟线空闲状态为低电平,数据在 SCK 时钟的上升沿被采样,数据在 SCK 时钟的下降沿切换。

- 模式 1: CPOL = 0 \text{CPOL}=0 CPOL=0, CPHA = 1 \text{CPHA}=1 CPHA=1。SCK 串行时钟线空闲状态为低电平,数据在 SCK 时钟的下降沿被采样,数据在 SCK 时钟的上升沿切换。

- 模式 2: CPOL = 1 \text{CPOL}=1 CPOL=1, CPHA = 0 \text{CPHA}=0 CPHA=0。SCK 串行时钟线空闲状态为高电平,数据在 SCK 时钟的下降沿被采样,数据在 SCK 时钟的上升沿切换。

- 模式 3: CPOL = 1 \text{CPOL}=1 CPOL=1, CPHA = 1 \text{CPHA}=1 CPHA=1。SCK 串行时钟线空闲状态为高电平,数据在 SCK 时钟的上升沿被采样,数据在 SCK 时钟的下降沿切换。

上述 4 种模式中,模式 0 与模式 3 为常用模式。模式 0 下的 SPI 时序图如下:

上图明确显示,模式 0 下 SCK 串行时钟线的空闲状态为低电平;当片选信号 SS 被主设备拉低后,数据传输启动;数据线 MOSI 与 MISO 的数据切换(Toggling)发生在时钟下降沿(上图黑色虚线位置);数据线 MOSI 与 MISO 的数据采样(Sampling)发生在时钟周期的中间时刻(上图灰色实线位置)。下图清晰描述其余 3 种模式下,数据线 MOSI 与 MISO 的数据切换位置与数据采样位置的对应关系:

SPI 主从结构内部的数据传输示意图如下图所示:

3.2 三种协议时序参数对比

三种协议均遵循 SPI 的 CPOL(时钟极性)与 CPHA(时钟相位)时序规则,仅通过数据线扩展提升速率,以下时序分析均基于最常用的模式 0(CPOL=0,CPHA=0)。

| 时序参数 | SPI(标准,0x0B Fast Read) | Dual SPI(0xBB Dual I/O Fast Read) | QSPI(0xEB Quad I/O Fast Read) |

|---|---|---|---|

| 数据采样沿 | SCLK 上升沿 | SCLK 上升沿 | SCLK 上升沿 |

| 数据更新沿 | SCLK 下降沿 | SCLK 下降沿 | SCLK 下降沿 |

| 时钟空闲电平 | 低电平 | 低电平 | 低电平 |

| 命令传输线数 | 1 线(MOSI) | 1 线(SIO0) | 1 线(IO0) |

| 地址传输线数 | 1 线(MOSI) | 2 线(SIO0/SIO1) | 4 线(IO0~IO3) |

| 数据传输线数 | 1 线(MISO) | 2 线(SIO0/SIO1) | 4 线(IO0~IO3) |

| dummy 周期数 | 8 个(用于 Flash 数据准备) | 8 个 | 8 个(可通过 DCYC 字段配置) |

| 模式兼容性 | 支持 4 种标准 SPI 模式 | 兼容 SPI 时序,仅扩展传输宽度 | 兼容 SPI/Dual SPI 时序,含专用扩展周期 |

3.3 典型时序波形说明

3.3.1 SPI(0x0B Fast Read)时序

波形流程:

- 主设备拉低 CS,启动通信;

- 主设备通过 MOSI 逐位发送 0x0B 命令(8 bit);

- 主设备通过 MOSI 发送 24 bit 地址(高位在前);

- 主设备发送 8 个 dummy 时钟周期(Flash 内部准备数据,此时 MISO 电平无效);

- 从设备通过 MISO 逐位输出数据,主设备在 SCLK 上升沿采样;

- 数据传输完成,主设备拉高 CS,停止通信。

关键特征:命令、地址由 MOSI 单向发送,数据由 MISO 单向接收,全双工传输,单时钟周期仅传输 1 bit。

3.3.2 Dual SPI(0xBB Dual I/O Fast Read)时序

波形流程:

- 主设备拉低 CS,通过 SIO0(原 MOSI)发送 0xBB 命令(单线传输);

- 切换至双线模式,主设备通过 SIO0/SIO1 并行发送 24 bit 地址(每时钟周期传输 2 bit);

- 执行 8 个 dummy 时钟周期(双线传输);

- 从设备通过 SIO0/SIO1 并行输出数据,主设备在 SCLK 上升沿采样;

- 主设备拉高 CS,结束通信。

关键特征:命令阶段单线传输,地址与数据阶段双线并行传输,半双工模式,单时钟周期传输 2 bit,速率较 SPI 翻倍。

3.3.3 QSPI(0xEB Quad I/O Fast Read)时序

波形流程:

- 主设备拉低 CS,通过 IO0(原 MOSI)发送 0xEB 命令(单线传输);

- 切换至四线模式,主设备通过 IO0~IO3 并行发送 24 bit 地址(每时钟周期传输 4 bit);

- 执行 8 个 dummy 时钟周期(四线传输,Flash 准备数据);

- 从设备通过 IO0~IO3 并行输出数据,主设备在 SCLK 上升沿采样;

- 主设备拉高 CS,结束通信。

QSPI 四线模式下的读命令时序如下图所示:

关键特征:命令阶段单线传输,地址与数据阶段四线并行传输,半双工模式,单时钟周期传输 4 bit;DDR 模式下,时钟上升沿与下降沿均传输数据,速率再翻倍。

3.4 时序参数计算示例

以 QSPI 50 MHz 时钟(周期 T=20 ns)、读取 256 字节数据为例:

- 命令传输时间:1 字节×8 时钟×20 ns=160 ns;

- 地址传输时间:24 位÷4 位/时钟×20 ns=120 ns;

- dummy 周期时间:8 时钟×20 ns=160 ns;

- 数据传输时间:256 字节×8 位/字节÷4 位/时钟×20 ns=102.4 μs;

- 总耗时:160 ns+120 ns+160 ns+102400 ns≈103 μs。

同理可计算 SPI(总耗时≈410 μs)与 Dual SPI(总耗时≈205 μs)的传输时间,验证速率提升效果。

四、QPSI 具体协议内容

4.1 QSPI 工作模式

QSPI 接口支持以下三种工作模式:

- 间接模式:通过配置 QSPI 相关寄存器执行全部操作,适用于单次数据量较小的读写场景。

- 状态轮询模式:周期性读取外部 Flash 状态寄存器,当特定标志位被置 1 时触发中断(例如擦除或烧写操作完成时,设备将产生中断信号),无需 CPU 持续查询,适合监控耗时较长的存储操作。

- 内存映射模式:将外部 Flash 映射至微控制器的地址空间,系统可将其视为内部存储器进行访问,无需执行复杂的 SPI 命令,适合 XIP 应用(如程序直接在 Flash 中运行)。

采用双闪存模式时,可同时访问 2 片 Quad‑SPI Flash,数据吞吐量与存储容量均可提升至原来的 2 倍。

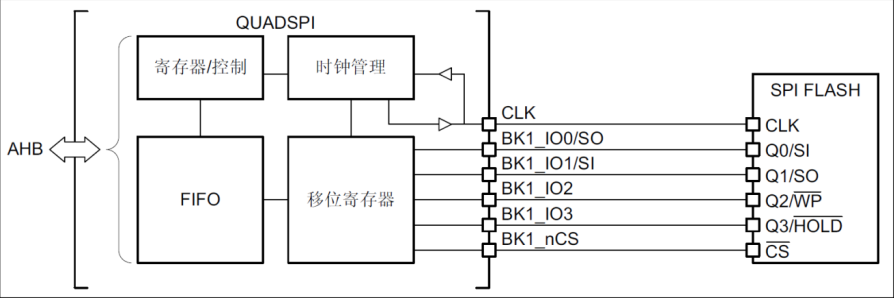

QSPI 功能框图(双闪存模式禁用状态)如下所示:

QSPI 通过 6 路信号与 Flash 建立连接,分别为 4 路数据线(BK1_IO0~BK1_IO3)、1 路时钟输出信号(CLK)与 1 路片选输出信号(低电平有效,BK1_nCS),各信号的功能介绍如下:

- BK1_nCS:片选输出信号(低电平有效),适用于 FLASH 1。若 QSPI 始终工作在双闪存模式下,该信号也可作为 FLASH 2 的从设备选择信号线。QSPI 通信以 BK1_nCS 信号拉低为起始标志,以 BK1_nCS 信号拉高为结束标志。

- CLK:时钟输出信号,适用于 2 片存储器,用于实现通信数据的同步。该信号由通信主机产生,其频率决定通信速率。不同设备支持的最高时钟频率存在差异,例如 STM32 系列芯片的 QSPI 时钟频率最大值为 f P C L K / 2 f_{PCLK}/2 fPCLK/2。多设备通信场景中,通信速率由低速设备的性能上限决定。

- BK1_IO0:双线/四线模式下为双向 I/O 接口,单线模式下为串行输出接口,适用于 FLASH 1。

- BK1_IO1:双线/四线模式下为双向 I/O 接口,单线模式下为串行输入接口,适用于 FLASH 1。

- BK1_IO2:四线模式下为双向 I/O 接口,适用于 FLASH 1。

- BK1_IO3:四线模式下为双向 I/O 接口,适用于 FLASH 1。

STM32F7 的 QSPI 接口结构示意图如下:

4.2 QSPI 工作状态

可通过寄存器配置选择 QSPI 的通信传输方式。执行四线读写操作(QSPI 模式)前,需将寄存器中的 QE(Quad Enable)位配置为 1。此外,执行四线读操作时,需在读取数据前等待 8 个 dummy clock 周期,以提升数据读取速度(具体参数需参考对应芯片的数据手册)。因此,相较于单线操作,四线操作除需新增四线模式下的读写数据状态外,还需新增写状态寄存器功能(用于将 QE 位配置为 1)与 dummy 状态(用于等待 8 个 clock 周期)。

四线模式包含以下工作状态:

- 空闲状态:完成各寄存器的初始化配置。

- 发送命令状态:发送 8 bit 命令码。

- 发送地址状态:发送 24 bit 地址码。

- 读等待状态(单线模式):读数据操作执行过程中,设备进入该状态等待操作完成。

- 写数据状态(单线模式):FPGA 通过单线模式向 QSPI Flash 写入数据。

- 写状态寄存器状态:将状态寄存器的 QE(Quad Enable)位配置为 1。

- Dummy Clock 状态:四线读数据操作执行前,等待 8 个 dummy clock 周期。

- 写数据状态(四线模式):FPGA 通过四线模式向 QSPI Flash 写入数据。

- 读等待状态(四线模式):FPGA 通过四线模式从 QSPI Flash 读取数据过程中,等待操作完成。

- 结束状态:单条指令操作执行完毕,设备输出结束标志。

其中状态 6~状态 9 为四线模式相较于单线模式新增的工作状态。

4.3 QSPI 命令序列

QSPI 通过命令与 Flash 进行通信,每条命令包含指令、地址、交替(复用)字节、空指令与数据五个阶段,任一阶段均可跳过,但命令序列需至少包含指令、地址、交替字节或数据四个阶段中的一个。片选信号 nCS 在每条指令执行前拉低,在指令执行完成后拉高。

-

指令阶段

该阶段将 QSPI_CCR[7:0] 寄存器 instruction 字段中配置的 8 位指令发送至 Flash,用于指定待执行操作的类型。多数 Flash 设备在单线 SPI 模式下仅能通过 IO0/SO 信号以 1 bit/次的方式接收指令,但指令阶段可选择以 2 bit/次(双线 SPI 模式,通过 IO0/IO1 传输)或 4 bit/次(四线 SPI 模式,通过 IO0/IO1/IO2/IO3 传输)的方式发送指令。传输模式可通过 QSPI_CCR[9:8] 寄存器的 IMODE[1:0] 字段进行配置。若 IMODE = 00,则跳过指令阶段,命令序列从地址阶段开始执行(若地址阶段存在)。

-

地址阶段

该阶段向 Flash 发送 1~4 字节的地址数据,用于指示操作的目标地址。待发送地址的字节数通过 QSPI_CCR[13:12] 寄存器的 ADSIZE[1:0] 字段进行配置。间接模式与自动轮询模式下,待发送的地址字节存储在 QSPI_AR 寄存器的 ADDRESS[31:0] 字段中;内存映射模式下,地址由 AHB 总线直接提供(数据来源为内核或 DMA)。地址阶段的数据传输可选择 1 bit/次(单线 SPI 模式,通过 SO 传输)、2 bit/次(双线 SPI 模式,通过 IO0/IO1 传输)或 4 bit/次(四线 SPI 模式,通过 IO0/IO1/IO2/IO3 传输)的方式,具体模式通过 QUADSPI_CCR[11:10] 寄存器的 ADMODE[1:0] 字段进行配置。若 ADMODE = 00,则跳过地址阶段,命令序列直接进入下一阶段(若下一阶段存在)。 -

交替字节阶段

该阶段向 Flash 发送 1~4 字节的交替数据,通常用于配置设备的工作模式。待发送交替字节的数量通过 QSPI_CCR[17:16] 寄存器的 ABSIZE[1:0] 字段进行配置,待发送的数据存储在 QSPI_ABR 寄存器中。交替字节阶段的数据传输可选择 1 bit/次(单线 SPI 模式,通过 SO 传输)、2 bit/次(双线 SPI 模式,通过 IO0/IO1 传输)或 4 bit/次(四线 SPI 模式,通过 IO0/IO1/IO2/IO3 传输)的方式,具体模式通过 QSPI_CCR[15:14] 寄存器的 ABMODE[1:0] 字段进行配置。若 ABMODE = 00,则跳过交替字节阶段,命令序列直接进入下一阶段(若下一阶段存在)。

部分应用场景中,交替字节阶段仅需发送 1 个半字节而非 1 个完整字节,例如双线模式下仅通过 2 个时钟周期发送交替字节。此类场景下,固件可配置为四线模式(ABMODE = 11)并发送 1 个字节,具体操作为将 ALTERNATE 寄存器的 bit 7 与 bit 3 置 1(IO3 保持高电平),bit 6 与 bit 2 置 0(IO2 保持低电平)。此时,待发送半字节的高 2 位存储在 ALTERNATE 寄存器的 bit 4:3 字段,低 2 位存储在 bit 1 和 bit 0 字段。例如,若需通过 IO0/IO1 发送半字节数据 2(二进制 0010),则需将 ALTERNATE 寄存器配置为 0x8A(二进制 1000_1010)。

-

空指令周期阶段

该阶段在指定的 1~31 个时钟周期内不进行数据的发送或接收,目的是在高频时钟工作条件下,为 Flash 预留足够的时间以完成数据阶段的准备工作。空指令周期的数量通过 QSPI_CCR[22:18] 寄存器的 DCYC[4:0] 字段进行配置。SDR 与 DDR 模式下,空指令周期的持续时间以完整时钟周期为单位进行计量。若 DCYC = 0,则跳过空指令周期阶段,命令序列直接进入数据阶段(若数据阶段存在)。空指令周期阶段的操作模式由 DMODE 字段确定。为确保数据信号从输出模式切换至输入模式时有足够的周转时间,双线与四线模式下从 Flash 接收数据时,需至少配置 1 个空指令周期。 -

数据阶段

该阶段可从 Flash 接收任意数量的字节数据,或向 Flash 发送任意数量的字节数据。间接模式与自动轮询模式下,待发送/接收数据的字节数通过 QSPI_DLR 寄存器进行配置。间接写入模式下,需将待发送至 Flash 的数据写入 QSPI_DR 寄存器;间接读取模式下,通过读取 QSPI_DR 寄存器可获取从 Flash 接收的数据。内存映射模式下,读取的数据通过 AHB 总线直接传输至 Cortex 内核或 DMA。数据阶段的数据传输可选择 1 bit/次(单线 SPI 模式,通过 SO 传输)、2 bit/次(双线 SPI 模式,通过 IO0/IO1 传输)或 4 bit/次(四线 SPI 模式,通过 IO0/IO1/IO2/IO3 传输)的方式,具体模式通过 QUADSPI_CCR[15:14] 寄存器的 ABMODE[1:0] 字段进行配置。若 DMODE = 00,则跳过数据阶段,命令序列在 nCS 信号拉高时立即结束。该配置仅适用于间接写入模式。

4.4 常用命令码对照表

三种协议的命令体系均基于 SPI Flash 标准指令集,差异在于数据传输阶段的线数配置,擦除、状态查询等基础命令在三种协议中通用。以下指令码以 W25Qxx、GD25Qxx 系列 SPI Flash 为例,实际使用需以具体芯片手册为准。

| 操作类型 | SPI(标准) | Dual SPI(DSPI) | QSPI(Quad SPI) | 命令功能说明 |

|---|---|---|---|---|

| 读操作 | 0x03(Read Data)、0x0B(Fast Read) | 0x3B(Dual Output Fast Read)、0xBB(Dual I/O Fast Read) | 0x6B(Quad Output Fast Read)、0xEB(Quad I/O Fast Read) | 0x03:标准单线读,无 dummy 周期; 0x0B/3B/6B:带 dummy 周期的高速读; 0xBB/EB:地址与数据均采用双/四线传输,速率最优 |

| 写操作 | 0x02(Page Program) | 0xA2(Dual Input Page Program) | 0x32(Quad Input Page Program) | 页编程操作,单次最多写入 256 字节; DSPI/QSPI 通过双/四线并行写入数据,提升写入速率; 写入前需先执行写使能命令 |

| 擦除操作 | 0x20(Sector Erase,4KB)、0xD8(Block Erase,64KB)、0xC7(Chip Erase) | 同 SPI(擦除指令与传输线数无关) | 同 SPI(擦除指令与传输线数无关) | 擦除后数据为全 1; 扇区/块擦除适用于局部数据更新,整片擦除适用于批量初始化; 擦除前需执行写使能命令 |

| 模式切换 | - | 0x38(Enter Dual I/O Mode)、0x01(写状态寄存器,置位双工使能位) | 0x38(Enter Quad I/O Mode)、0x01(写状态寄存器 2,置 QE=1) | 模式切换前需执行写使能; QSPI 需通过 0x01 命令配置状态寄存器 2 的 QE 位,将 WP ‾ \overline{\text{WP}} WP/ HOLD ‾ \overline{\text{HOLD}} HOLD复用为 IO2/IO3 |

| 状态查询 | 0x05(Read Status Register 1)、0x35(Read Status Register 2) | 同 SPI | 同 SPI | 读取状态寄存器获取设备状态: BUSY 位(bit 0)表示是否忙,WEL 位(bit 1)表示写使能是否生效,QE 位(状态寄存器 2 bit 1)表示 QSPI 模式是否启用 |

| 设备识别 | 0x90(JEDEC ID Read)、0xAB(Release Power-Down) | 0x92(Dual JEDEC ID Read) | 0x94(Quad JEDEC ID Read) | 读取厂商 ID、设备 ID 等信息; DSPI/QSPI 通过双/四线并行输出 ID 数据,提升识别效率 |

| 写使能 | 0x06(Write Enable) | 0x06(Write Enable) | 0x06(Write Enable) | 所有写操作、擦除操作、模式切换操作前必须执行的前置命令,用于置位 WEL 位(写使能锁存) |

五、SPI 及 QSPI 开发实践

5.1 通用初始化准备(以 STM32 为例)

前置条件:

- 硬件连接正常(QSPI 6 线:CS/PB6、CLK/PB2、IO0/PB10、IO1/PB11、IO2/PB12、IO3/PB13);

- MCU 时钟初始化完成,PCLK2 频率为 100 MHz;

- W25Q128BV 状态寄存器 2 的 QE 位已置 1(启用四线模式)。

5.1.1 时钟与引脚配置

目标:配置 QSPI 相关 GPIO 为复用功能,确保时钟信号稳定、引脚电平正常。

- GPIO 配置:

- 将 CS、CLK、IO0~IO3 引脚配置为复用功能 AF10(STM32 系列 QSPI 对应的复用功能);

- 输出类型:推挽输出(PP),确保电平驱动能力;

- 速度等级:高速(High Speed),匹配 50 MHz 及以上时钟频率;

- 上拉电阻:使能,防止引脚空闲时电平漂移导致误触发。

- QSPI 时钟配置:

- 使能 QSPI 外设时钟:通过 RCC_APB2ENR 寄存器置位 QSPIEN 位(RCC_APB2ENR |= RCC_APB2ENR_QSPIEN);

- 配置时钟分频系数:根据目标时钟频率计算分频值,公式为: f Q S P I _ C L K = f P C L K 2 2 × ( D I V + 1 ) f_{QSPI\_CLK} = \frac{f_{PCLK2}}{2 \times (DIV + 1)} fQSPI_CLK=2×(DIV+1)fPCLK2。示例:目标 QSPI 时钟为 50 MHz,PCLK2 为 100 MHz,则 DIV = (100/(2×50)) - 1 = 0,将 QSPI_CR1 寄存器的 PRESC 位(bit 2~0)配置为 0x00。

5.1.2 QSPI 控制器基础配置

通过 QSPI 控制寄存器配置工作参数,确保控制器正常运行:

- 工作模式:配置为间接模式(QSPI_CR1 寄存器 MODE 位 = 00),由寄存器主动发起命令传输;

- 数据宽度:默认 8 位(QSPI_CR2 寄存器 DFS 位 = 000),适配标准 SPI Flash 指令格式;

- FIFO 配置:设置 FIFO 中断阈值(如 QSPI_FCR 寄存器 FTH 位 = 01,阈值为 4 字节),批量数据传输时触发中断,减少 CPU 查询开销;

- 中断使能:使能“操作完成中断”(TCIE,QSPI_CR1 位 6)与“错误中断”(ERRIE,QSPI_CR1 位 5),便于监控命令执行状态与异常处理。

5.2 QSPI 读操作执行流程(Quad I/O Fast Read,0xEB)

- 寄存器配置

- 命令控制寄存器(QSPI_CCR)配置:指令码(INSTRUCTION)0xEB(bit 7~0);指令传输模式(IMODE)01(单线传输,bit 9~8);地址传输模式(ADMODE)11(四线传输,bit 11~10);地址宽度(ADSIZE)10(24 位地址,bit 13~12);交替字节模式(ABMODE)00(无交替字节,bit 15~14);空指令周期数(DCYC)0x08(8 个 dummy 周期,bit 22~18);数据传输模式(DMODE)11(四线传输,bit 25~24);传输方向(DIR)0(接收数据,bit 26)。

- 地址寄存器(QSPI_AR)配置:写入目标读取地址(如 0x00100000,24 位地址需对齐)。

- 数据长度寄存器(QSPI_DLR)配置:写入待读取数据长度(如读取 256 字节,DLR = 255,因寄存器采用 0 开始计数)。

- 命令执行与数据接收

- 启动命令:置位 QSPI_CR1 寄存器的 CSTART 位(bit 0),QSPI 控制器自动按照配置的参数发起命令传输。

- 数据接收(两种方式可选):查询模式,循环查询 QSPI_SR 寄存器的 FTF 位(FIFO 接收满标志,bit 1),当 FTF = 1 时,读取 QSPI_DR 寄存器获取数据,直至接收完 DLR 配置的所有数据;中断模式,当 FIFO 数据量达到阈值(4 字节)时,触发中断,在中断服务函数中读取 QSPI_DR 数据,直至 DLR 计数为 0。

- 命令完成判断:查询 QSPI_SR 寄存器的 TC 位(传输完成标志,bit 0),当 TC = 1 时,表明命令执行完成。

- 错误处理

- 超时错误(TOERR,bit 4):原因包括时钟不稳定、Flash 响应异常或配置错误导致命令超时;处理方式为通过 QSPI_CR1 寄存器置位 SWRST 位重置 QSPI 控制器,重新初始化后重试命令;若多次重试失败,上报硬件故障。

- 数据错误(DERRE,bit 3):原因包括数据传输过程中出现位错误或同步异常;处理方式为重新执行读取命令,对比两次读取结果;若结果仍不一致,判定 SPI Flash 损坏或硬件连接故障。

- 访问错误(AFERR,bit 2):原因包括目标地址超出 SPI Flash 容量范围(W25Q128BV 容量 16 MByte,地址范围 0x000000~0x0FFFFFF);处理方式为校验目标地址的合法性,修正地址后重新执行命令。

- 结果校验

将读取的数据与预设校验值对比:若读取地址为未写入数据的区域,校验值为 0xFF(SPI Flash 出厂默认值);若读取地址为已写入数据的区域,校验值为写入的原始数据;若两者一致,表明读取成功;若不一致,优先排查地址配置、QE 位使能状态,再执行错误处理流程。

5.3 QSPI 写操作执行流程(Quad Input Page Program,0x32)

- 前置步骤:执行写使能(0x06)

- 配置 QSPI_CCR 寄存器:指令 0x06,IMODE=01(单线传输),ADMODE/ABMODE/DMODE=00(无地址/交替字节/数据),DIR=1(发送数据);

- 置位 CSTART 位启动命令,查询 QSPI_SR 寄存器的 TC 位确认命令完成;

- 校验写使能状态:执行 0x05 命令读取状态寄存器 1,确认 WEL 位(bit 1)为 1;若未置 1,重试写使能命令(最多重试 3 次),仍失败则执行错误处理。

- 寄存器配置

- 命令控制寄存器(QSPI_CCR)配置:指令码(INSTRUCTION)0x32(bit 7~0);指令传输模式(IMODE)01(单线传输,bit 9~8);地址传输模式(ADMODE)11(四线传输,bit 11~10);地址宽度(ADSIZE)10(24 位地址,bit 13~12);交替字节模式(ABMODE)00(无交替字节,bit 15~14);空指令周期数(DCYC)0x00(无 dummy 周期,bit 22~18);数据传输模式(DMODE)11(四线传输,bit 25~24);传输方向(DIR)1(发送数据,bit 26)。

- 地址寄存器(QSPI_AR)配置:写入目标页地址(如 0x00100000),需确保地址对齐 256 字节页边界(避免跨页写入)。

- 数据长度寄存器(QSPI_DLR)配置:写入待写入数据长度(如 128 字节,DLR = 127)。

- 命令执行与数据发送

- 启动命令:置位 CSTART 位,QSPI 控制器自动发送命令和地址。

- 数据发送(两种方式可选):查询模式,循环查询 QSPI_SR 寄存器的 FNE 位(FIFO 非空标志,bit 0),当 FNE = 0 时,向 QSPI_DR 寄存器写入数据,直至所有数据发送完成;中断模式,当 FIFO 空闲时触发中断,在中断服务函数中写入数据。

- 等待编程完成:发送完所有数据后,执行 0x05 命令读取状态寄存器 1,循环查询 BUSY 位(bit 0),直至 BUSY = 0(Flash 内部编程完成);若 BUSY 位长时间(如 5 ms)未清零,判定为编程失败。

- 错误处理

除参考读命令的超时错误、访问错误处理逻辑外,新增页编程专属错误处理:- 写保护错误:原因包括状态寄存器 1 的 WPEN 位为 1 且 WP ‾ \overline{\text{WP}} WP引脚为低电平,禁止写入操作;处理方式为拉高 WP ‾ \overline{\text{WP}} WP引脚,或通过 0x01 命令清除 WPEN 位,重新执行写使能和编程命令。

- 页边界错误:原因包括写入数据跨页(如地址 0x0000FF 写入 2 字节,跨越 0x000000~0x0000FF 页);处理方式为拆分待写入数据,确保单次写入不跨页,修正地址后重新执行命令。

- 编程失败(BUSY 位超时):原因包括 SPI Flash 物理损坏、电压异常或命令配置错误;处理方式为重试编程命令(最多 2 次),仍失败则标记该页为坏块,切换至备用页写入,并记录错误日志。

- 结果校验

执行 Quad I/O Fast Read(0xEB)命令读取刚写入的地址,将读取数据与原始写入数据逐字节对比:若一致,表明编程成功;若不一致,排查坏块、写保护、地址配置等问题,执行错误处理流程。

5.4 SPI/Dual SPI 命令流程简化要点

SPI 与 Dual SPI 命令流程基于上述 QSPI 流程简化,差异在于数据线配置、寄存器参数与命令选择:

- 数据线配置:SPI 仅配置 MOSI/MISO 为单向引脚,无需配置 IO2/IO3;Dual SPI 配置 SIO0/SIO1 为双向引脚,无需配置 IO2/IO3。

- 寄存器差异:SPI 的 ADMODE/DMODE 配置为 01(单线传输),无需配置 DCYC 字段(普通读命令无 dummy 周期);Dual SPI 的 ADMODE/DMODE 配置为 10(双线传输),无需 QSPI 专属的 IO2/IO3 相关配置。

- 命令选择:SPI 选用标准命令(如 0x03 读、0x02 写);Dual SPI 选用 Dual 类命令(如 0xBB 读、0xA2 写),无需配置 QE 位。

5.5 通用开发建议

- 时序参数校验:务必参考具体 SPI Flash 芯片手册,确认 dummy 周期数、编程时间、时钟频率上限等参数,避免时序不匹配导致通信失败;

- 批量传输优化:批量数据读写优先使用 DMA 模式(配置 QSPI_DMA 相关寄存器),减少 CPU 占用率,提升系统整体效率;

- 数据可靠性保障:关键数据写入后必须执行读取校验,重要数据建议增加冗余存储或校验码(如 CRC),避免数据丢失或错误;

- 错误处理机制:所有命令执行过程中需加入错误检测与重试机制(有限次数),重试失败后记录错误日志,便于问题定位与后期维护;

- 功耗优化:空闲时可将 SPI/QSPI 控制器置于低功耗模式,关闭时钟;对功耗敏感的场景,优先选择 SPI 或 Dual SPI(时钟频率可降低)。

六、协议选型指南

6.1 选型决策逻辑

应用场景 → 外设类型 → 速率需求 → 硬件成本 → 协议选型

- 通用外设(ADC、DAC、传感器等)→ 优先选择 SPI;

- SPI Flash 存储 → 速率需求低(<20 Mbps)→ SPI;

- SPI Flash 存储 → 速率需求中等(20~40 Mbps)、成本敏感 → Dual SPI;

- SPI Flash 存储 → 速率需求高(>40 Mbps)、需 XIP 功能 → QSPI。

6.2 典型场景选型示例

- 智能传感器节点:连接温湿度传感器、加速度传感器,速率需求低(<1 Mbps),选择 SPI,利用其高兼容性简化设计;

- 便携式数据记录仪:存储日志数据,速率需求中等(≈20 Mbps),成本敏感,选择 Dual SPI,在 4 线硬件基础上实现速率翻倍;

- 嵌入式工业控制器:程序存储在外部 Flash 中,需 XIP 功能(程序直接在 Flash 运行),速率需求高(≈50 Mbps),选择 QSPI,保障程序运行效率;

- 消费电子(如智能音箱):外扩 SPI Flash 存储固件,速率需求中等,兼顾成本与效率,选择 Dual SPI 或 QSPI。

6.3 选型注意事项

- 控制器兼容性:确保 MCU 具备对应协议的控制器(如 QSPI 需专用控制器),避免硬件不支持导致无法实现;

- 外设兼容性:确认 SPI Flash 等外设支持目标协议模式(如部分低端 Flash 仅支持 SPI,不支持 Dual SPI/QSPI);

- 开发复杂度:QSPI 开发复杂度高于 SPI/Dual SPI,需评估开发周期与团队技术能力;

- 扩展性:若未来可能提升速率,优先选择引脚兼容的方案(如 4 线硬件预留 IO2/IO3,便于从 Dual SPI 升级为 QSPI)。

附录 常用术语与符号说明

| 术语/符号 | 全称 | 说明 |

|---|---|---|

| SPI | Serial Peripheral Interface | 串行外围设备接口,标准 4 线全双工协议 |

| Dual SPI | Dual Serial Peripheral Interface | 双线 SPI,4 线半双工,单时钟周期传输 2 bit |

| QSPI | Quad Serial Peripheral Interface | 四线 SPI,6 线半双工,单时钟周期传输 4 bit |

| CPOL | Clock Polarity | 时钟极性,定义 SCLK 空闲时的电平 |

| CPHA | Clock Phase | 时钟相位,定义数据采样的时钟边沿 |

| dummy 周期 | Dummy Cycle | 空时钟周期,用于 Flash 内部数据准备 |

| QE 位 | Quad Enable Bit | 四线使能位,置 1 时启用 QSPI 模式,复用 WP ‾ \overline{\text{WP}} WP/ HOLD ‾ \overline{\text{HOLD}} HOLD为 IO2/IO3 |

| XIP | Execute In Place | 执行在原地,程序直接在外部 Flash 中运行,无需加载到 RAM |

| WEL 位 | Write Enable Latch Bit | 写使能锁存位,置 1 时允许写/擦除/模式切换操作 |

| BUSY 位 | Busy Bit | 忙标志位,置 1 时表示 Flash 正在执行内部操作(擦除/编程) |

附录 SPI 与 QSPI 开发常见故障排查

本清单按硬件层-协议层-软件层-外设适配层分层梳理,覆盖 SPI/Dual SPI/QSPI 开发中的典型故障,适用于 STM32、ESP32 等主流 MCU 与 W25Qxx/GD25Qxx 系列 Flash 的调试场景。

一、硬件层故障排查

| 故障现象 | 可能原因 | 排查步骤 | 解决措施 |

|---|---|---|---|

| 设备无响应(CS 拉低后无数据输出) | 1. 电源未供电或电压不稳 2. 引脚接线错误(如 CLK/MOSI 接反) 3. 引脚电平不匹配(如 3.3V 设备接 5V MCU) 4. 未上拉/下拉导致引脚电平漂移 | 1. 万用表测量 Flash VCC 引脚电压,确认在 3.0~3.6V 范围内 2. 对照硬件原理图核对 CS、CLK、IO0~IO3 引脚连接关系 3. 检查 MCU 引脚配置是否为开漏输出(需外接上拉电阻) 4. 示波器测量空闲时引脚电平,确认无毛刺或悬空 | 1. 更换稳定电源,增加电源滤波电容(100nF 陶瓷电容) 2. 重新焊接引脚,确保接线与原理图一致 3. 3.3V 与 5V 设备之间增加电平转换芯片 4. 关键引脚(CS、IO0~IO3)外接 10KΩ 上拉电阻 |

| 数据传输偶尔出错,随机性强 | 1. 时钟频率过高,超出外设最大支持频率 2. 布线过长或未做阻抗匹配,信号反射 3. 接地不良,存在电磁干扰 | 1. 查阅 Flash 手册确认最大时钟频率(如 W25Q128 最大支持 104MHz) 2. 示波器观察 CLK 与 IO 引脚波形,查看是否有信号畸变 3. 检查 PCB 接地是否完整,SPI 信号线是否与大功率信号线平行 | 1. 降低 QSPI 时钟频率(如从 50MHz 降至 25MHz) 2. 缩短 SPI 信号线长度,关键信号线做阻抗匹配(50Ω) 3. 增加接地过孔,隔离 SPI 信号线与干扰源 |

| QSPI 模式无法启用(IO2/IO3 无数据) | 1.

WP

‾

\overline{\text{WP}}

WP/

HOLD

‾

\overline{\text{HOLD}}

HOLD 引脚未正确复用为 IO2/IO3 2. 硬件未焊接 IO2/IO3 引脚 3. QE 位未置 1 | 1. 对照原理图确认

WP

‾

\overline{\text{WP}}

WP 接 IO2、

HOLD

‾

\overline{\text{HOLD}}

HOLD 接 IO3 2. 目视检查引脚焊接情况,万用表测量引脚连通性 3. 读取状态寄存器 2,确认 QE 位(bit1)为 1 | 1. 重新焊接

WP

‾

\overline{\text{WP}}

WP/

HOLD

‾

\overline{\text{HOLD}}

HOLD 引脚 2. 执行写使能+写状态寄存器命令,置 QE=1 3. 确保 QSPI 控制器配置中启用 4 线模式 |

二、协议层故障排查

| 故障现象 | 可能原因 | 排查步骤 | 解决措施 |

|---|---|---|---|

| 读数据全为 0xFF(未写入时正常,写入后仍为 0xFF) | 1. 写操作前未执行写使能命令(0x06) 2. 写保护生效(WPEN 位为 1 或 WP ‾ \overline{\text{WP}} WP 引脚拉低) 3. 写操作后未等待 BUSY 位清零 | 1. 读取状态寄存器 1,检查 WEL 位(bit1)是否为 1 2. 检查 WP ‾ \overline{\text{WP}} WP 引脚电平,读取状态寄存器 1 的 WPEN 位(bit7) 3. 写操作后循环查询 BUSY 位(bit0),确认其变为 0 | 1. 写操作前必须先执行 0x06 写使能命令 2. 拉高 WP ‾ \overline{\text{WP}} WP 引脚,或写状态寄存器清除 WPEN 位 3. 增加 BUSY 位等待逻辑,设置超时机制(如 5ms) |

| 读数据错误(与写入数据不一致) | 1. CPOL/CPHA 模式配置错误 2. Dummy 周期数不足 3. 地址位数配置错误(如 24 位地址配成 32 位) | 1. 对照 Flash 手册确认支持的时序模式(通常为模式 0/3) 2. 检查 Fast Read 命令的 dummy 周期数(如 0xEB 命令需 8 个 dummy 周期) 3. 确认地址宽度配置与 Flash 容量匹配(如 16MB Flash 用 24 位地址) | 1. 调整 CPOL/CPHA 参数,匹配外设时序要求 2. 增加 dummy 周期数,参考手册推荐值 3. 修正地址寄存器配置,确保地址位数正确 |

| Dual/QSPI 模式速率未提升 | 1. 未发送模式切换命令(如 0xBB/0xEB) 2. 地址/数据阶段仍使用单线传输 3. 控制器未启用 DDR 模式(仅 QSPI 支持) | 1. 检查命令序列,确认发送了对应模式的读命令 2. 查看寄存器配置,确认 ADMODE/DMODE 为双线/四线模式 3. 示波器观察地址/数据阶段的 IO 引脚,确认多线同时传输 | 1. 替换为 Dual/QSPI 专用命令(如 0xBB 替代 0x0B) 2. 配置 ADMODE/DMODE 为 10(双线)或 11(四线) 3. 启用 DDR 模式,确认时钟上下沿均传输数据 |

三、软件层故障排查

| 故障现象 | 可能原因 | 排查步骤 | 解决措施 |

|---|---|---|---|

| 寄存器配置错误,命令无法执行 | 1. 指令码写错(如将 0xEB 写成 0xBE) 2. 数据长度寄存器(DLR)配置错误(如 0 开始计数) 3. 传输方向配置错误(读配成写,写配成读) | 1. 核对命令码与手册一致性,打印寄存器配置值 2. 确认 DLR 配置值 = 数据长度 - 1(如 256 字节配 255) 3. 检查 CCR 寄存器 DIR 位,读操作设 0,写操作设 1 | 1. 修正指令码,建立命令码宏定义避免手写错误 2. 调整 DLR 计算逻辑,增加长度合法性校验 3. 区分读写操作的方向配置 |

| FIFO 溢出/空读错误 | 1. FIFO 阈值配置不合理 2. 中断服务函数处理不及时 3. 查询模式下未等待 FIFO 标志位 | 1. 查看 FCR 寄存器 FTH 位配置,确认阈值与数据长度匹配 2. 检查中断优先级,避免被高优先级中断抢占 3. 打印 FIFO 状态标志位(FTF/FNE),确认查询逻辑正确 | 1. 根据数据长度调整 FIFO 阈值(如批量传输设为 8 字节) 2. 提高 QSPI 中断优先级,简化中断服务函数逻辑 3. 查询模式下必须等待 FTF/FNE 标志位再读写 DR 寄存器 |

| 超时错误(TOERR 位置 1) | 1. 命令执行时间超过超时阈值 2. 设备未正确响应,BUSY 位卡死 3. 控制器未正确启动命令(CSTART 位未置 1) | 1. 检查超时时间配置,是否小于 Flash 擦写时间 2. 循环读取 BUSY 位,确认是否长时间为 1 3. 检查代码中是否置位 CSTART 位,且未提前清零 | 1. 增大超时阈值(如擦除操作设为 100ms) 2. 超时后重置 QSPI 控制器,重新初始化 3. 确保 CSTART 位置 1 后,等待 TC 位再清除 |

四、外设适配层故障排查

| 故障现象 | 可能原因 | 排查步骤 | 解决措施 |

|---|---|---|---|

| 擦除操作失败 | 1. 擦除命令与扇区/块大小不匹配 2. 擦除后未等待 BUSY 位清零 3. 坏块导致擦除失败 | 1. 确认擦除命令(0x20 扇区/0xD8 块)与目标地址匹配 2. 擦除后循环查询 BUSY 位,直至为 0 3. 读取 Flash 坏块标记,确认目标地址非坏块 | 1. 根据操作范围选择正确擦除命令 2. 增加擦除后 BUSY 位等待逻辑 3. 建立坏块管理机制,跳过坏块地址 |

| XIP 模式无法运行程序 | 1. 内存映射地址配置错误 2. QSPI 时钟频率过高,程序运行不稳定 3. Flash 未正确初始化,QE 位未置 1 | 1. 核对 MCU 内存映射地址范围,确认与 Flash 容量匹配 2. 降低 QSPI 时钟频率,测试不同速率下的稳定性 3. 检查 XIP 模式前的初始化流程,确认 QE 位已置 1 | 1. 修正内存映射地址配置,确保与链接脚本一致 2. 选择稳定的时钟频率(如 33MHz) 3. 初始化流程中先配置 QE 位,再进入 XIP 模式 |

| 设备 ID 读取错误 | 1. ID 读取命令选择错误 2. 传输线数配置错误(如四线 ID 用单线读取) 3. 厂商 ID 与设备 ID 顺序混淆 | 1. 确认 ID 命令(0x90/JEDEC ID、0xAB/Release Power-Down) 2. 检查 ID 命令的传输模式,是否与手册一致 3. 对照手册确认 ID 字节顺序(如厂商 ID 在前,设备 ID 在后) | 1. 替换为正确的 ID 读取命令 2. 配置 ID 命令的传输线数(如 0x94 命令用四线模式) 3. 调整 ID 字节解析顺序,匹配手册定义 |

五、通用排查工具与方法

- 示波器/逻辑分析仪:抓取 CS、CLK、IO0~IO3 波形,分析命令、地址、数据阶段的时序是否符合手册要求。

- 寄存器打印调试:在关键步骤(命令发送前、数据传输后)打印 QSPI 控制器寄存器值,确认配置与预期一致。

- 最小系统验证:搭建仅包含 MCU 与 Flash 的最小系统,排除其他外设干扰,验证基础通信功能。

- 对比测试:先用 SPI 模式验证通信正常,再逐步切换到 Dual/QSPI 模式,定位模式切换过程中的问题。

via:

- 基础——SPI 与 QSPI 的异同,QSPI 的具体协议是什么,QSPI 有什么用-优快云 博客

https://blog.youkuaiyun.com/wangguchao/article/details/105593303 - SPI 和 QSPI 协议学习-优快云 博客

https://blog.youkuaiyun.com/weixin_36590806/article/details/114945334 - SPI、Dual SPI 和 QSPI 有什么区别?

https://mp.weixin.qq.com/s/6PL8RuEbfcsOxu1-A87JHQ - 【SPI】SPI 与 QSPI 异同与使用 - Emma1111 - 博客园

https://www.cnblogs.com/Wangzx000/p/16971543.html - 几篇质量高点的 SPI 文档,方便 V7 用户手册SPI制作

https://forum.anfulai.cn/forum.php?mod=viewthread&tid=96788

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?