最近数据缓存方面用到了较多的fifo,发现Xilinx的fifo的depth、rdcnt、full flag等参数的时序会因为fifo的种类(standard or fwft)、时钟(dc or single)、位宽(same or not)等,因此写文章记录一下,方便以后查看。先说说自己的结论吧,主要是以下几点:

1,full、empty信号变化会因为情况不同而不同,但有两点是所有的情况都一样的:a,full信号拉高,会延迟最后一个写使能信号拉高;b,empty信号拉高,会延迟最后一个读使能信号拉高。因此,如果empty作为读信号或者full作为写信号,赋值时必须无延迟。

2,fifo复位后,需要隔2~3个周期才能操作,当然更长也可以。

3,任何模式下,写计数与写时钟对齐,读计数与读时钟对齐。双时钟时,写计数延迟2个时钟变化;单时钟时,写计数延迟1个时钟变化。值得注意的是,在fwft模式下,读计数会比实际少2,写计数也会在开始正常的情况下然后变得比实际少2,因此,在fwft模式下用读计数作为触发条件时需要比实际少2,写计数最好不要作为触发条件。

4,当位宽不一致时,a,写8位,读16位,写第一个为h‘01,第二个为h‘02,那么读第一个则为h'0102;b,写16位,读8位,写第一个为h'1234,那么第一个读为12,第二个读为34。

5,非常重要,xilinx fifo的大坑,对于异步fifo,即使两边的时钟频率一样,也最好不要采用“非空就读”的策略,因为这样虽然你的数据不会丢,但是可能会不连续;同样设计的fifo最好预留足够的空间,因为当读写同时发生时,空间不足时full信号会莫名拉高,导致你写失败。

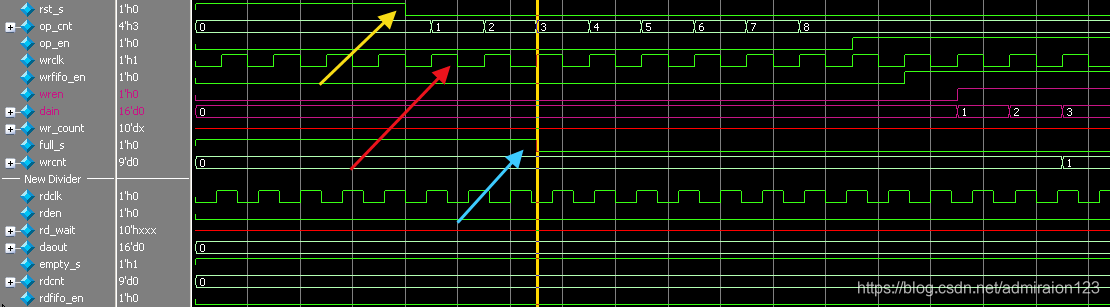

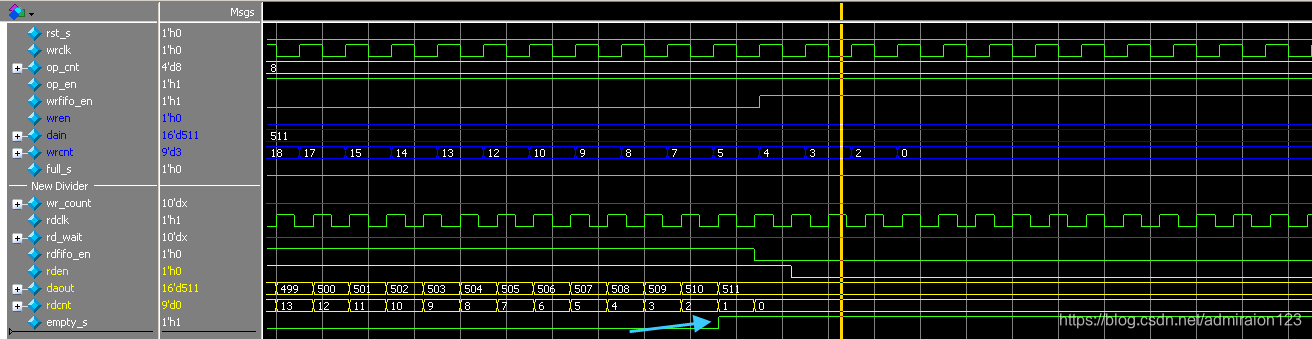

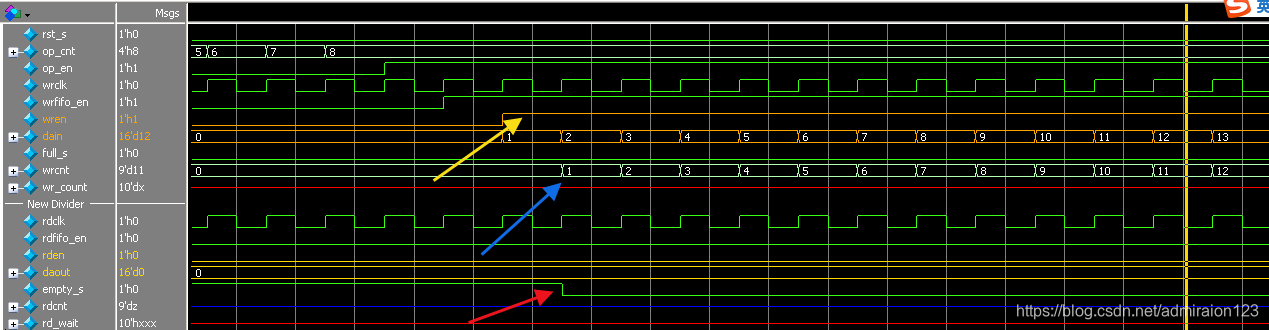

情况1:a,时钟,写为20M,读为25M;b,位宽,读写一样;c,标准fifo。d,深度,设置512,但是此时xilinx的实际深度为511,没明白。从下图可以看出,fifo在复位信号(黄箭头)释放后,满信号(蓝箭头)会等待三个写时钟(红箭头)后在释放,即此后才可以操作fifo。当然fifo在复位时是满还是空是可以设置的,且释放等待时间也不一定,只是需要注意复位后,一定要等待几个时钟再去操作fifo。

如下图所示,写计数wrcnt在第一个写使能后,延迟两拍写时钟才变为1,而读计数rdcnt和空信号则在延迟7拍读时钟才变正确。

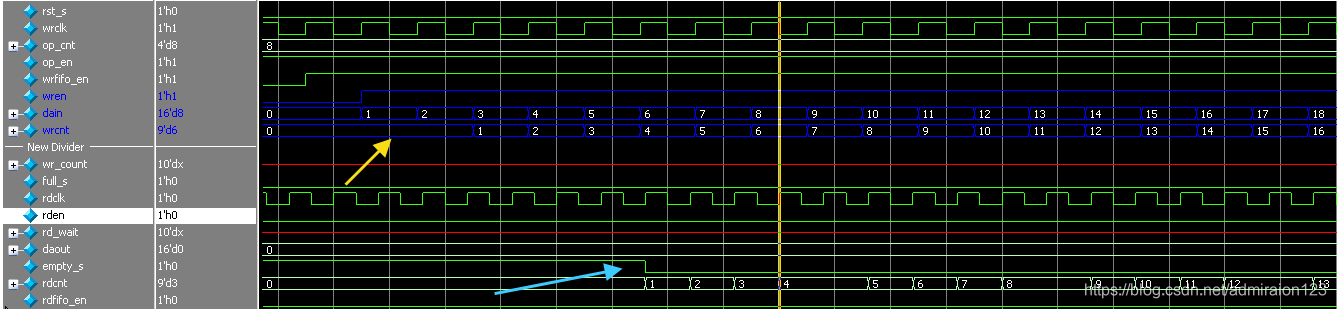

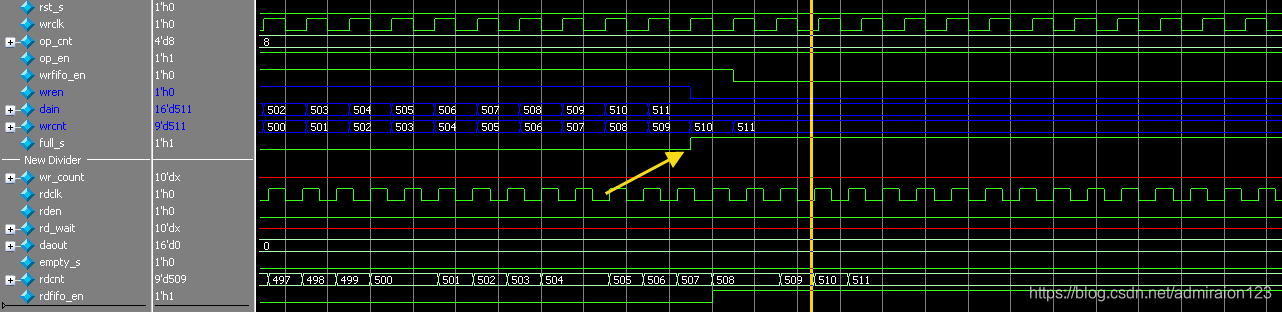

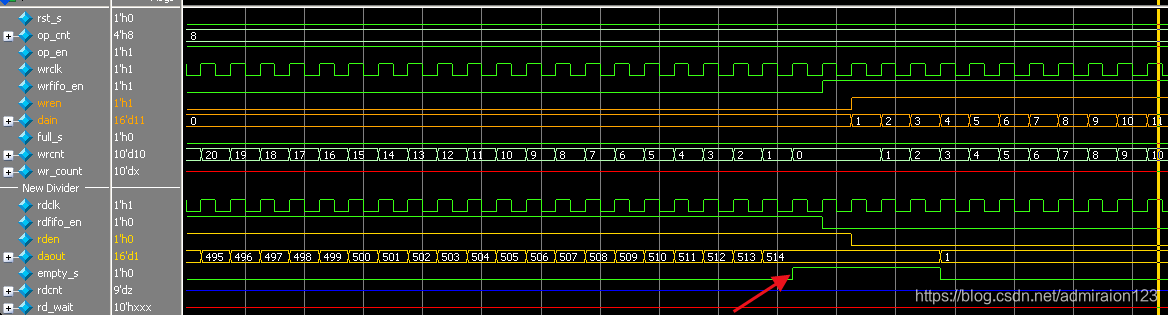

如下图所示,满信号会在写完最后一个数后延迟一个wrclk拉高,因此写程序时不要用full flag去作为写使能的条件,这样会导致最后一个值写不进去(当然,如果直接将full flag不通过寄存的方式赋值给写使能信号,也是可以的)。

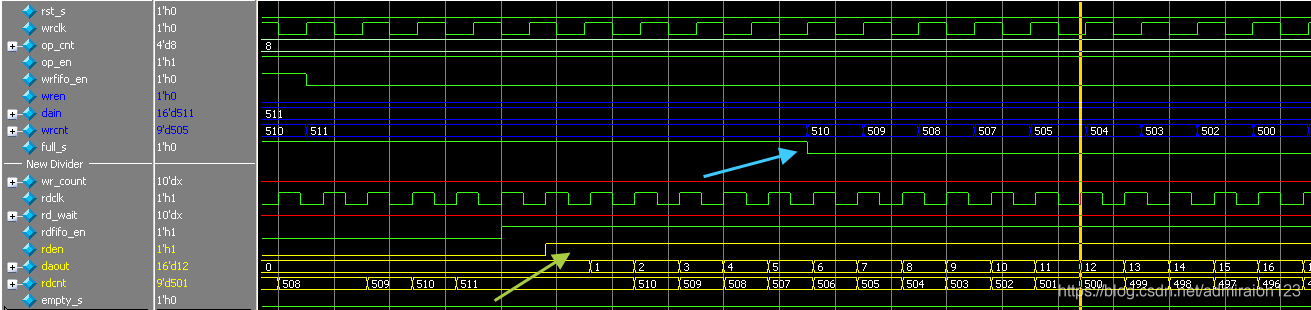

再看看读过程,读使能信号拉高后,数据延迟一个读时钟出来。读计数延迟两个读时钟。满信号在7个读时钟后才拉低。

同理,空信号也会在读完最后一个数后,延时一个读时钟拉高,因此不要用空信号作为读使能依据时,需要通过组合电路,不能寄存,否则会多读一次。

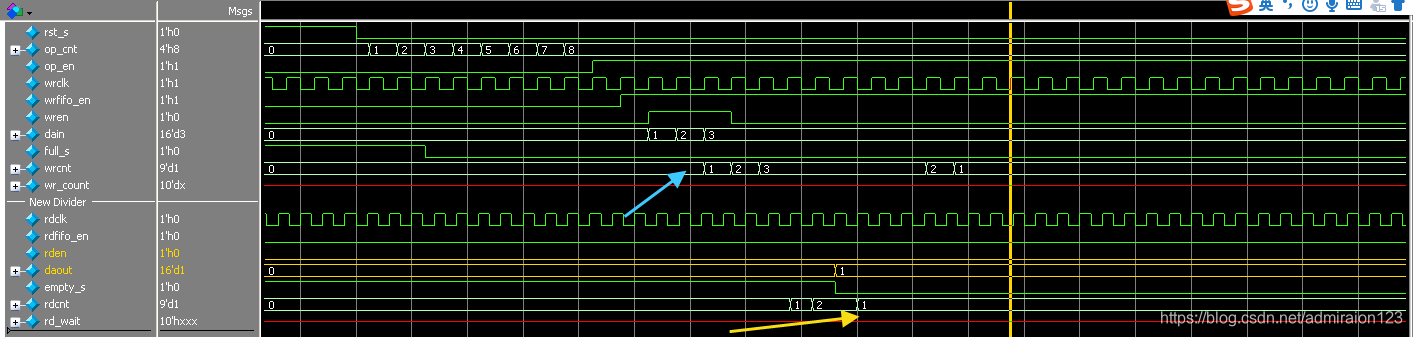

情况2:在1的基础上,将标准形式改为fwft形式。此时设置512深度,但xilinx例化的fifo实际为513,不是太明白。此种情况与情况1相比,主要有两点不同,a,读数据不会延迟一个读时钟输出;b,读计数rdcnt会比实际少2,不太明白,即使fwft模式下看做已经读了一次,也应该比实际少1。

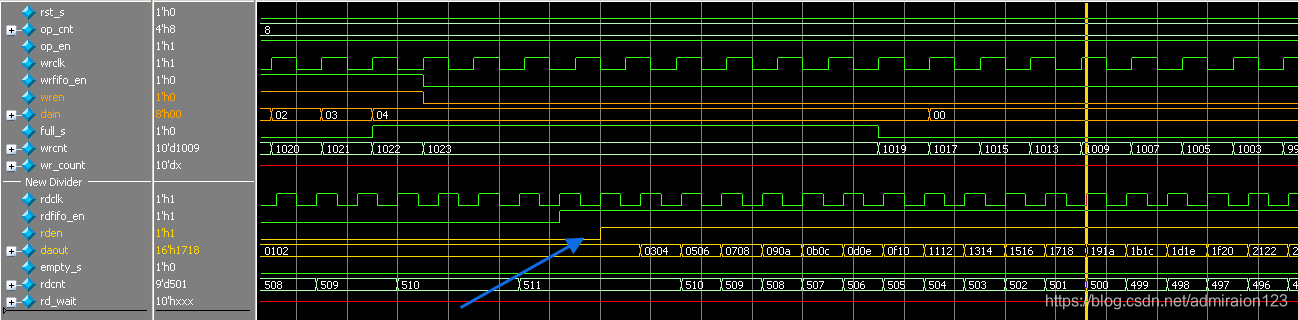

情况3:在2的基础上,将写数据位宽改为8,深度改为1024,读数据改为16,深度为512,但Xilinx例化时写实际深度为1027,读深度为513。此种情况下,需要注意的点:数据排列,比如第一个数为hex01,第二个数为hex02,则读出来的为hex0102。

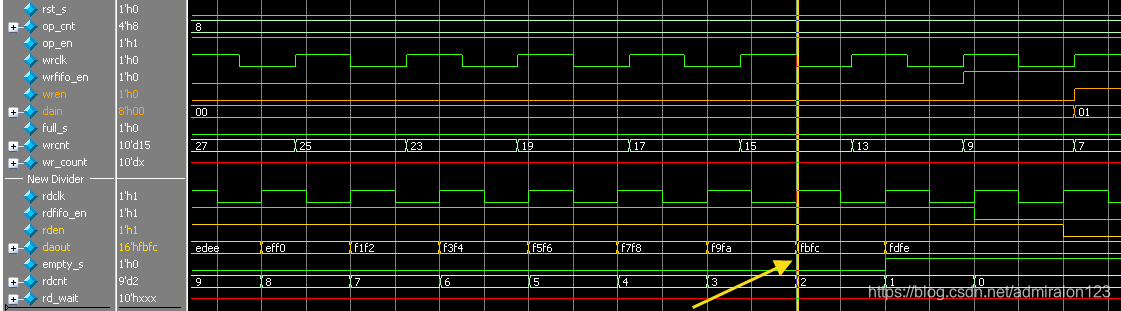

情况4:在3的基础上,将fwft改为标准形式,此时xilinx例化的实际写深度为1023,读深度为511。此种情况与情况1基本一样。

情况5:在情况情况4的基础上,将读写位宽都改16位,时钟改为单时钟。此时Xilinx实际例化深度为512。此种情况,计数只延迟一个时钟输出,空信号、满信号号变化也只延迟一个时钟。

情况6:在情况5的基础上,将标准形式fifo改为fwft。此种情况下实际例化深度为514。此种情况除了空信号会在写第一个数延迟3拍拉低,别的一样。

616

616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?