本章围绕用于信号处理与机器学习加速的硬件平台选型、实时流处理的理论基础、在资源受限平台(FPGA / 嵌入式)上部署模型的压缩与整数量化原理,以及系统级监控与远程更新的可靠性保障展开。每一节均从数学模型出发,给出推导、界与证明,以便作为教材中算法与工程实现部分的正式章节内容。

13.1 SDR、FPGA、GPU、ASIC 的角色与选型指南

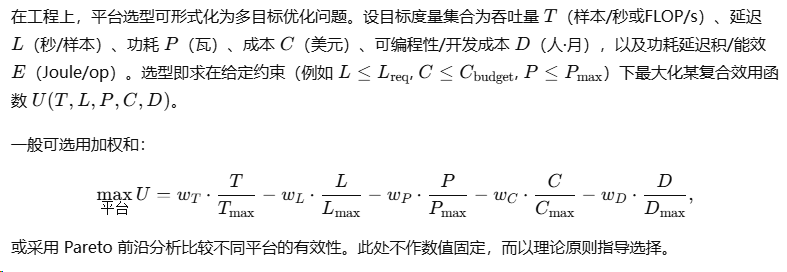

13.1.1 目标函数与约束建模

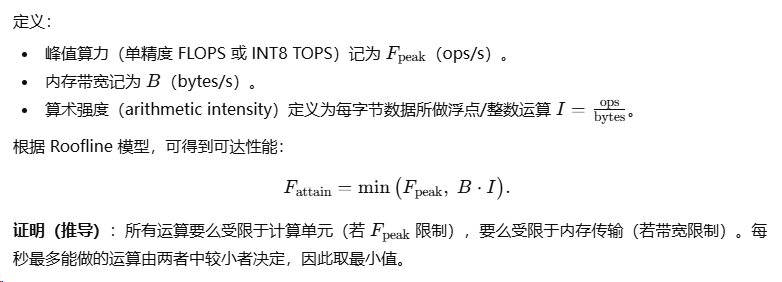

13.1.2 平台能力的基本模型

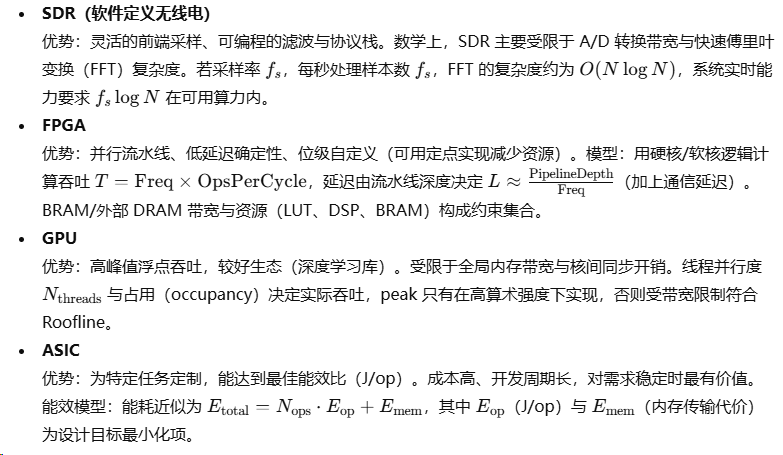

13.1.3 各平台数学特征比较

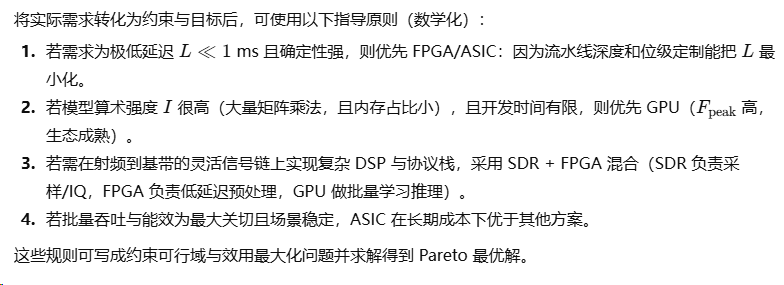

13.1.4 选型准则的正规化形式

13.2 实时流处理:采样率、缓冲、并行化、延迟优化

13.2.1 采样理论与带宽约束

13.2.2 缓冲与队列论

13.2.3 并行化、流水与分区

并行化可分为数据并行、模型并行与流水线(pipeline)并行。对实时流处理,常用流水线与并行通道减少每阶段延迟与提高吞吐。

13.2.4 延迟优化的综合公式

13.3 模型压缩、整数量化与在 FPGA/嵌入式上的部署要点

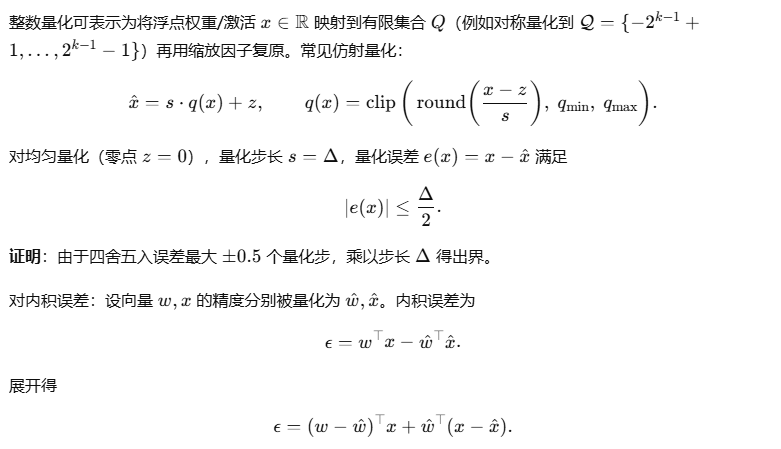

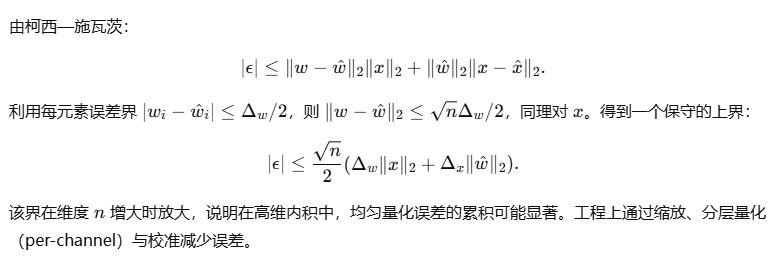

13.3.1 量化数学基础与误差界

13.3.2 定点与块浮点表示

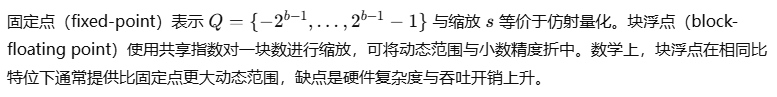

13.3.3 量化感知训练(QAT)与后训练量化(PTQ)

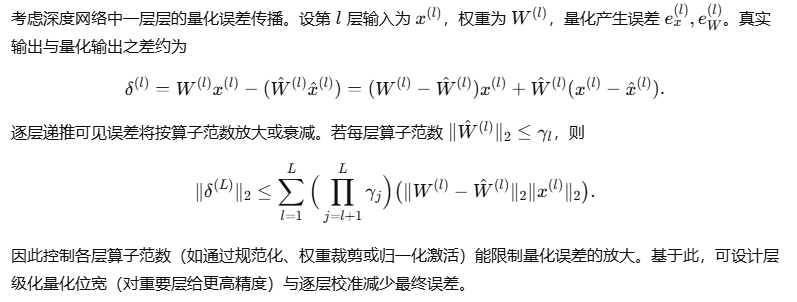

13.3.4 量化误差传播与稳定性分析

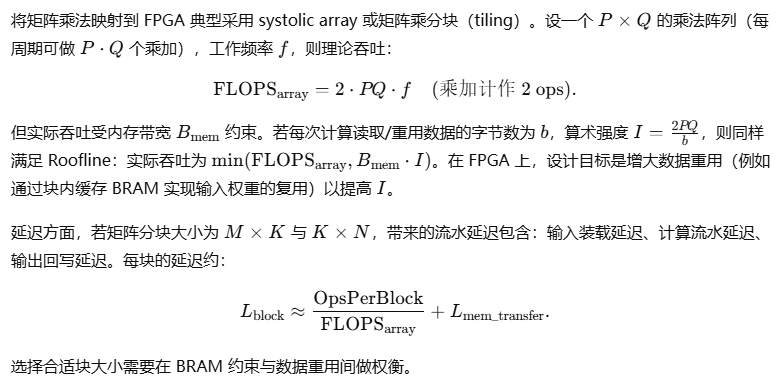

13.3.5 FPGA/嵌入式部署的算力/带宽配平与阵列设计

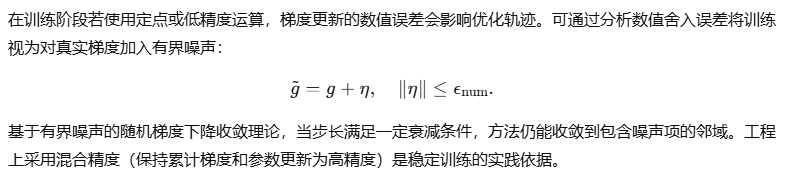

13.3.6 定点实现中的收敛与数值稳定性

13.4 监控、日志与远程更新机制

13.4.1 监控指标与滤波/采样策略

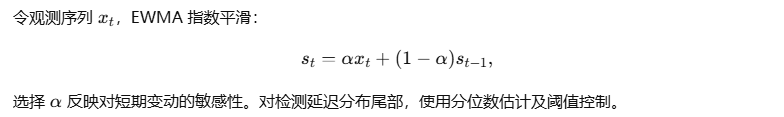

监控指标包括:延迟分位数(P50/P95/P99)、吞吐、错误率、资源利用(CPU/GPU%)、温度、电流/功耗、版本号等。为了可靠检测异常,采用统计检测方法,例如基于滑动窗口的均值与方差估计,并使用带阈值的 CUSUM 或 EWMA 检测突发漂移。

13.4.2 日志的一致性与带宽考虑

日志可分为高频短日志(local)与低频汇总日志(remote)。高频原始日志保存在本地循环缓冲,关键事件以可靠消息队列(例如带持久化的可靠传输)汇报。网络受限时采用压缩与批量发送策略:证明批量发送在单位带宽费用下能降低传输开销但增加发送延迟,形成带宽/延迟权衡。理性设计采用自适应批量策略以满足延迟约束。

13.4.3 远程更新(OTA)的一致性与可靠性证明

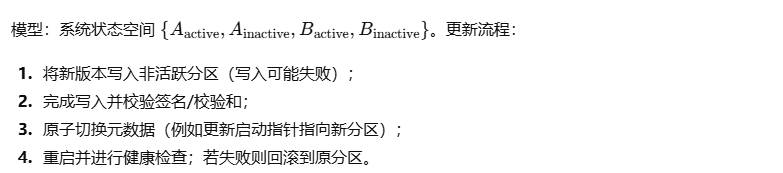

设计目标:在远程更新期间保证系统随时可回滚到健康版本,防止中途损坏导致不可用。常用架构为双分区(A/B)镜像与原子切换。

原子性证明要点:若切换操作(步骤3)为原子写(例如利用单次写入持久化标志或事务文件系统),则系统在任意时刻只有一个分区被标记为启动目标,从而保证系统不会指向半写入的镜像。若切换操作可能出现中断,需设计切换为“两阶段提交”形式并保证 idempotence:写入完成标志与激活标志分开,激活前需校验完整性。该设计可把不变性 III(“在任何时间,系统有一个有效的可引导映像”)作为不变式,证明更新步骤保持该不变式。

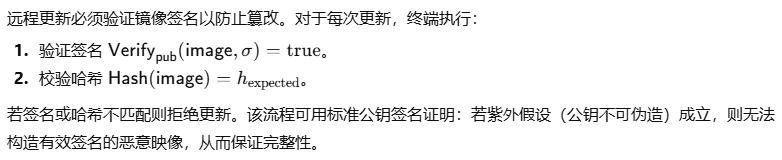

13.4.4 安全性保证:认证与完整性

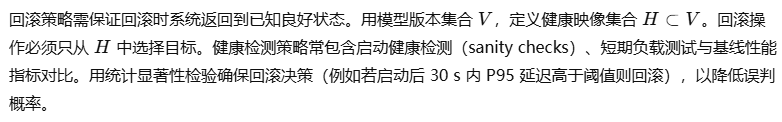

13.4.5 回滚与一致性验证

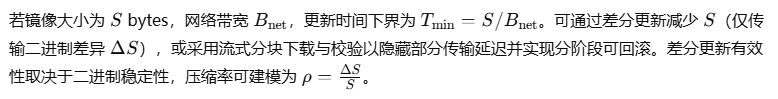

13.4.6 可靠更新协议的时间复杂度与带宽需求

本章小结

本章以严格的数学与工程模型系统化地讨论了硬件平台选型的度量、实时流处理的理论基础与延迟/带宽约束、模型压缩与整数量化的误差分析及其在 FPGA/嵌入式平台上的实现要点,以及监控、日志与远程更新的可靠性与安全措施。关键结论包括:

-

平台选型可形式化为带约束的效用最大化问题,Roofline 与能效模型是第一性原则工具;

-

实时处理必须从采样定理、排队理论与并行度的角度共同设计以满足延迟约束;

-

量化误差在高维内积中会累积,需采用 per-channel 缩放、QAT、动态范围管理以控制误差放大;

-

FPGA/ASIC 设计的核心是数据重用(提高算术强度)与资源平衡(LUT/DSP/BRAM/带宽);

-

远程更新要保证原子性、完整性与可回滚性,采用双分区、签名校验与健康检测可以提供工程级可证明的安全性保障。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?