目录

3.4.4 MSI and MSI-X Capabilities

4.2 Write DMA Avalon-MM Master Port

4.5 32-Bit Control Register Access (CRA) Slave Signals

4.6 Descriptor Controller Interfaces when Instantiated Internally

4.6.1 Read Descriptor Controller Avalon-MM Master interface

4.6.2 Write Descriptor Controller Avalon-MM Master Interface

4.6.3 Read Descriptor Table Avalon-MM Slave Interface

4.6.4 Write Descriptor Table Avalon-MM Slave Interface

4.8 Reset, Status, and Link Training Signals

4.8.2 Status and Link Training Signals

4.9 MSI Interrupts for Endpoints

4.10 Physical Layer Interface Signals

4.10.1 Transceiver Reconfiguration

5.1 Reset Sequence for Hard IP for PCI Express IP Core and Application Layer

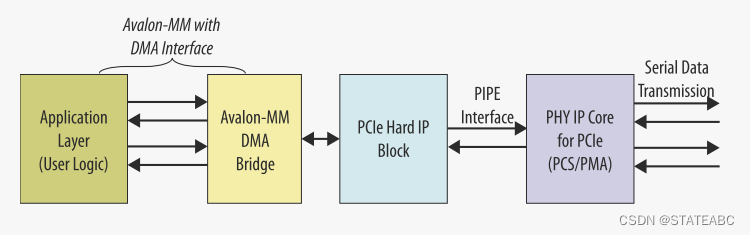

1. IP概述

V系列指的是Intel的Arria V、Cyclone V、Arria V GZ和Stratix V,适用于PCI Express的V系列Avalon-MM DMA实现了完整的协议栈,包括事务层、数据链路层核物理层,并且支持Gen1 x8、Gen2 x4、Gen2 x8、Gen3 x2、Gen3 x4 和 Gen3 x8。

V-Series Avalon-MM DMA Interface for PCI Express Intel FPGA IP支持与DMA配合达到 Gen3 ×8数据速率的128位或256位Avalon-MM到应用层的接口。

2. Avalon-MM DMA Ports

在V-Series Avalon-MM DMA for PCI Express Intel FPGA IP中有一些Avalon-MM DMA端口,这些端口实现了通过DMA读写数据的功能。

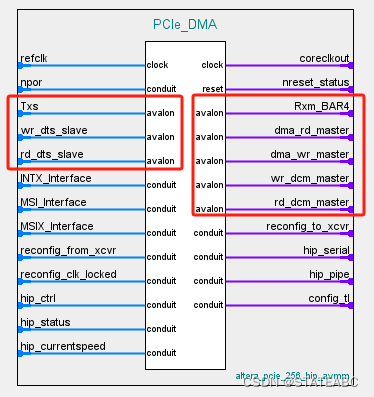

| Function | Port | Description |

| TXS | Txs | Avalon-MM从端口 Avalon-MM主设备使用该端口向PCIe发送内存读取或写入操作。 当DMA完成操作时,Descriptor Controller使用该端口将DMA状态写回PCIe中的描述符空间。Descriptor Controller还使用该端口向上游发送MSI中断。 |

| Read Data Mover | dma_rd_master | Avalon-MM主端口 在正常的读取DMA操作期间,Read Data Mover将数据从PCIe移动到片上存储器并且从PCIe域获取描述符,将它们写入Descriptor Controller中的FIFO。 dma_rd_master端口连接到wr_dts_slave端口,用于加载写入DMA描述符FIFO,而rd_dts_slave端口用于加载read |

| Write Data Mover | dma_wr_master | Avalon-MM 主端口 Write Data Mover从片上存储器读取数据,然后将数据写入PCIe域。 |

| Descriptor Controller FIFOs | wr_dts_slave rd_dts_slave |

用于描述符控制器FIFO的Avalon-MM从端口。 当Read Data Mover从系统内存获取描述符时,它使用该端口将描述符写入FIFO中。读取DMA描述符和写入DMA描述符有两个单独的描述符表,因此有两个端口。 写入DMA FIFO的地址范围为0x100_0000至0x100_1FFF。 读取DMA FIFO的地址范围为0x100_2000至0x100_3FFF。 |

| Control in the Descriptor Controller | wr_dcm_master rd_dcm_master |

Control in the Descriptor Controller有一个用于读取DMA的传输端口和一个用于写入DMA的接收端口。 接收端口连接到RXM_BAR0,而传输端口连接到Txs。 来自RXM_BAR0的接收路径在内部连接,不在连接面板中显示。对于传输路径,读取和写入DMA端口都在连接面板中外部连接到Txs(即wr_dcm_master和rd_dcm_master都连接到Txs)。 |

| RXM_BAR0 | 不显示 | Avalon-MM主端口 它将来自PCIe主机的内存访问传递到PCIe BAR0。主机使用该端口来编程Descriptor Controller。 当使用了内部描述符控制器,端口连接不显示,连接在a10_pcie_hip_0模块内部进行。 |

| RXM_BAR4 | Rxm_BAR4 | Avalon-MM主端口。 它将来自PCIe主机的内存访问传递到PCIe BAR4。它连接到片上存储器。PCIe主机通过PCIe BAR4访问存储器。 在典型的应用中,系统软件控制该端口以在片上存储器中初始化随机数据。软件还读取数据以验证正确的操作。 |

根据Intel给的示例,NIOS中连接方式

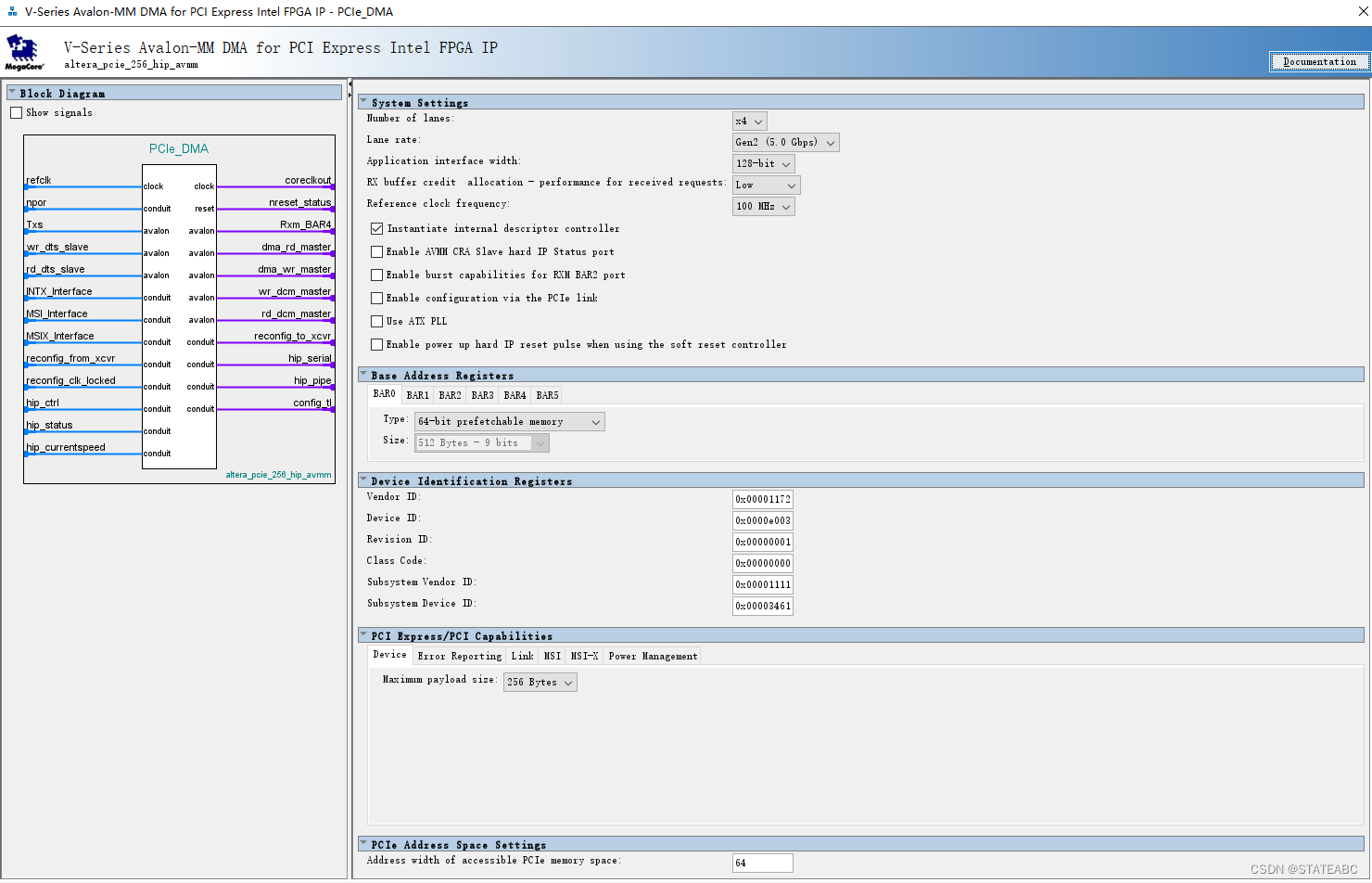

3. 参数设置

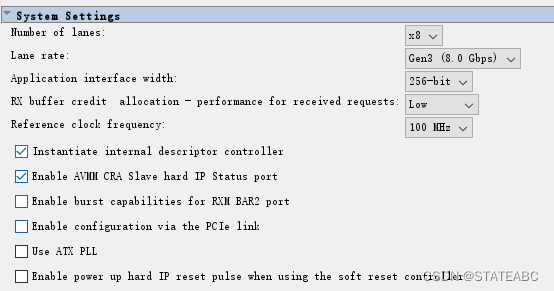

3.1 系统设置

- Number of lanes

通道数,有x1、x2、x4、x8四个选项,指定支持的最大通道数。 带DMA的Avalon-MM接口不支持x1配置。

- Lane Rate

通道速率,有Gen1 (2.5 Gbps)、Gen2 (2.5/5.0 Gbps)、Gen3 (2.5/5.0/8.0 Gbps)三个选项,指定链路可以运行的最大数据速率。

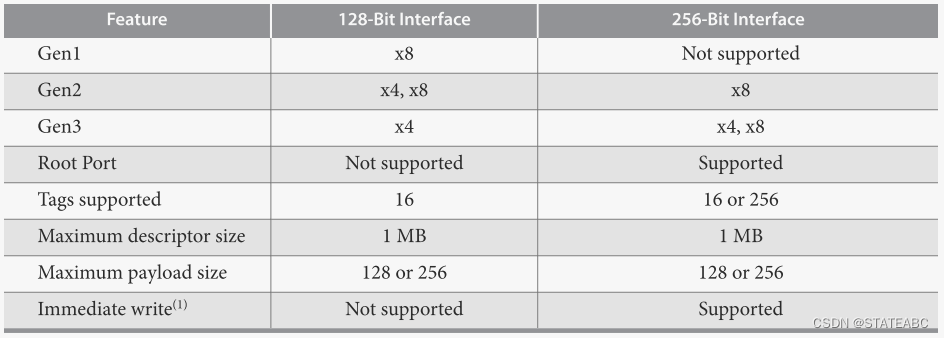

- Application interface width

应用接口宽度,有128 bits、256bits两个选项。指定应用层接口的宽度。

可以组成以下组合:

| 应用接口宽度 | 配置 | 应用层时钟频率 |

| 128 bits | Gen1 x8 | 125 MHz |

| 128 bits | Gen2 x4 | 125 MHz |

| 128 bits | Gen2 x8 | 250 MHz |

| 256 bits | Gen2 x8 | 125 MHz |

| 128 bits | Gen3 x4 | 250 MHz |

| 256 bits | Gen3 x4 | 125 MHz |

| 256 bits | Gen3 x8 | 250 MHz |

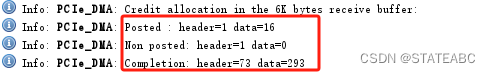

- RX buffer credit allocation - performance for received requests

RX 缓冲区信用分配 - 接收请求的性能,有Minimum、Low、Balanced三个选项。确定在16KB的RX缓冲区中分配的posted header credits、posted data credits、non-posted header credits、completion header credits和completion data credits,调整信用分配以优化系统性能。更改此选项时,消息窗口会动态更新Posted、Non-Posted以及Completion的信用数量。

• Mininum—配置Non-Posted请求信用和Posted请求信用所允许的最小PCIe规范,将大部分RX缓冲区空间留给Completion的header和data。对于应用程序逻辑生成许多读取请求并且很少从PCIe链路接收单个请求的变体,请选择此选项。

• Low—配置更大一些的RX缓冲区空间用于Non-Posted请求信用和Posted请求信用,但仍将大部分空间用于Completion的header和data。对于应用程序逻辑生成许多读取请求并且很少从 PCIe 链路接收少量请求的变体,请选择此选项。此选项推荐用于典型的Endpoint应用程序,其中大部分的PCIe流量由位于端点应用层逻辑中的DMA引擎生成。

• Balanced—将大约一半的RX缓冲区空间配置给接收请求,另一半给接收完成。选择此选项适用于接收请求和接收完成大致相等的应用程序。

- Reference clock frequency

参考时钟频率,有100MHz、125MHz两个选项。PCI Express基础规范3.0要求100MHz ±300 ppm的参考时钟。提供125MHz参考时钟是为了方便包含125MHz 时钟源的系统。

对于Gen3,建议使用公共参考时钟 (0ppm),当使用单独的参考时钟(非0ppm)时,PCS 偶尔必须插入SKP符号,可能会导致PCIe链路进入恢复状态。 Gen1或Gen2模式不受此问题的影响。

- Instantitate internal descriptor controller

实例化内部描述符控制器,On/Off。当为On时,描述符控制器将包含在Avalon-MM桥中。 当为Off时,描述符控制器作为单独的外部组件。如果使用Altera提供的描述符控制器,则为On。 如果修改或替换设计中的描述符控制器逻辑,则为Off。

- Enable AVMM CRA Slave hard IP Status port

启用Avalon-MM CRA Slave硬件IP状态端口,On/Off。启用此选项允许对桥接寄存器进行读写访问,但Completer的单dword除外。该选项对Requester/Completer变量是必需的,对Completer Only变量是可选的。

- Enable burst capabilities for RXM BAR2 port

启用RXM BAR2端口的突发功能,On/Off。当为On时,BAR2 RX Avalon-MM主机支持突发。如果BAR2是32位且支持突发,则 AR3不可用于其他用途。如果BAR2是64位,则 BAR3 寄存器保存地址的高32位。

- Enable configuration via the PCIe link

启用配置通过PCIe链路,On/Off。打开时,Quartus软件将Endpoint放置在通过协议 (CvP) 配置所需的位置。

- Use ATX PLL

使用ATX PLL,On/Off。当打开此选项时,PCI Express的Hard IP使用 ATX PLL而不是CMU PLL。 对于其他配置,使用ATX PLL代替CMU PLL可减少所需的收发器通道数量。 此选项需要使用软复位控制器,并且不支持CvP流程。

- Enable power up hard IP reset pulse when using the soft reset controller

启用软复位控制器时在上电时启用硬件IP复位脉冲,On/Off。当打开此选项时,软复位控制器在上电时生成一个脉冲以复位硬件IP。这个脉冲确保在对设备进行编程后复位硬件IP,无论专用的PCI Express复位引脚perstn的行为如何。此选项适用于使用软复位控制器的Gen2和Gen3设计。

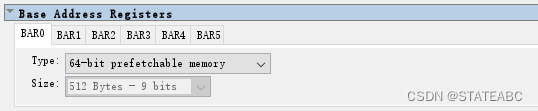

3.2 基址寄存器 (BAR) 设置

可用BAR的类型和大小取决于端口类型。

- Type

BAR的类型,有Disabled、64-bit prefetchable memory、32-bit non-prefetchable memory、32-bit prefetchable memory、I/O address space五个选项。

如果选择64位可预取内存,将合并2个连续的BAR以形成一个64位可预取BAR;必须将较高编号的BAR设置为Disabled。不支持非预取(non-prefetchable)的64位BAR,因为在典型系统中,Root Port Type 1配置空间将最大非预取内存窗口设置为32位。

将内存定义为prefetchable允许提前获取连续数据。当requestor者可能需要来自同一区域的比最初请求的更多的数据时,预取

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1276

1276

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?