1. DMA Controller Core

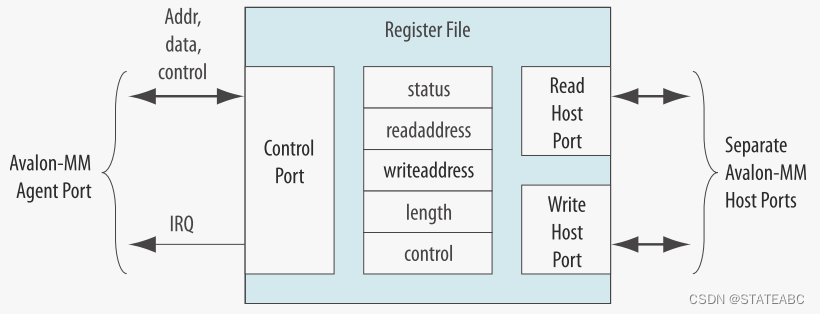

具有 Avalon 接口的DMA Control Core执行批量数据传输,从源地址范围读取数据并将数据写入不同的地址范围。 Avalon 内存映射 (Avalon-MM) 主机外设(如 CPU)可以将内存传输任务交给DMA控制器。 当DMA控制器执行内存传输时,主机可以自由地并行执行其他任务。

典型的 DMA 事务处理如下:

- CPU通过写入控制端口来为DMA控制器准备事务。

- CPU启用DMA控制器,然后DMA控制器开始传输数据,无需CPU的额外干预。 DMA的主机读端口从读地址读取数据,该地址可以是存储器或外设。 主机写端口将数据写入目标地址,该地址也可以是存储器或外设。 浅FIFO在读端口和写端口之间缓冲数据,默认深度为2。

- 当传输指定数量的字节(固定长度事务)或发送方或接收方发出数据包结束信号(可变长度事务)时,DMA 事务结束。 在事务结束时,DMA 控制器会生成中断请求 (IRQ)。

- 在事务期间或之后,CPU 可以通过检查 DMA 控制器的状态寄存器来确定事务是否正在进行,或者事务是否结束(以及如何结束)。

设置DMA事务:

Avalon-MM主机外设通过控制端口写入寄存器来设置和启动DMA事务:

- 读取(源)地址位置;

- 写入(目标)地址位置;

- 各个传输的大小:字节(8 位)、半字(16 位)、字(32 位)、双字(64 位)或四字(128 位);

- 事务结束时启用中断;

- 使源或目标能够通过数据包结束信号结束 DMA 事务;

- 指定源和目标是内存还是外设;

然后主机外设在控制寄存器中设置一个位以启动 DMA 事务。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

603

603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?