SYNCFIFO

synvfifo_inst

synvfifo synvfifo_inst (

.clock ( clock_sig ),

.data ( data_sig ),

.rdreq ( rdreq_sig ),

.wrreq ( wrreq_sig ),

.empty ( empty_sig ),

.full ( full_sig ),

.q ( q_sig ),

.usedw ( usedw_sig )

);

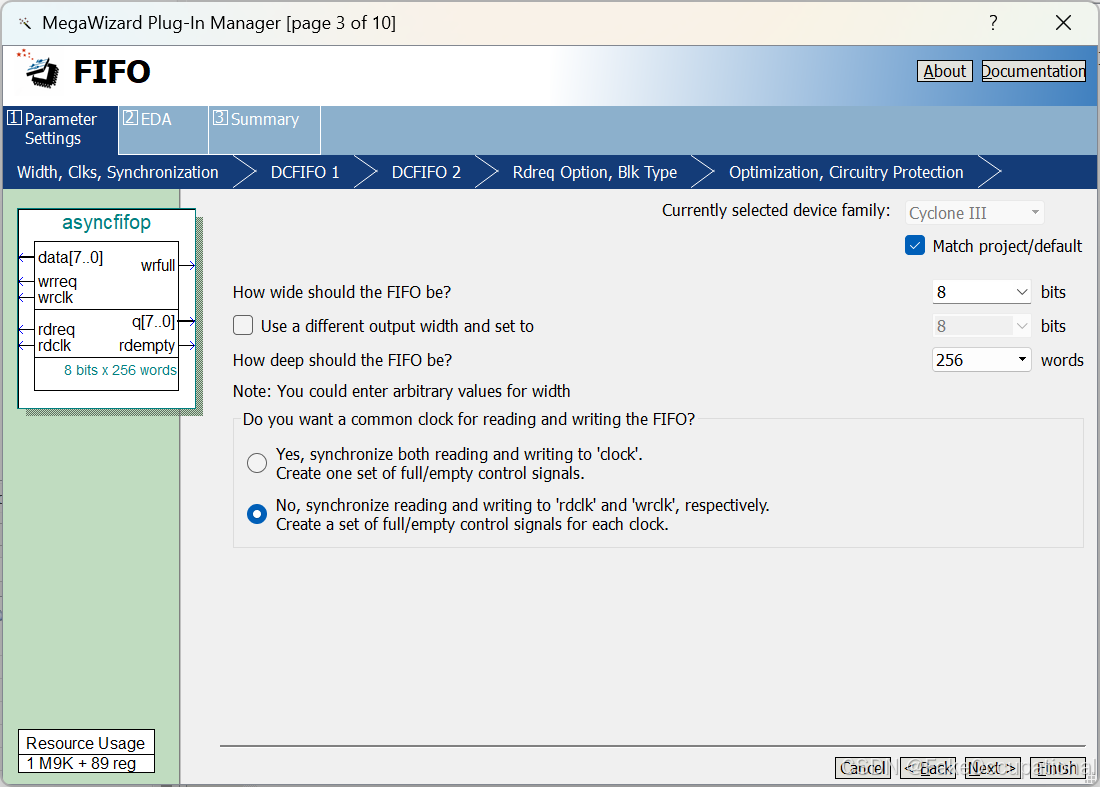

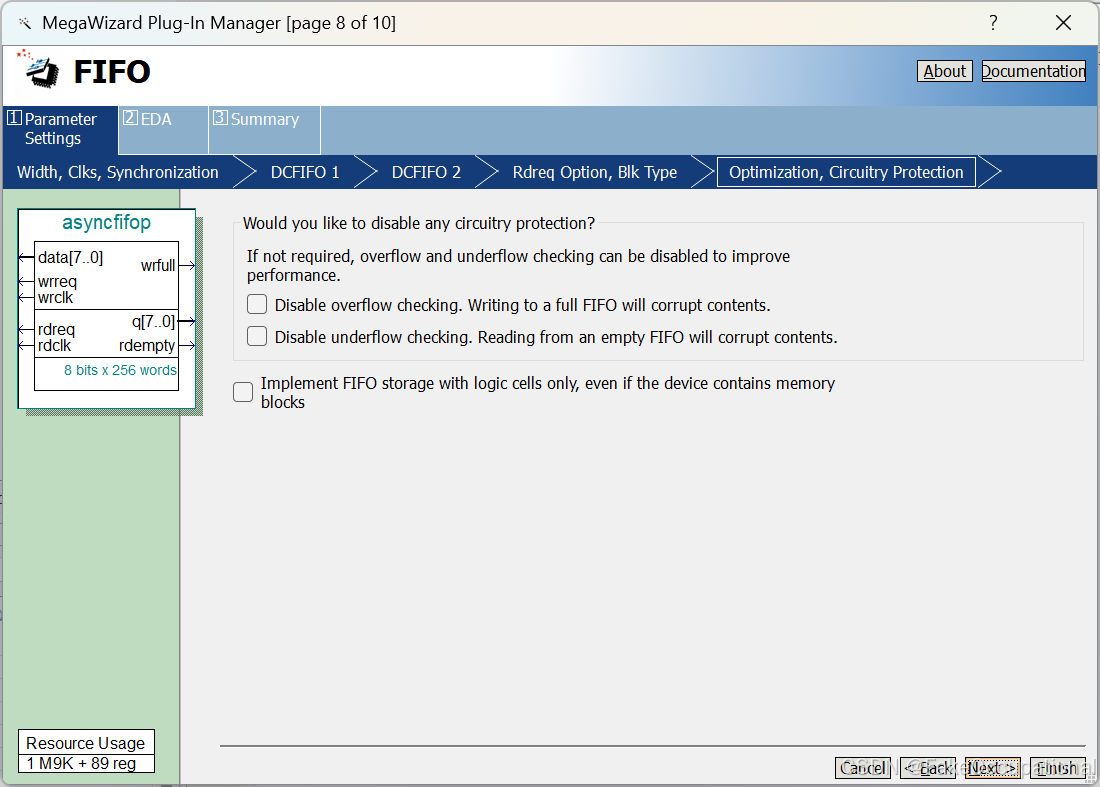

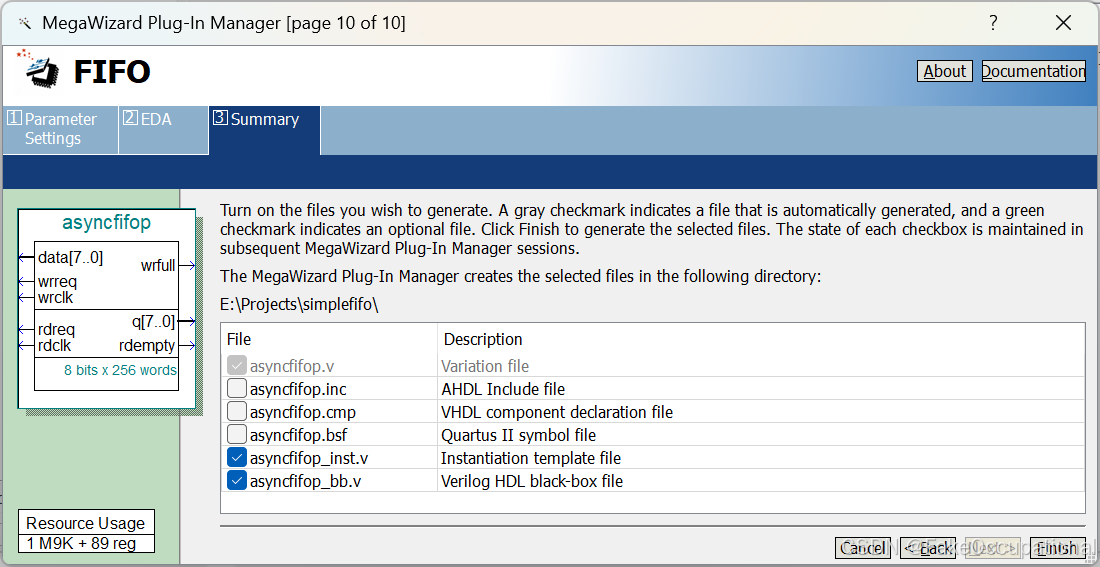

ASYNCFIFO

asyncfifop_inst

asyncfifop asyncfifop_inst (

.data ( data_sig ),

.rdclk ( rdclk_sig ),

.rdreq ( rdreq_sig ),

.wrclk ( wrclk_sig ),

.wrreq ( wrreq_sig ),

.q ( q_sig ),

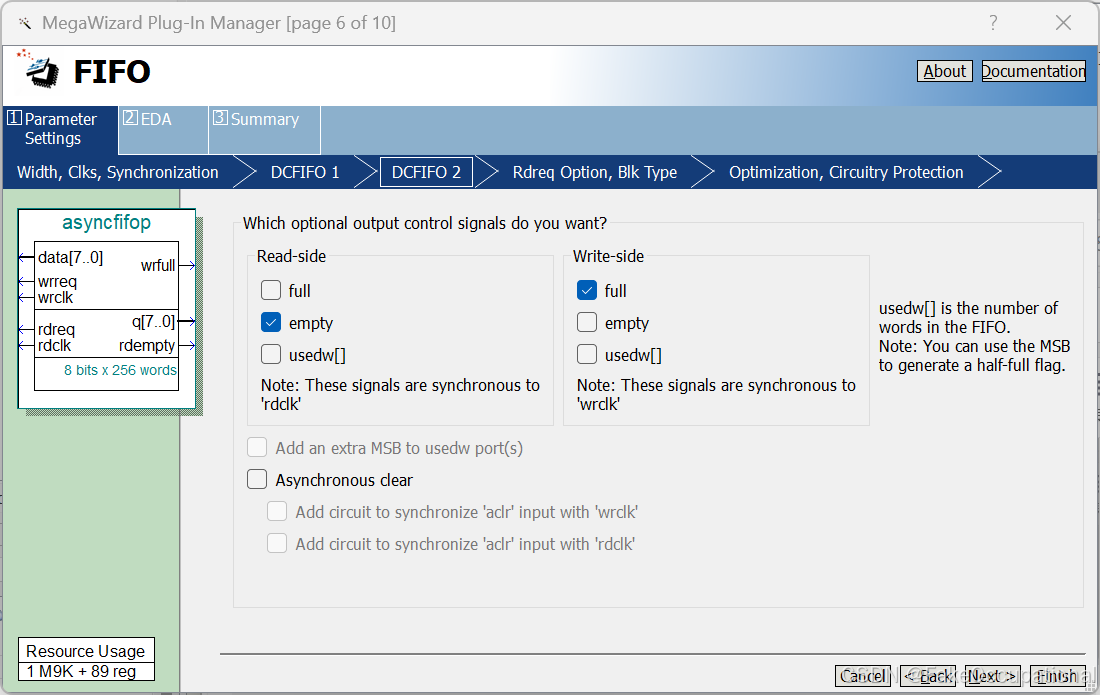

.rdempty ( rdempty_sig ),

.wrfull ( wrfull_sig )

);

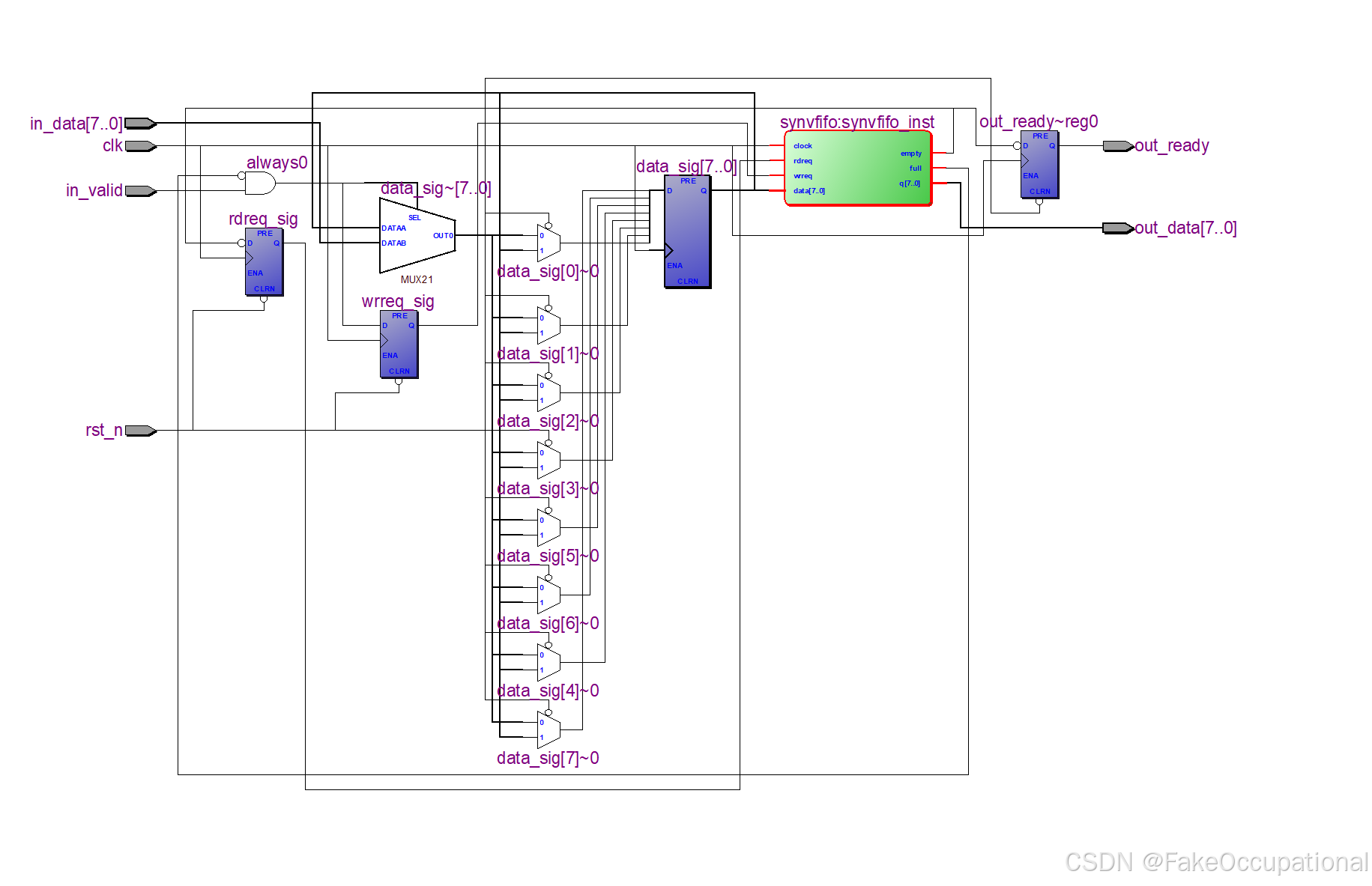

synvfifo_inst 使用示例

module simplefifo (

input wire clk, // 系统时钟

input wire rst_n, // 异步复位信号

input wire [7:0] in_data, // 输入数据

input wire in_valid, // 输入数据有效信号

output reg out_ready, // 输出准备好信号

output wire [7:0] out_data // 处理后的输出数据

);

// FIFO接口信号

wire full_sig; // FIFO满标志

wire empty_sig; // FIFO空标志

reg wrreq_sig; // 写请求信号

reg rdreq_sig; // 读请求信号

reg [7:0] data_sig; // 写入FIFO的数据

wire [7:0] q_sig; // FIFO输出数据

wire [4:0] usedw_sig; // FIFO已用深度

// 实例化FIFO

synvfifo synvfifo_inst (

.clock ( clk ),

.data ( data_sig ),

.rdreq ( rdreq_sig ),

.wrreq ( wrreq_sig ),

.empty ( empty_sig ),

.full ( full_sig ),

.q ( q_sig ),

.usedw ( usedw_sig )

);

// 数据写入逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

wrreq_sig <= 0;

end else if (in_valid && !full_sig) begin

wrreq_sig <= 1;

data_sig <= in_data;

end else begin

wrreq_sig <= 0;

end

end

// 数据读取和处理逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

rdreq_sig <= 0;

out_ready <= 0;

end else begin

if (!empty_sig) begin

rdreq_sig <= 1;

out_ready <= 1;

end else begin

rdreq_sig <= 0;

out_ready <= 0;

end

end

end

// 将FIFO输出赋值给处理后的输出数据

assign out_data = q_sig;

endmodule

7521

7521

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?