一、FIFO IP 核简介

FIFO(First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写方式。与 ROM 或 RAM 的按地址读写方式不同,FIFO 的读写遵循“先进先出”的原则,即数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以FIFO存储器没有地址线。FIFO 有一个写端口和一个读端口外部无需使用者控制地址,使用方便。

FIFO存储器主要是作为缓存,应用在同步时钟系统和异步时钟系统中,在很多的设计中都会使用,后面实例中如:多比特数据做跨时钟域的转换、前后带宽不同步等都用到了FIFO。FIFO 根据读写时钟是否相同,分为SCFIFO(同步FIFO)和 DCFIFO(异步FIFO),SCFIFO 的读写为同一时钟,应用在同步时钟系统中; DCFIFO 的读写时钟不同,应用在异步时钟系统中。

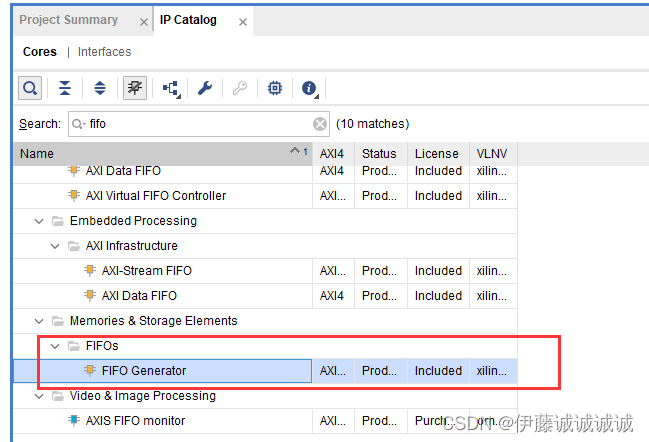

1.SCFIFO IP 核配置

下面来看一下同步fifo的配置:

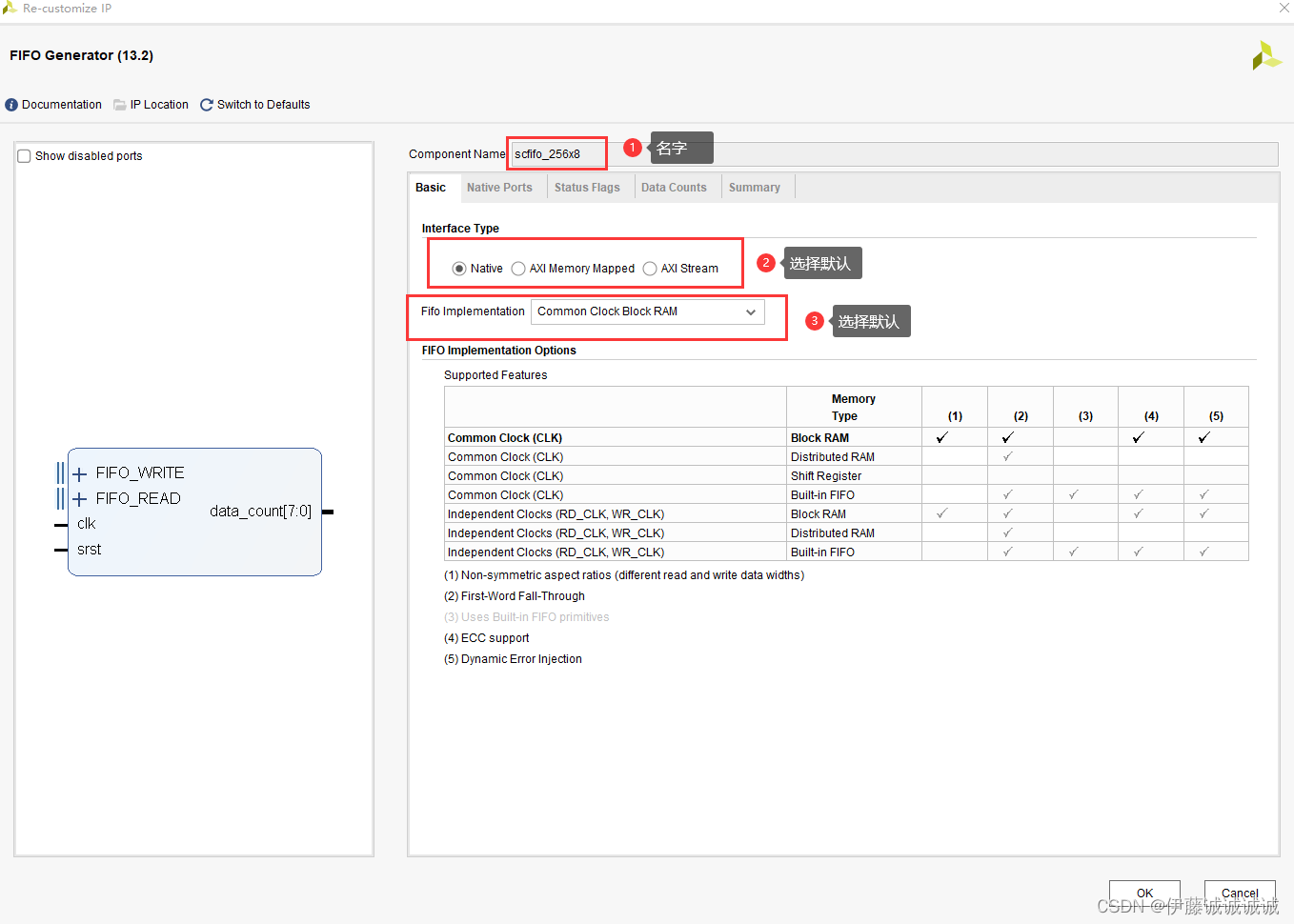

① 框中我们输入IP核的命名, 后面实例化IP 的时候都是使用的该名字,这里所取的名字最好是和该 IP 核相关,因为本节我们主要讲解同步 fifo,给该 IP 核取名为scfifo_256x8,让人一看名字就知道我们调用的 scfifo 是 256 个深度 8 位宽的。

① 框中我们输入IP核的命名, 后面实例化IP 的时候都是使用的该名字,这里所取的名字最好是和该 IP 核相关,因为本节我们主要讲解同步 fifo,给该 IP 核取名为scfifo_256x8,让人一看名字就知道我们调用的 scfifo 是 256 个深度 8 位宽的。

② 框是选中 FIFO 的接口类型, 这里我们按默认选择“Native” 即可。

③ 框是选中 FIFO 的类型, 以及使用什么资源来实现。 这里我们选择“Common Clock Block RAM”使用块 RAM 来实现同步 FIFO;其中 Common Clock 表示是同步 FIFO,Block RAM 表示的是块 RAM 资源。

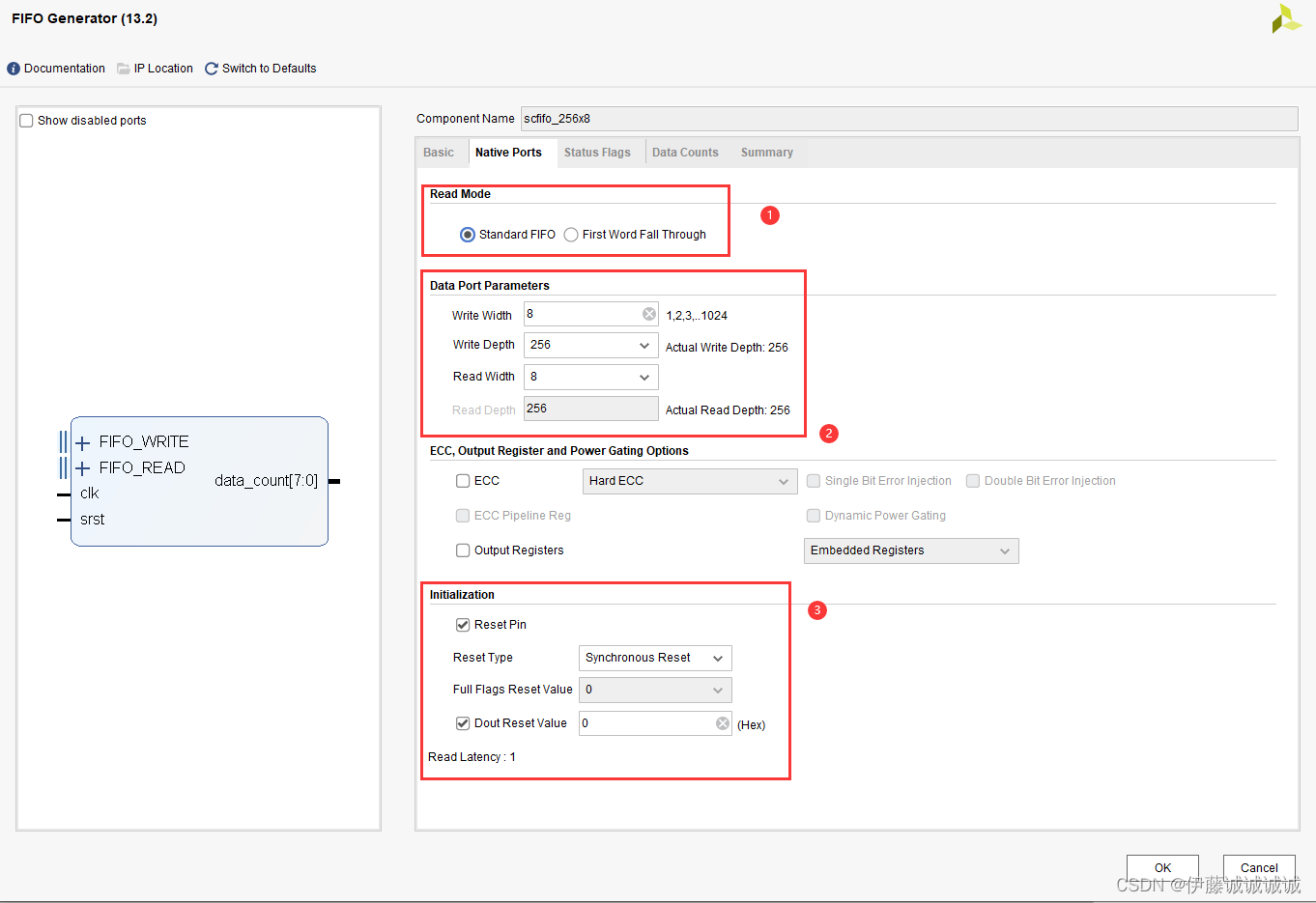

①框中是对模式的选择,这里我们选

文章介绍了FIFO(FirstInFirstOut)的基本概念,特别是同步FIFO(SCFIFO)的配置过程,包括IP核的命名、接口类型、存储器类型的选择。在配置中,设置了数据位宽和深度,并讨论了复位信号、状态标志的生成。接着展示了如何在Verilog中例化SCFIFOIP核,并给出了Testbench的仿真测试文件,用于验证FIFO的读写操作。

文章介绍了FIFO(FirstInFirstOut)的基本概念,特别是同步FIFO(SCFIFO)的配置过程,包括IP核的命名、接口类型、存储器类型的选择。在配置中,设置了数据位宽和深度,并讨论了复位信号、状态标志的生成。接着展示了如何在Verilog中例化SCFIFOIP核,并给出了Testbench的仿真测试文件,用于验证FIFO的读写操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?