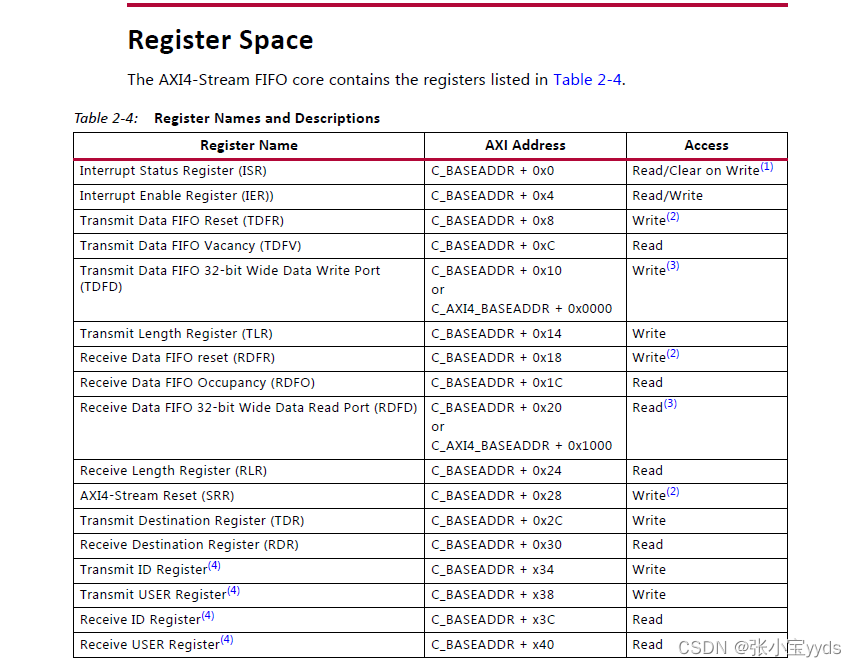

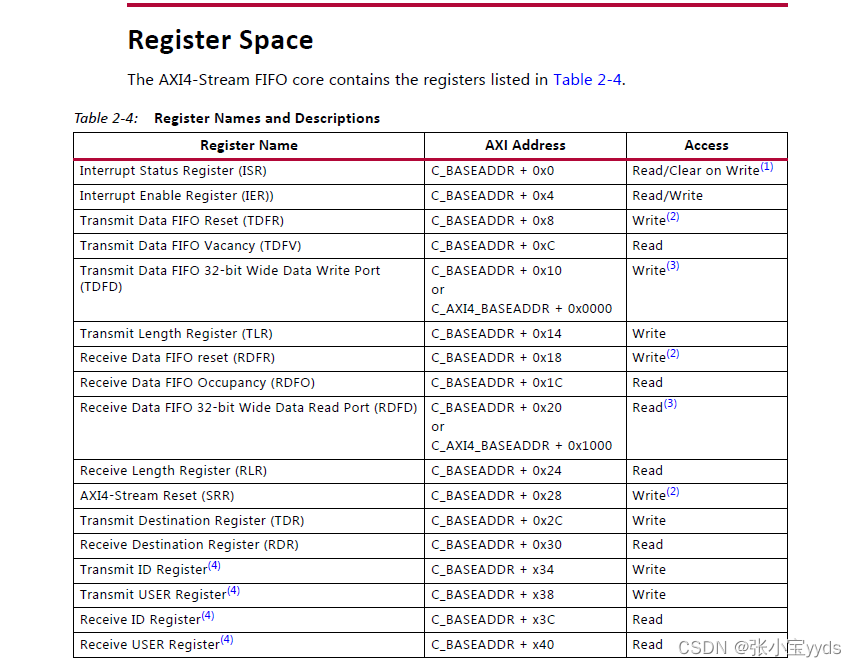

一:寄存器描述

二:写操作流程

1.读TDFV(0xC)寄存器 //查询FIFO可写次数

2.写TDFD(lite接口:0x10,full接口:0x0)寄存器 //写待发数据

3.写TLR (0x14)寄存器 &

本文详细介绍了寄存器在存储转发模式和直通模式下的写操作与读操作流程,包括查询FIFO可写次数、写入待发数据、设置包长度及读取接收数据的具体步骤。

本文详细介绍了寄存器在存储转发模式和直通模式下的写操作与读操作流程,包括查询FIFO可写次数、写入待发数据、设置包长度及读取接收数据的具体步骤。

1.读TDFV(0xC)寄存器 //查询FIFO可写次数

2.写TDFD(lite接口:0x10,full接口:0x0)寄存器 //写待发数据

3.写TLR (0x14)寄存器 &

4852

4852

3384

3384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?