1.1 JTAG to AXI Master说明

参考文档:

1.xilinx PG174 <<JTAG to AXI Master v1.2 LogiCORE IP Product Guide>>

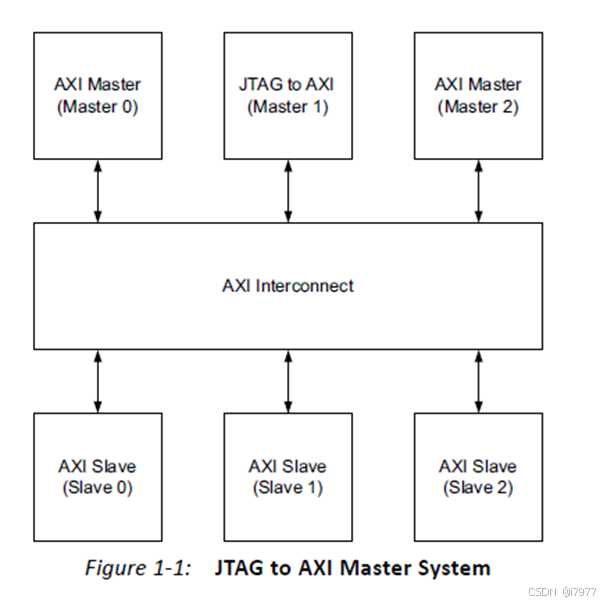

下图展示了一个使用JTAG to AXI master IP作为AXI主控核心的AXI系统。JTAG to AXI master IP主机接口没有自己的地址空间,他可以对所有的寻址空间进行访问,即它可以和挂载到互联矩阵上的所有从机通信。同时它可以和系统中的另一个axi主机共存(例如处理器)。

JTAG to AXI Master IP core可以生成AXI事务,并将AXI信号连接到可编程逻辑。该IP只有一个axi主机接口,接口具体参数均可以配置。通过该主机接口,可以在没有处理器系统的情况下,操作axi从机外围设备,用于debug外围设备。

图1:ip 接口

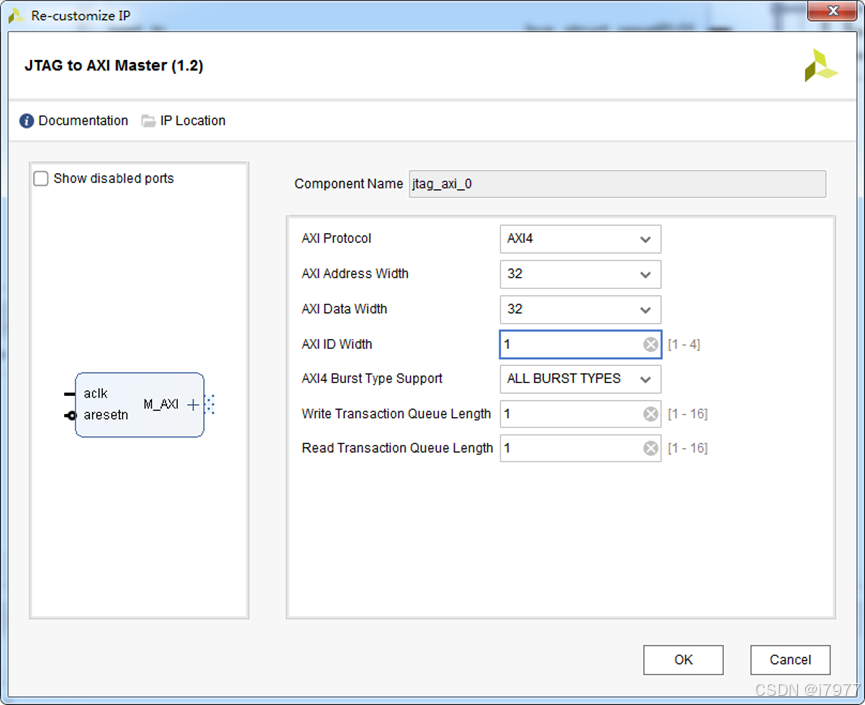

1.2 JTAG to AXI Master IP配置

配置界面如下图所示,根据实际需要和axi协议要求配置即可。不做赘述。

1.3 BD设计

该BD设计硬件运行环境为zcu104开发板。通过调用JTAG to AXI Master ip连接到DDR MIG核的axi接口,对DDR进行读写测试。框图如下:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1398

1398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?