摘要

FreeRTOS为了保证实时性要求严格的中断能及时响应,在屏蔽任务切换时,只屏蔽了优先级比较低的部分中断。而可被屏蔽的这些中断可以保证内核的临界区不被破坏,因此这些中断也能使用部分内核API。在这样的中断发送信号量,可以让有时序性要求较高的任务或信号量来自于外设的任务及时获取信号量并运行。

本文将介绍CortxM7的相关中断寄存器,并说明如何配置FreeRTOS中与中断有关的宏。最后说明想要运行操作系统内核API的中断时,该中断优先级的设置范围。

另外,本文还额外说明了pvPortMalloc()这个堆内存申请函数不能在中断中使用的原因。

CortxM7的相关中断寄存器

参见:《ARM Cortex-M7 Devices Generic User Guide》

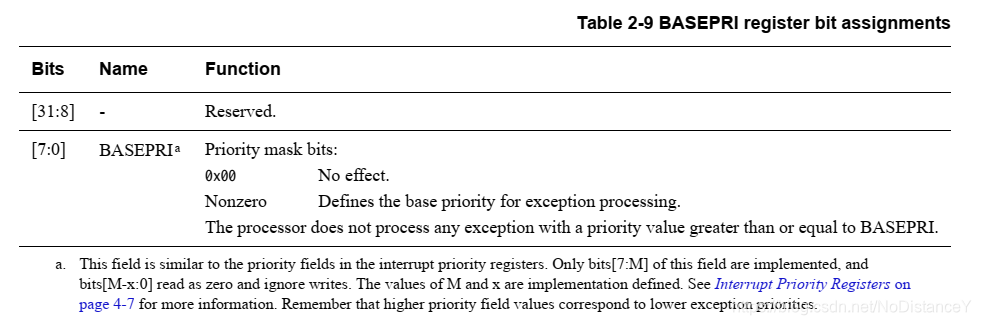

1、基础优先级屏蔽寄存器:

Base Priority Mask Register

The BASEPRI register defines the minimum group priority for exception processing. When

BASEPRI is set to a nonzero value, it prevents the activation of all exceptions with the same or

lower group priority level as the BASEPRI value.

表格下方有一段小注释,这就是我们从其他二手渠道中知道的优先级寄存器中的值越大,优先级越小的来源。

Remember that higher priority field values correspond to lower exception priorities.

在 Table 4-9中也强调了这一说法:

Each priority field holds a priority value, 0-255. The lower the value, the greater the priority of the corresponding interrupt.

If enabled, the processor can implement only bits[7:n] of each field, bits[n-x:0] read as zero and ignore writes. The values of n and x are implementation defined.

stm32h7提供的系统初始化函数中,就设置了默认的中断分组:

HAL_Init();→HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4);→SCB->AIRCR

本文深入解析了FreeRTOS在Cortex-M7处理器上如何管理和配置中断,以确保实时性和任务切换的效率。详细介绍了相关寄存器如BASEPRI和AIRCR的作用,以及如何设置中断优先级分组。同时,阐述了使用内核API的中断优先级范围,解释了为何不能在中断中使用pvPortMalloc()函数。

本文深入解析了FreeRTOS在Cortex-M7处理器上如何管理和配置中断,以确保实时性和任务切换的效率。详细介绍了相关寄存器如BASEPRI和AIRCR的作用,以及如何设置中断优先级分组。同时,阐述了使用内核API的中断优先级范围,解释了为何不能在中断中使用pvPortMalloc()函数。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3927

3927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?