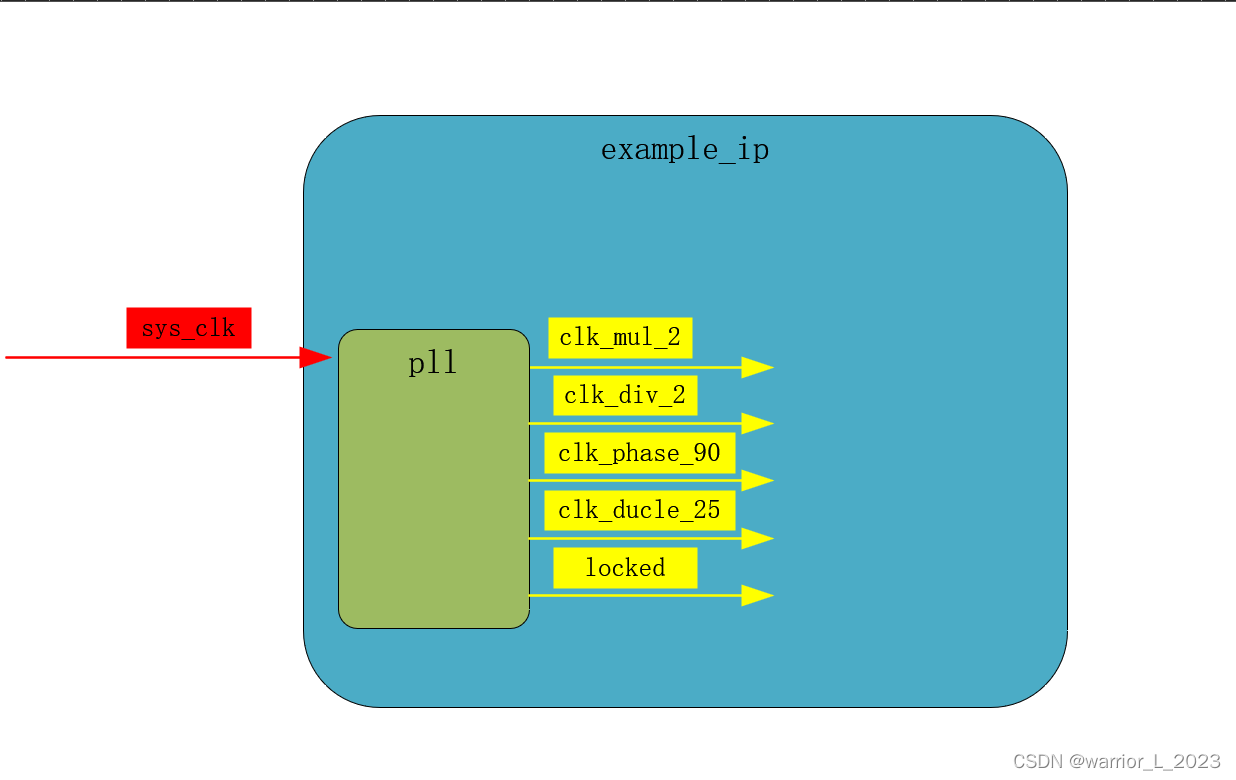

PLL:

module top(

input wire sys_clk ,

output wire clk_mul_2 ,

output wire clk_div_2 ,

output wire clk_phase_90 ,

output wire clk_ducyle_2 ,

output wire locked

);

pll pll_insert(

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div_2 ),

.c2 ( clk_phase_90 ),

.c3 ( clk_ducyle_2 ),

.locked ( locked )

);

endmodule

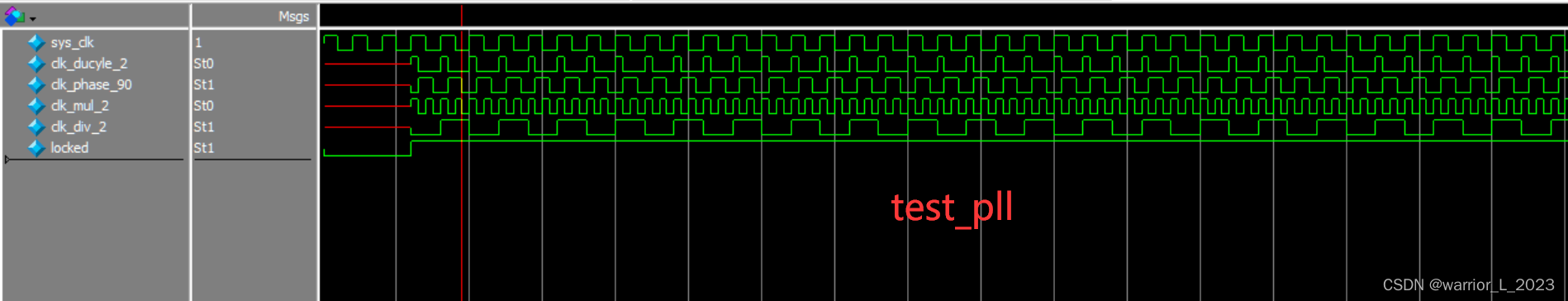

`timescale 1ns/1ns

module test_pll ();

reg sys_clk ;

wire clk_mul_2 ;

wire clk_div_2 ;

wire clk_phase_90 ;

wire clk_ducyle_2 ;

wire locked ;

top top_insert(

.sys_clk ( sys_clk ) ,

.clk_mul_2 ( clk_mul_2 ) ,

.clk_div_2 ( clk_div_2 ) ,

.clk_phase_90 ( clk_phase_90 ) ,

.clk_ducyle_2 ( clk_ducyle_2 ) ,

.locked ( locked )

);

parameter CYCLE = 20 ;

initial begin

sys_clk <= 1'b1 ;

end

always #(CYCLE / 2) sys_clk <= ~ sys_clk ;

endmodule

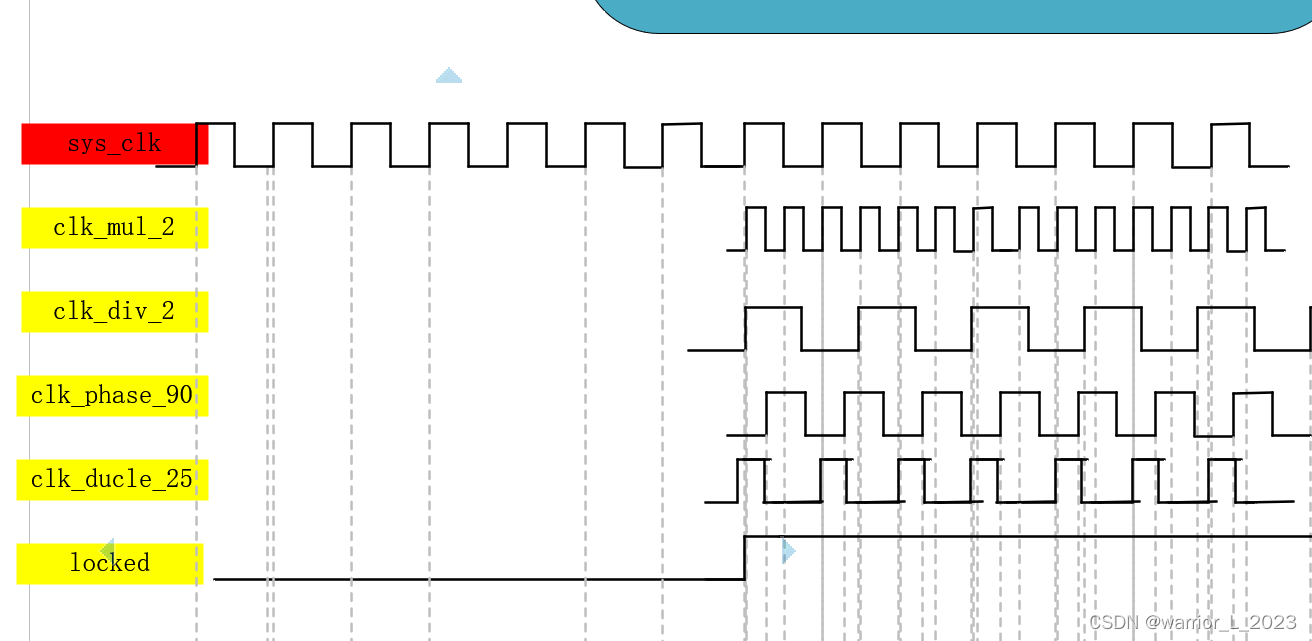

该文章详细描述了一个使用Verilog语言编写的PLL(锁相环路)模块,它用于处理系统时钟信号,包括乘法器、除法器、相位调整和周期调整功能。测试模块展示了如何配置和驱动PLL,以及如何在仿真环境中设置时钟周期。

该文章详细描述了一个使用Verilog语言编写的PLL(锁相环路)模块,它用于处理系统时钟信号,包括乘法器、除法器、相位调整和周期调整功能。测试模块展示了如何配置和驱动PLL,以及如何在仿真环境中设置时钟周期。

1224

1224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?