本周开始了FPGA的学习,之前在FPGA上的知识可以说基本上是空白,以下内容仅供参考,如有不恰当之处,欢迎指正。

**

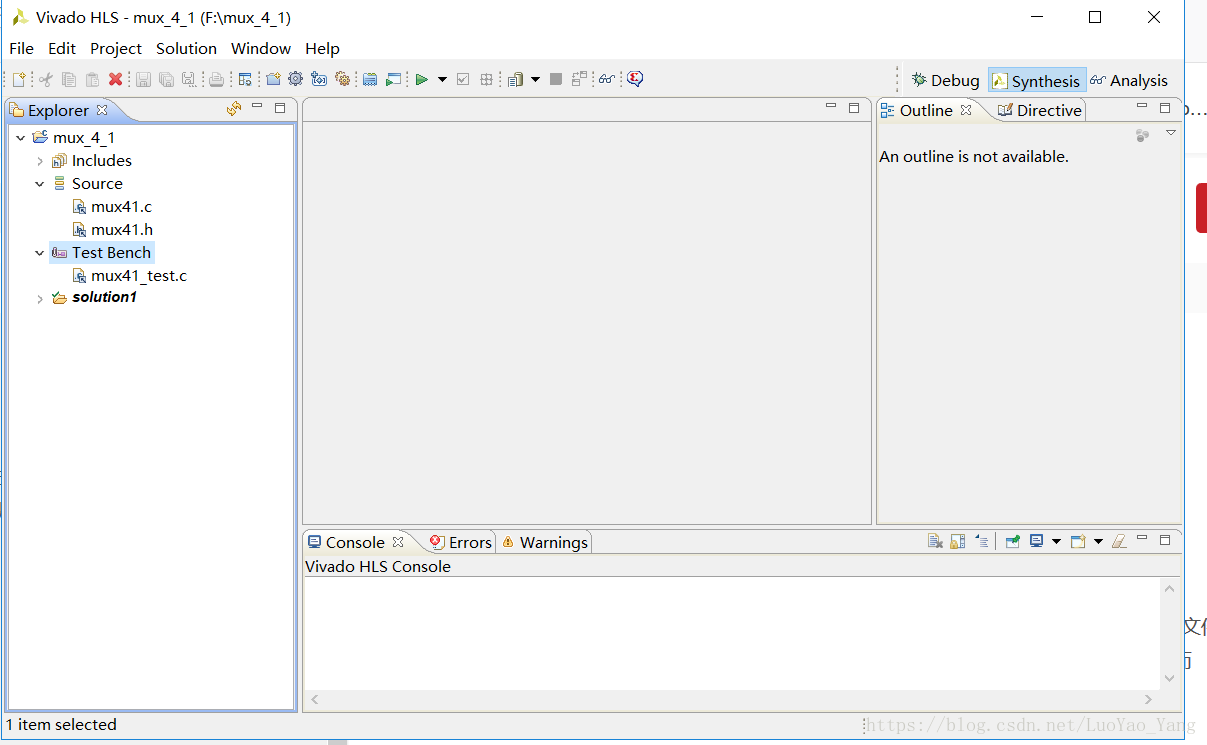

1、创建工程

**

1、1在进行生成IP Core之前,首先安装Vivado HLS,这里我安装的是Vivado HLS 2016.4版本。

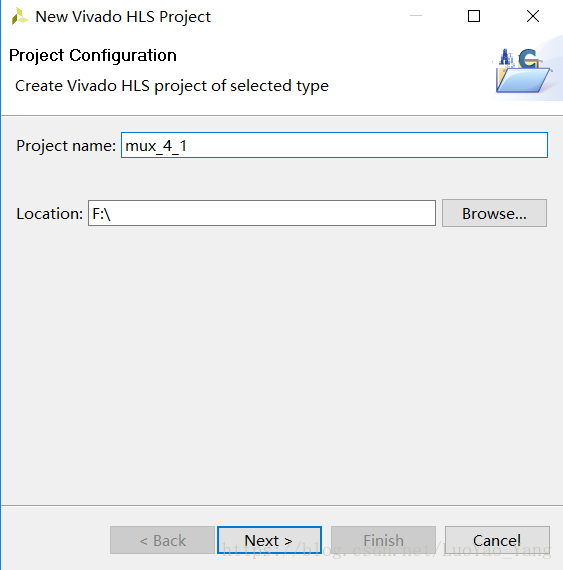

1、2打开Vivado HLS以后,可点击Creat New Project或者通过File->New Project来对新工程进行创建。此处我们创建一个最简单的工程,四选一数据选择器。在设置完成Project name和Location之后,点击Next,进入下一步。

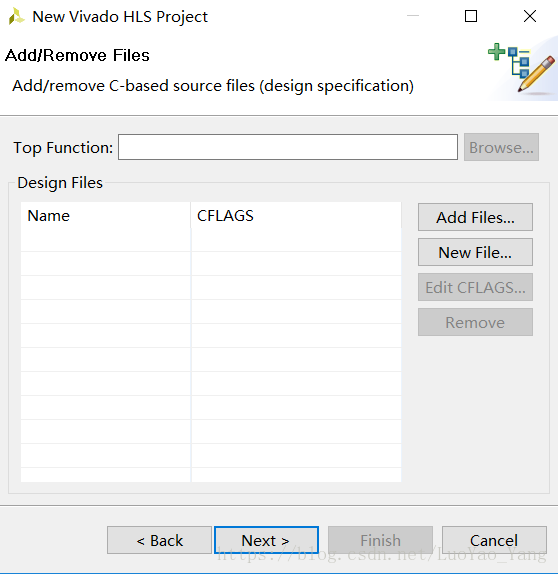

1、3这里需要填入的是Top Function以及Design Files,这两个内容可以现在就加入文件,也可以在后面进行加入或者在后面进行编写。Top Function是你指定要合成的顶级函数,而Design Files是设计时需要用到或者调用的一些函数方法的定义。

1、4Testbench中是加入后续需要进行测试或者验证的C语言代码,同样的可以现在就进行添加文件,或者后面在testbench中通过add file或者new file进行添加和编写相应程序。

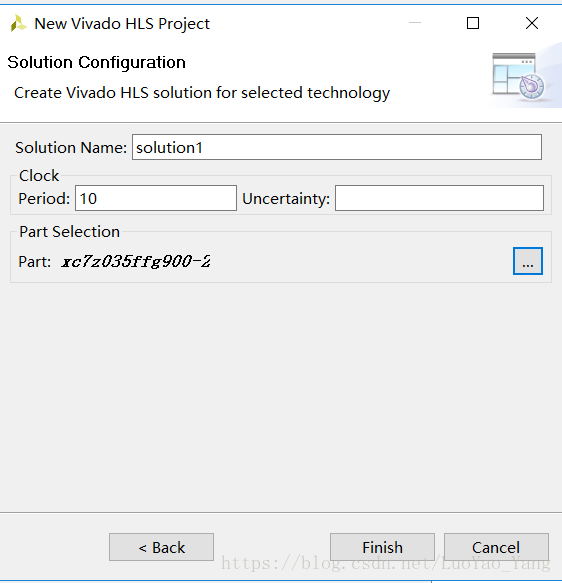

1、5紧接着是创建Solution,这里会有以下参数需要进行设置:Solution的名称以及Clock时钟周期(默认以ns为单位)和Uncertainty不确定性。在part selection中选择相应的芯片点击finish,前期的设置工作就算完成了。

2、进行相关仿真和RTL的合成及输出

2、1由于上一步没有对source和testbench添加文件,可在此点击右键添加已经存在的文件或者添加新文件进行编写。这里我个人的理解是source定义的是一些后面用得到的方法,而testbench是对这些方法的检测。

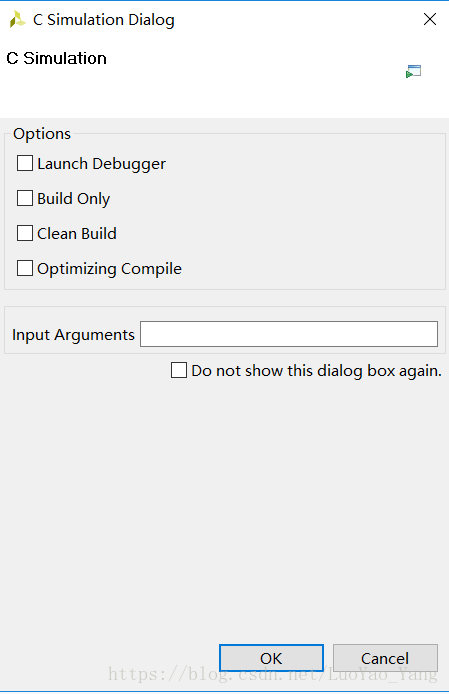

2、2点击C Simulation,进行C代码的仿真,此时会出现以下界面:

Launch Debugger:编译C代码并自动打开调试透视图,从中可设置断点单个执行语句,来看每个变量的值。

Build only:仅编译,不运行

clean build:在编译代码之前从项目中删除任何现有的可执行的文件和目标文件

optimized compile:默认情况下,设计使用调试信息进行编译。

这里直接点击OK,不用进行选择

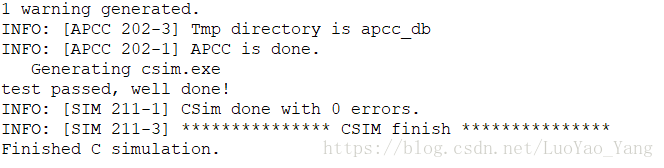

可以看到Finished C simulation的提示

在运行了C simulation后,会生成csim文件夹。

文件夹csim / build是与C模拟相关的所有文件的主要位置。

(1)测试平台读取的任何文件都将复制到此文件夹中。

(2)创建C可执行文件csim.exe并在此文件夹中运行。

(3)测试平台写入的任何文件都在此文件夹中创建。

如果在C模拟对话框中选择了“build only”选项,则会在此文件夹中创建文件csim.exe,但不会执行该文件。

文件夹csim / report包含C模拟的日志文件。

2、3使用C Synthesis设计合成RTL

因为之前没有对Top Function进行设置,这里先通过project settings进行设置,然后点击Solution->Run C Synthesis->activate soltion

运行成功后,会生成syn文件夹,其中report文件夹是对相应参数的报告文件,verilog,vhdl和systemc文件夹包含输出RTL文件。

2.4在此之后,点击Export RTL 就可以生成IP Core

本文介绍了FPGA学习的基础步骤,包括创建工程、设置TopFunction、添加DesignFiles和Testbench等内容,并详细记录了从创建项目到RTL合成及输出IPCore的全过程。

本文介绍了FPGA学习的基础步骤,包括创建工程、设置TopFunction、添加DesignFiles和Testbench等内容,并详细记录了从创建项目到RTL合成及输出IPCore的全过程。

2768

2768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?