vivado HLS 为赛灵思开发的高层次综合工具,可实现直接使用 C,C++ 以及 System C 语言对Xilinx的FPGA器件进行编程。赛灵思官方给出了ug902文档,很详细的介绍了官方提供的各种库,以及HLS的使用方法。本文将介绍如何在zynq上使用vivado HLS生成的ip核。

一、创建一个vivado HLS工程

具体的vivado HLS工程创建以及优化方法,可参考博客:https://blog.youkuaiyun.com/weixin_39290638/article/details/80228806

本文只作简要介绍。

首先,在solution中一定要选择所使用的正确的芯片型号,本文所使用的芯片型号为xc7z020clg400-2,如图所示:

然后,确保top function正确:

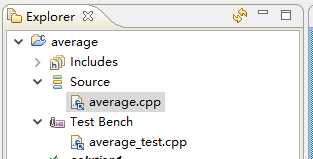

编写源码和test bench,设置好接口:

本文介绍了如何在Zynq平台上使用vivado HLS生成的IP核。首先,详细说明了创建vivado HLS工程的步骤,包括选择正确的芯片型号、设置接口和验证代码。接着,展示了在vivado block design中导入和配置自定义IP核的过程。最后,讲解了PS端如何驱动IP核,包括初始化、调用函数读取PL端数据的细节。

本文介绍了如何在Zynq平台上使用vivado HLS生成的IP核。首先,详细说明了创建vivado HLS工程的步骤,包括选择正确的芯片型号、设置接口和验证代码。接着,展示了在vivado block design中导入和配置自定义IP核的过程。最后,讲解了PS端如何驱动IP核,包括初始化、调用函数读取PL端数据的细节。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

451

451