1 generated clock的定义

generated clock是有master clock衍生而来,master clock指的是由create_clock定义的clock

当基于master clock生成一个新的clock时,可以将这个新的clock定义为generated clock

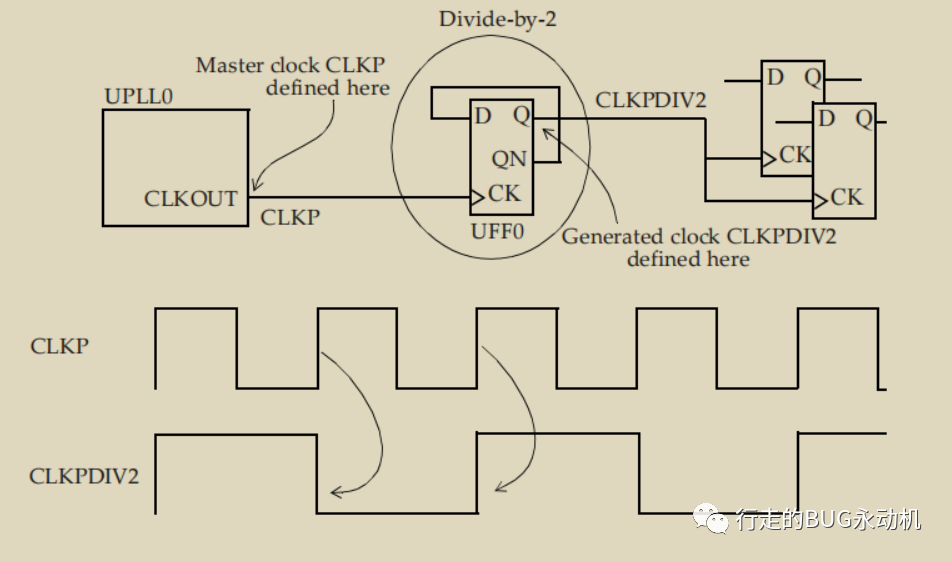

举个栗子,如下图所示,UFF0的功能是将时钟CLKP进行二分频,那么便可以在UFF0的输出端UFF0/Q定义一个generated clock

CLKP在经过UFF0后,后续电路的时钟周期发生了更改,但STA并不知道后续电路的时钟发生了变化,更不知道新的clock的周期是多少,因此需要定义generated clock,让STA知道后续电路的clock已经发生了更改以及新的clock周期是多少

# 创建一个master clock

create_clock -name CLKP 10 \

[get_pins UPLL0/CLKOUT]

# 新的clock被命名为CLKDIV2

# 它的master clock 在UPLL0/CLKOUT处定义

# 新的clock是master clock的二分频

# 新的clock在UFF0/Q处定义

create_generated_clock \

-name CLKPDIV2 \

-source UPPL0/CLKOUT \

-divide_by 2 \

[get_pins UFF0/Q]

2 generated clock与master clock的区别

从上面一张图中可以看到,master clock是由电路推出的,generated clock也是由电路推出的,也就是说,其实我们是可以在UFF0/Q定义一个master clock的

本文详细解析了generatedclock的创建原理、与masterclock的区别,展示了如何在门控电路、时钟分频和边缘触发场景中运用。了解了如何通过edges和edge_shift精确定义时钟周期,并探讨了invert选项的作用。关键概念包括clock domain、clockpath和latency。

本文详细解析了generatedclock的创建原理、与masterclock的区别,展示了如何在门控电路、时钟分频和边缘触发场景中运用。了解了如何通过edges和edge_shift精确定义时钟周期,并探讨了invert选项的作用。关键概念包括clock domain、clockpath和latency。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2526

2526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?