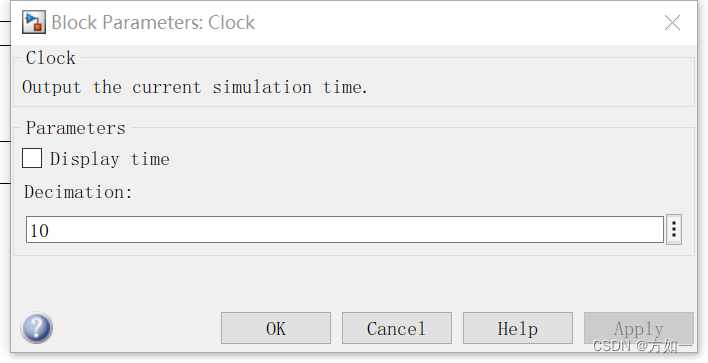

clock:提供仿真时间

Clock模块可以在窗口中显示每一步仿真当时的仿真时间。

Display time:勾选后可以在在仿真过程中显示当前仿真时间,如果不显示,则可将其输人到工作区中。

Decimation:时间更新获取的增量,可以是任意正整数, 默认为10则表示系统将以1s、2s、3s…10s依次递增。

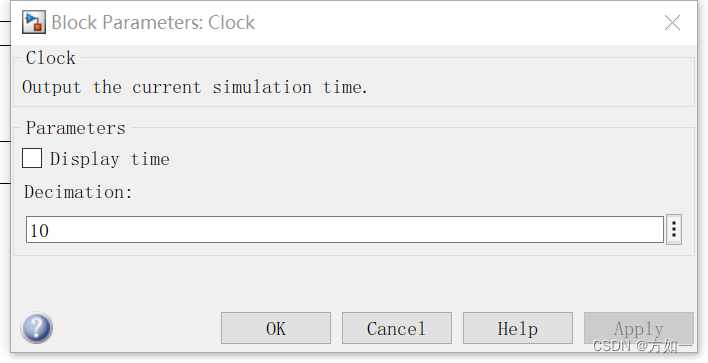

Clock模块可以在窗口中显示每一步仿真当时的仿真时间。

Display time:勾选后可以在在仿真过程中显示当前仿真时间,如果不显示,则可将其输人到工作区中。

Decimation:时间更新获取的增量,可以是任意正整数, 默认为10则表示系统将以1s、2s、3s…10s依次递增。

683

683

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?