Verilog HDL允许标量net信号值具有各种未知值和不同的强度级别或强度级别组合,从而为信号争用、双向导通门、电阻式 MOS 器件、动态 MOS、电荷共享和其他与技术相关的网络配置提供精确建模。这种多级逻辑强度建模将信号组合解析为已知或未知值,从而以更高的精度表示硬件行为。

逻辑强度指定应包括两个部分:

a) 网络net值为0的强度,称为strength0,指定为以下之一:

supply0 strong0 pull0 weak0 highz0

b) 网络net值为1的强度,称为strength1,指定为以下之一:

supply1 strong1 pull1 weak1 highz1

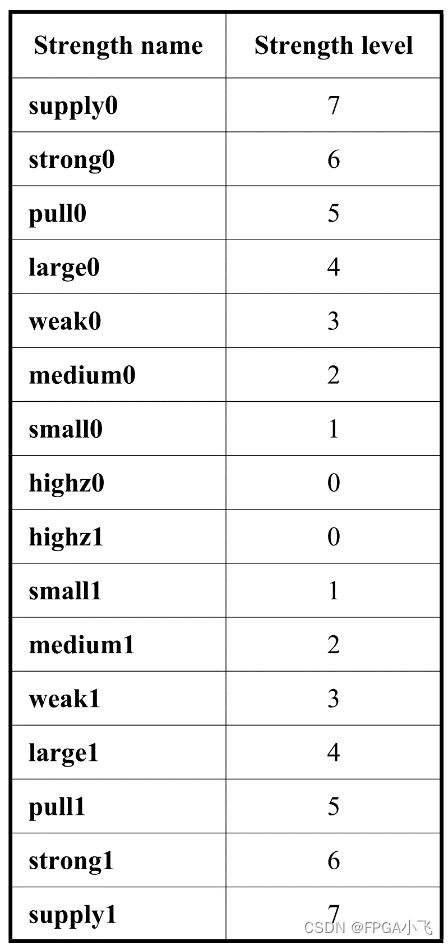

(highz0, highz1) 或(highz1, highz0) 的组合是非法的。表1为标量net信号值的强度等级值:

表1:标量net信号值的强度等级

表1列出了四种驱动强度等级:

supply strong pull weak

具有这4种驱动强度的信号从对应的门逻辑输出和连续赋值输出就开始生效。

在表1中,有三种电荷储存强度(charge storage strengths):

large medium small

具有电荷存储强度的信号应来自于trireg类型的net信号。

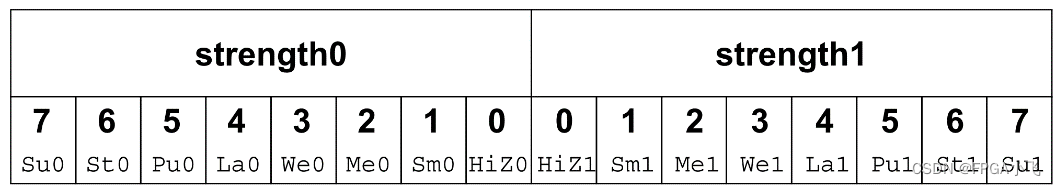

现在为了方便讨论,可以将表1中的信号强度进一步划分为图1:

图1:标量net信号值的强度标尺

如果已知net信号的值,则该信号的强度级别都应在图1所示的strength0或strength1部分内。如果net信号值未知,则我们认为其强度等级应同时在strength0和strength1部分。对于net信号值为z的情况,其强度等级应仅位于图1的strength0或strength1强度为0的Hiz0/1部分内。

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

6685

6685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?