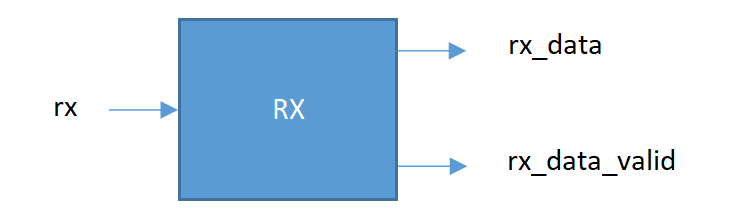

3.RX模块设计

经过TX模块的设计分析之后,现在对RX是不是就不那么惧怕啦?我们还是按照老规矩来拆解这个模块:

逻辑关系:

rx表示接收到的单bit数据(其实它就是一段持续的电流,忽高忽低,想象一下);rx_data表示生成的并行数据;rx_data_valid表示对rx_data进行使能。

设计思路:

(1)看输出,rx_data和rx_data_valid。而rx_data来源于rx,由单bit数据经过串行转并行生成,而rx_ready取决于当前状态,rx_data没有生成的时候置0,当rx_data生成后就置1。

问题1)怎么定义rx_data_valid?

解释:当rx_data生成后,就可以置1。怎么判定数据

本文详细介绍了UART RX模块的设计思路和逻辑关系,包括串行转并行的过程,检测下降沿的方法,以及各个阶段的数据采样和校验策略。通过分析,解释了如何在检测到下降沿后进行数据接收,以及如何在特定时钟时刻进行采样和校验,最终生成有效的rx_data和rx_data_valid信号。

本文详细介绍了UART RX模块的设计思路和逻辑关系,包括串行转并行的过程,检测下降沿的方法,以及各个阶段的数据采样和校验策略。通过分析,解释了如何在检测到下降沿后进行数据接收,以及如何在特定时钟时刻进行采样和校验,最终生成有效的rx_data和rx_data_valid信号。

订阅专栏 解锁全文

订阅专栏 解锁全文

551

551