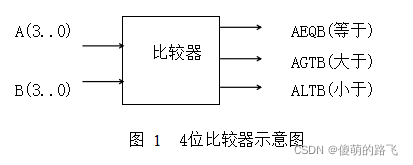

目的:实现一个4位二进数据比较器。

分析:两个操作数的比较有三种结果,即A等于B,A大于B和A小于B。两个4位二进制比较器,构建比较器表如下。

| 输入 | 输出 | |||

| A | B | AGQB | AGTB | ALTB |

| A = B | 1 | 0 | 0 | |

| A > B | 0 | 1 | 0 | |

| A < B | 0 | 0 | 1 | |

转向控制语句:next 和 exit

(1)next语句

跳转到本次循环的起始位置,开始下一次循环。

(2)exit语句

跳转到本次循环的结束位置,结束循环。

程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity num_compare is

port(

Ai,Bi :in std_logic_vector(3 downto 0);

AEQB,AGTB,ALTB :out std_logic --AEQB-Ai等于Bi,AGTB-Ai大于Bi,ALTB-Ai小于Bi

);

end num_compare;

architecture behave of num_compare is

begin

process(Ai,Bi)

begin

for n in 3 downto 0 loop

if(Ai(n) = Bi(n)) then

AEQB <= '1';

AGTB <= '0';

ALTB <= '0';

next; --回到当前循环起始处进行第二轮比较

elsif(Ai(n) > Bi(n)) then

AEQB <= '0';

AGTB <= '1';

ALTB <= '0';

exit; --比较结束,跳出循环

elsif(Ai(n) < Bi(n)) then

AEQB <= '0';

AGTB <= '0';

ALTB <= '1';

exit; --比较结束,跳出循环

end if;

end loop;

end process;

end behave;

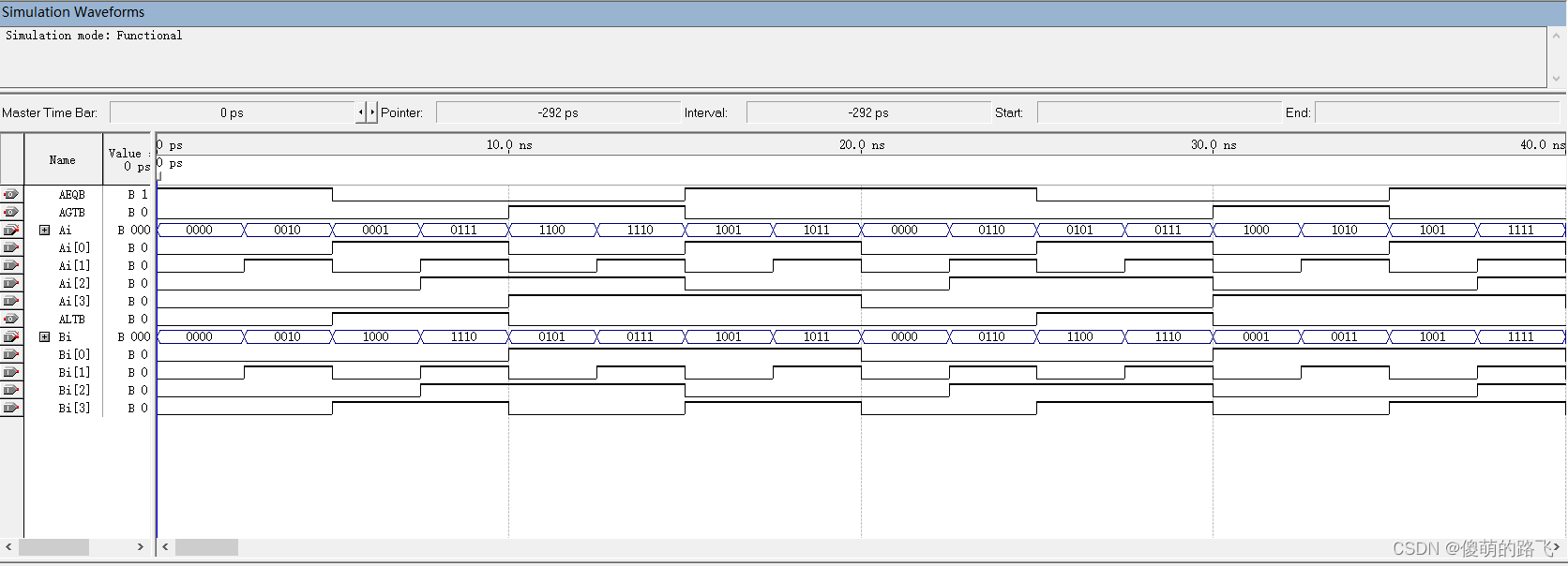

仿真波形图

本文记录了使用VHDL语言设计一个4位二进制数据比较器的过程,详细介绍了比较器的三种输出状态:相等、大于、小于,并探讨了VHDL中的next和exit语句在循环控制中的应用,同时提供了程序代码及仿真波形图作为验证。

本文记录了使用VHDL语言设计一个4位二进制数据比较器的过程,详细介绍了比较器的三种输出状态:相等、大于、小于,并探讨了VHDL中的next和exit语句在循环控制中的应用,同时提供了程序代码及仿真波形图作为验证。

7712

7712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?