问题现象

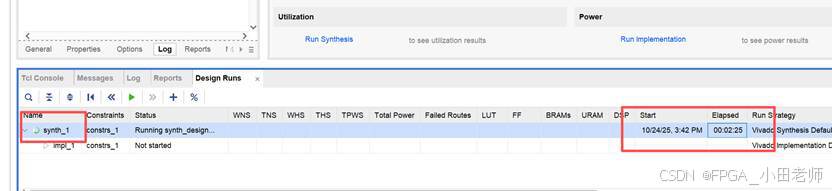

程序综合一直卡在了Run Synth Design………等了好久好久,还是没有结果

问题分析:

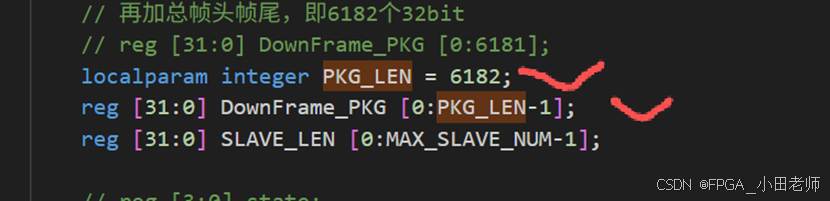

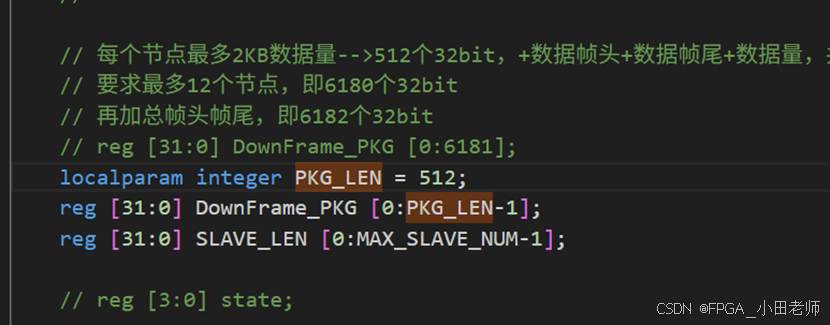

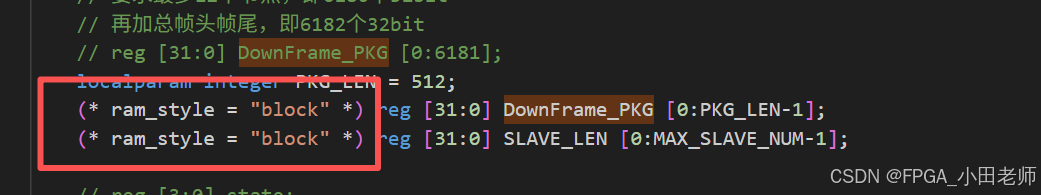

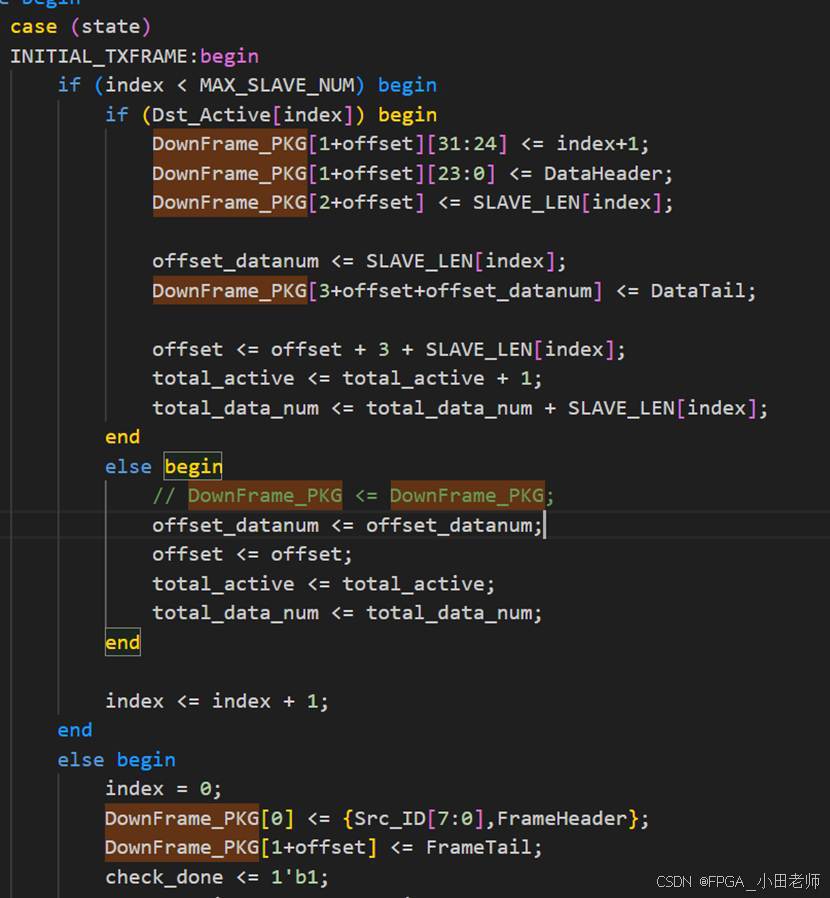

出现这种情况,一般考虑是资源超了的原因,回顾程序,可能出问题的地方在于,程序中有一个很大的数组,在做大规模存储,如下。

那是FF超了?BRAM超了?还是什么其它的原因呢?根据资源评估的计算来说,RAM资源应该是足够的,鉴于此,我们开始问题定位。

问题定位:

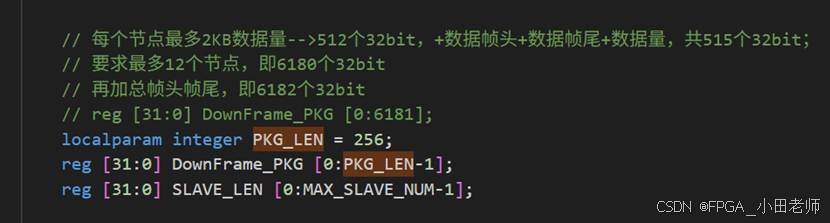

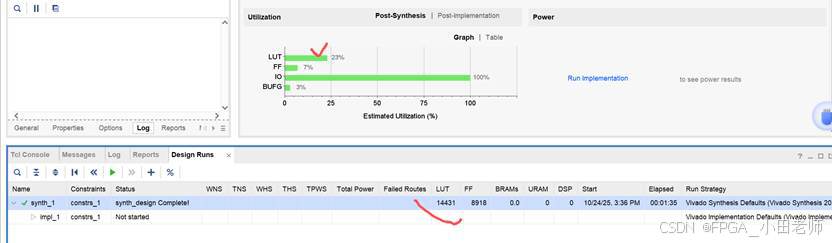

第一步,将PKG_LEN修改为256,综合大于1.5min,LUT资源23%,FF占用7%

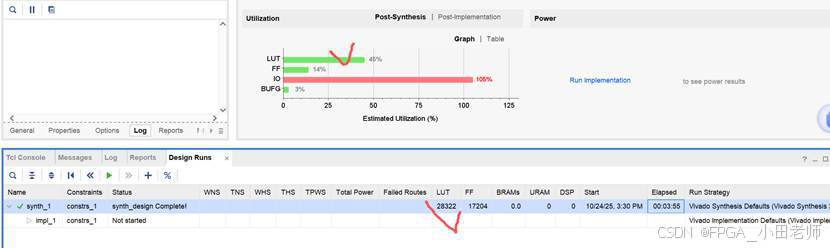

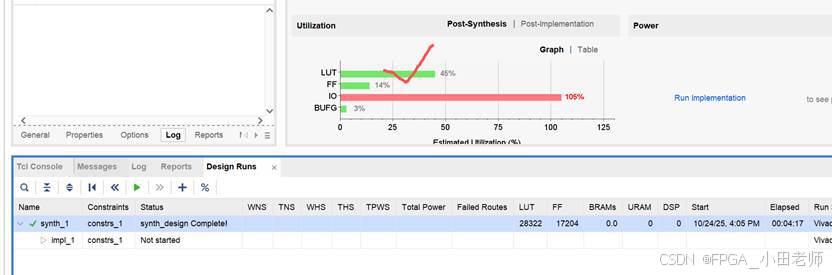

第二步,将PKG_LEN修改为512,综合大约4min,LUT资源占用45%,FF占用14%

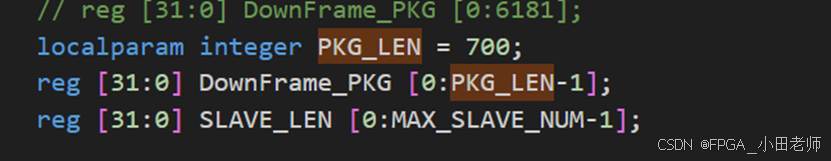

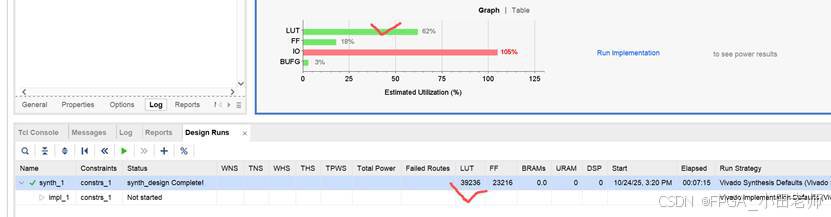

第三步,将PKG_LEN修改为700,综合大约7min,LUT资源占用62%,FF占用18%

第四步,将PKG_LEN修改为1024,我们发现综合卡在了第2分25秒的时候,无法再进行下去了。

鉴于上述的规律,我考虑是LUT资源超了,而最可能的原因是reg数组实现大规模存储,vivado可能将其默认成触发器堆栈,严重浪费了LUT/FF资源,按照这个思路我们开始优化:

强制指示综合器用Block RAM,写法如下,使用PKG_LEN为512进行编译,发现跟之前一样,说明没有生效,

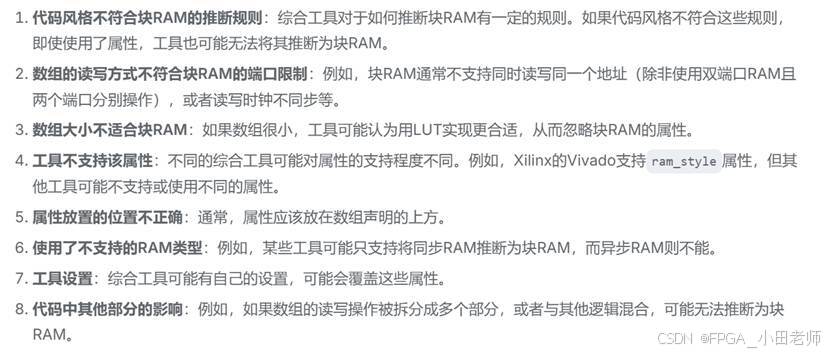

查看没有生效的原因大约如下:

考虑到程序内部设置有复杂的寻址逻辑,所以可能是不符合块RAM的推断规则的,既如此,可以尝试这个数组直接改成一个RAM(例化双口RAM,修改实现逻辑),这样就可以综合为一个Block RAM了。

但是因为我这边资源差的太大了,所以跟领导对接,不在FPGA中做组包的工作了,所以这个问题就到此结束了。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?