目录

3.4 System Init/Test模式 - 系统初始化专家

3.6 High Level Traffic模式 - 协议仿真大师

1 引言

在FPGA系统设计中,验证AXI总线的稳定性和性能至关重要。Xilinx提供的AXI Traffic Generator(AXI流量发生器)IP核正是为此而生的强大工具。本文将深入解析这一IP核的六种工作模式及应用场景。

2 AXI Traffic Generator概述

AXI Traffic Generator(ATG)是一个高度可配置的IP核,能够生成多种类型的AXI事务,用于验证和压力测试基于AXI的系统。它支持AXI4、AXI4-Lite和AXI4-Stream三种接口协议。

3 六种工作模式深度解析

3.1 Advanced模式 - 全功能定制

特点:提供完全控制权,支持所有AXI4特性

-

可编程寄存器:通过控制寄存器精确配置每个事务参数

-

CMDRAM & PARAMRAM:支持复杂事务序列的存储与重复执行

-

地址生成:支持固定、递增、随机地址模式

-

应用场景:复杂AXI协议验证、压力测试

关键寄存器:

-

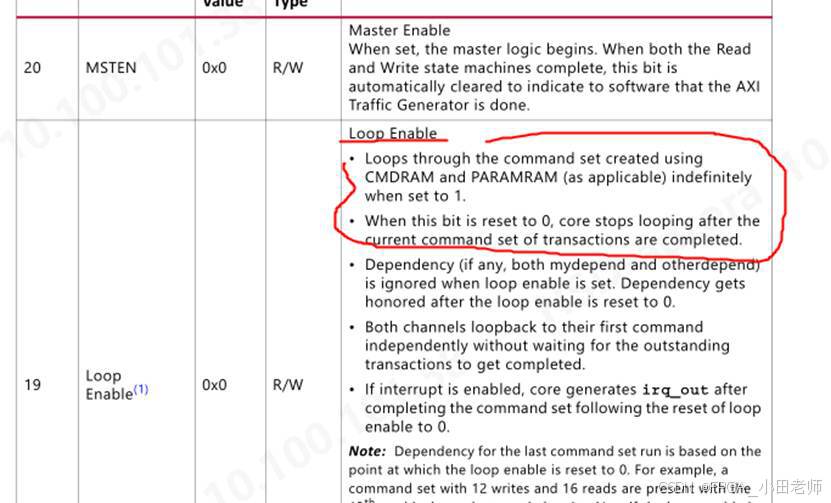

0x00- Master Control:控制主接口使能、循环模式 -

0x04- Slave Control:配置从接口行为 -

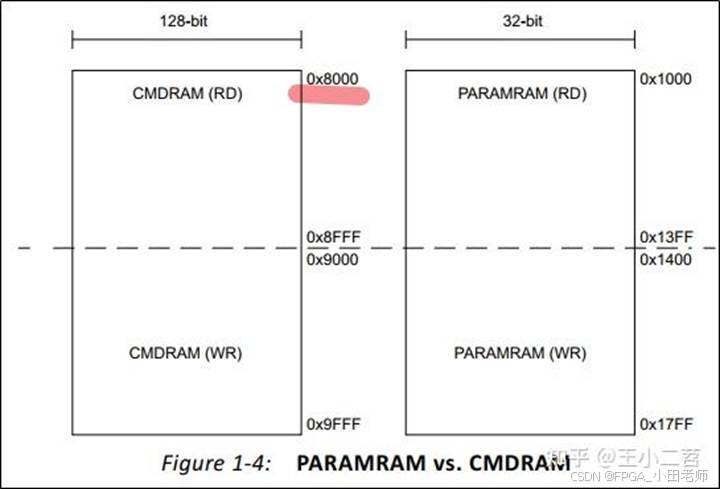

0x8000- Command RAM:存储AXI事务命令

3.2 Advanced模式的相关寄存器说明

Advanced mode允许完全控制流量的产生。提供了控制寄存器对core进行编程并生成不同的axi事务,相关寄存器如下。

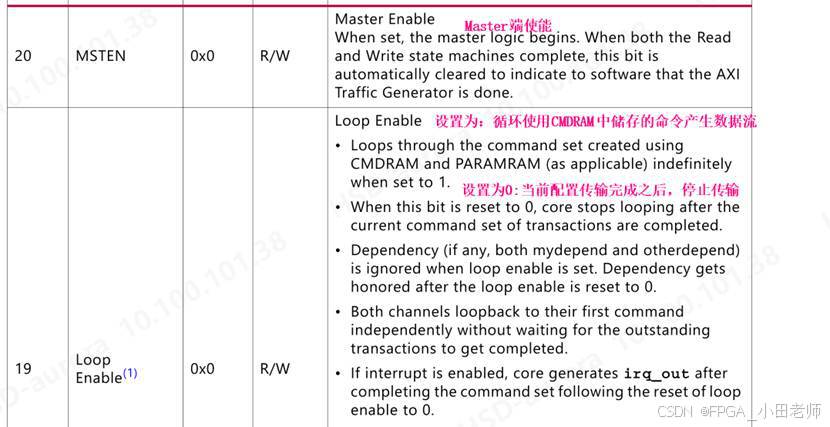

3.2.1 Master Contro(0x00寄存器)

允许用户配置master接口 控制使能ATG

3.2.2 Slave Control(0x04寄存器)

允许用户配置ATG的Slave 接口

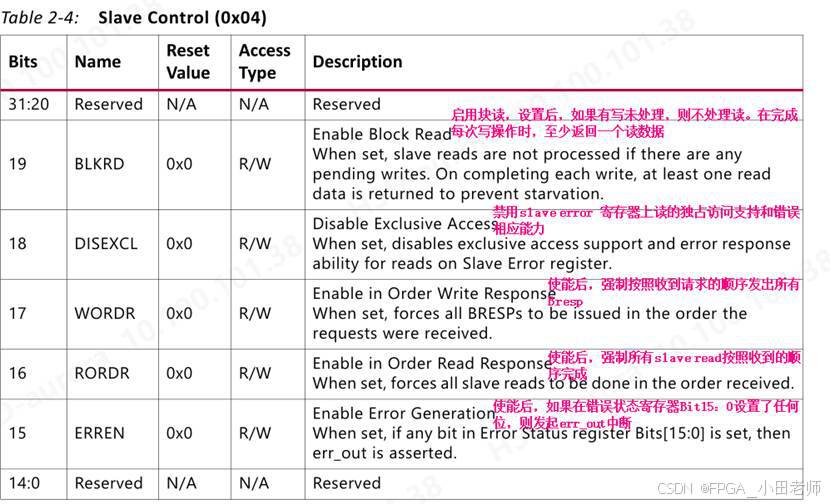

3.3 Advance模式配置界面和关键参数说明

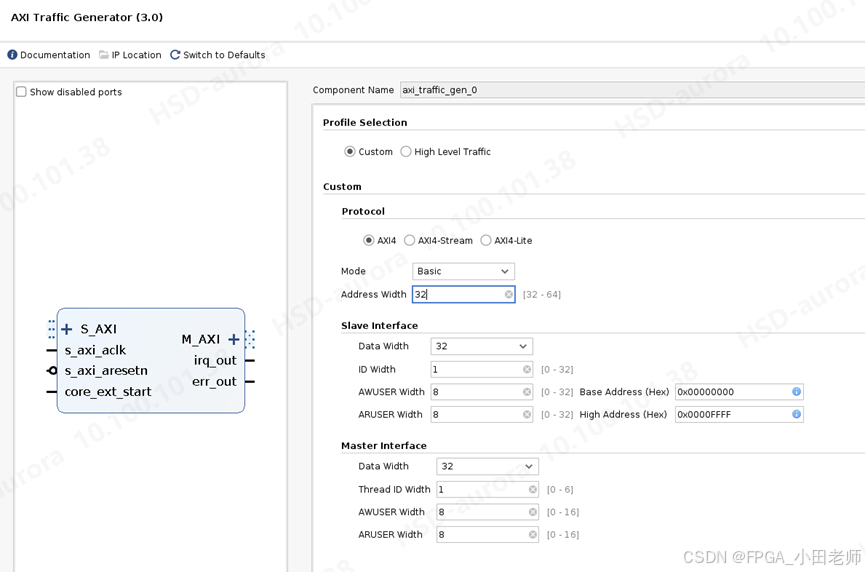

我们打开ip设置如下图所示,这个是默认的设置,我们模式设置为Advanced

其中Repeat Count和 Address Gen seed需要做额外的说明

Repeat count:其实就是CDMRAM中的配置的重复个数,要使用这个Repeat Count,必须配置Master Control为循环使用CMDRAM和PARAMRAM创建的指令集,除此之外,还需要设置PARAMRAM的模式为CMDRAM重复多次,这样才会调用Repeat count的值,如果上面没有进行所述配置,那么Repeat count就不会生效

Address Gen seed:产生随机地址的种子,要使用这个,我们需要配置Addrmode为Random,其才会生效,否则这两个值也不会被使用的,使用的地址就是写入CMDRAM的AXI_Address。

3.4 Advanced模式下的仿真详解

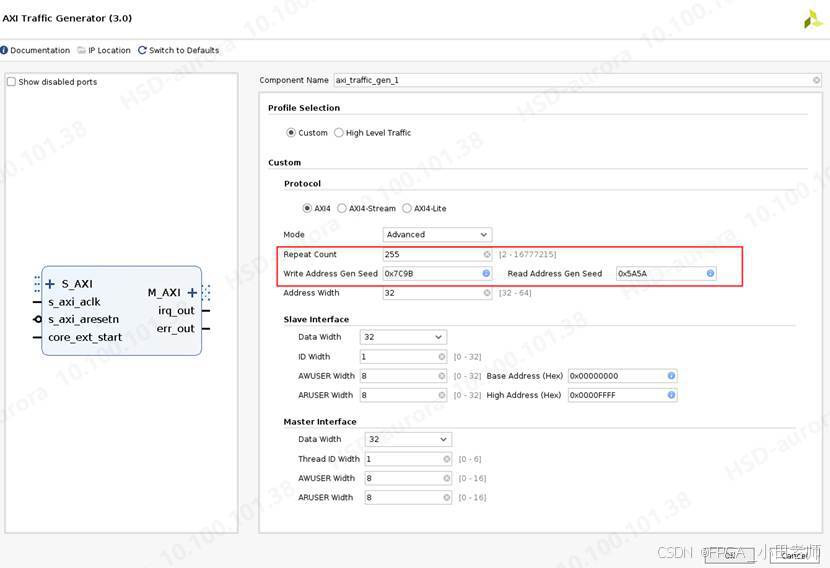

3.4.1 仿真框架说明

下面以xilinx自带的仿真为例进行说明

打开仿真,在scope中看到如下内容:

driver模块:是AXI Traffic Generator IP核的AXI-Lite System Test模式;

DUT模块:是AXI Traffic Generator IP核的Advanced模式;

responder模块:是AXI Bram Ctrl IP核。

其中driver模块使用的是system_test模式,与system_init模式相比,多了一个读的功能

3.4.2 仿真信号详解

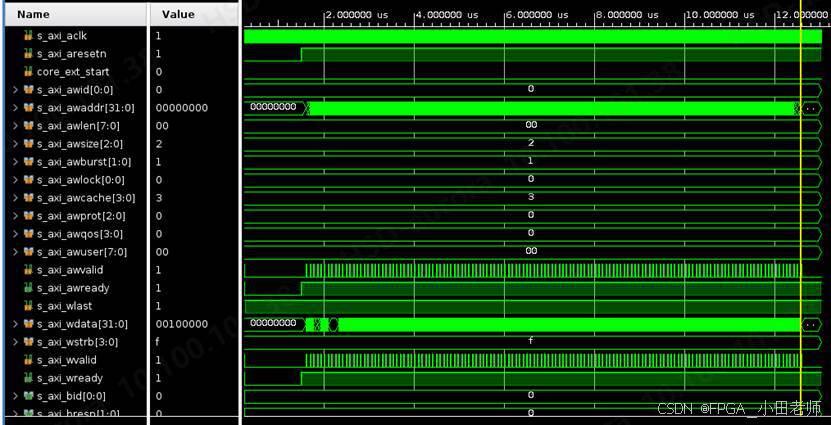

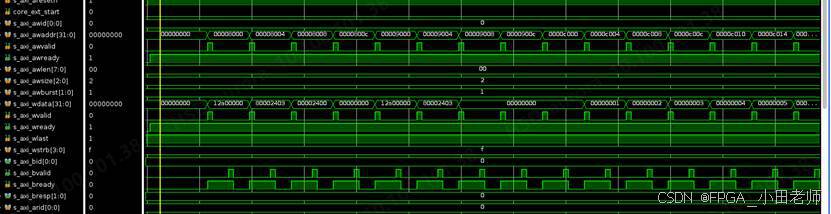

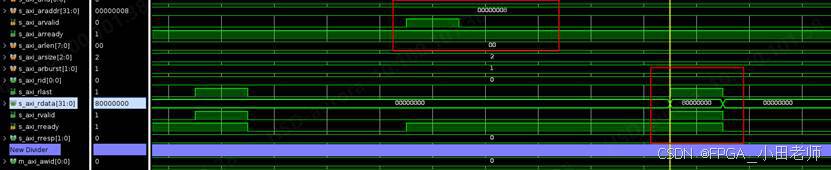

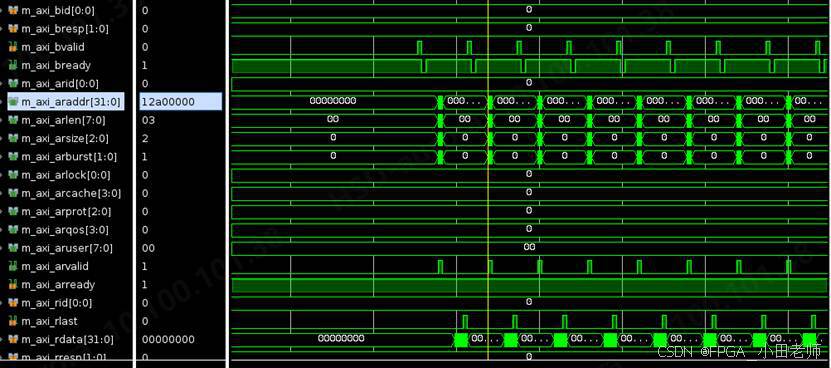

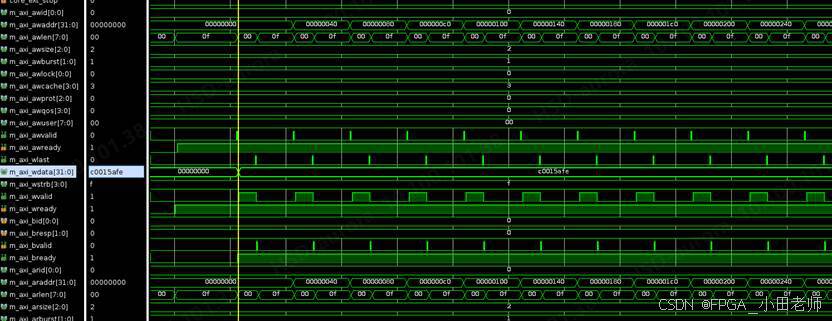

我们添加DUT的信号,可以看出,前面的driver往DUT的Slave端传输了很多的数据

下面我们详细看一下这些地址和数据信号:

第一笔读取了地址0x0000_0000寄存器,值为0x2000_0000,对应的是core的版本信息

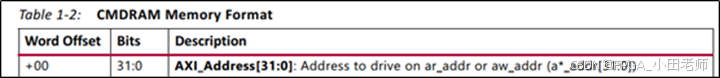

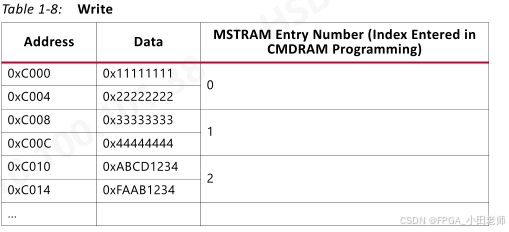

接下来往0x0000_8000写入0x12a0_0000,这个就是给Master端的axi的读地址,地址0x0000_8000是Command RAM的起始地址。0x8000对应的是RD部分的地址

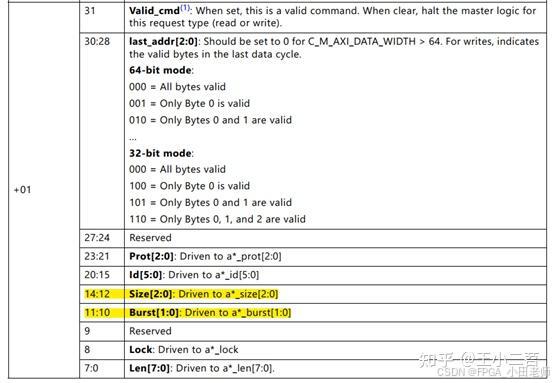

接下来0x0000_8004写入0x8000_2403,是给读的axi的配置,例如size、bust等

31 bit为1,表示该命令有效,14-12值为10(b),表示突发size为2,11-10为01(b),表示突发类型为INCR,7-0为0x03,表示突发length为3。

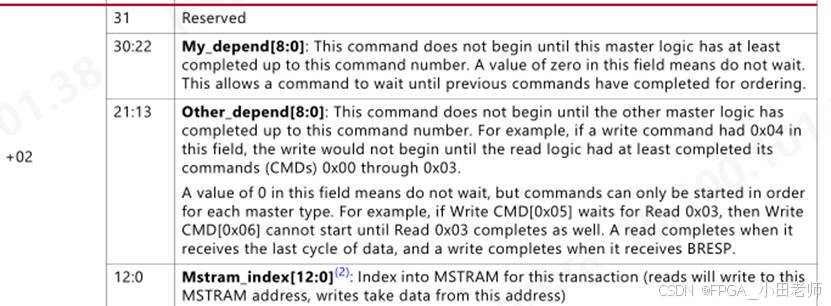

给0x0000_8008写入0x0000_2400

给0x0000_800C写入0x0000_0000

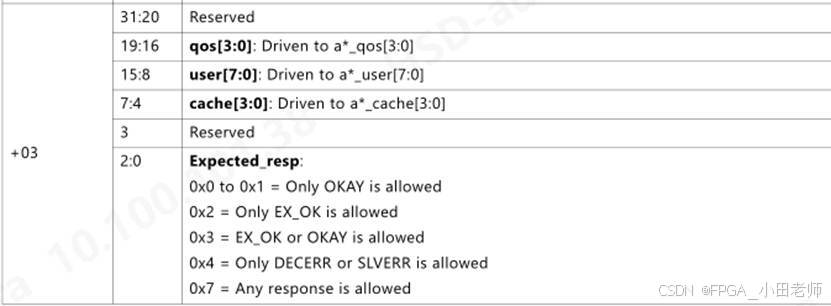

接下来就是0x0000_9000对应的四个寄存器,与上述解释类似,只是它对应的是AXI write的配置

地址0x0000_c000对应为Master RAM起始地址,依次给他写入数据

在数据传输完成之后,读取了0x0000_0008寄存器的值,读取的值为0x8000_0000

表示Master Completion,其意味着Master端事务完成。

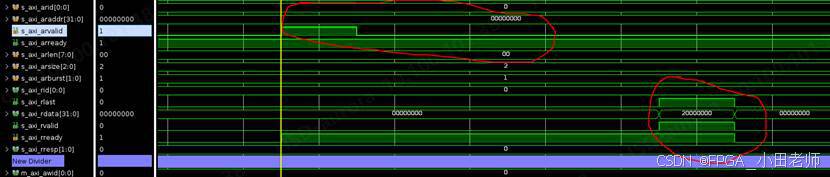

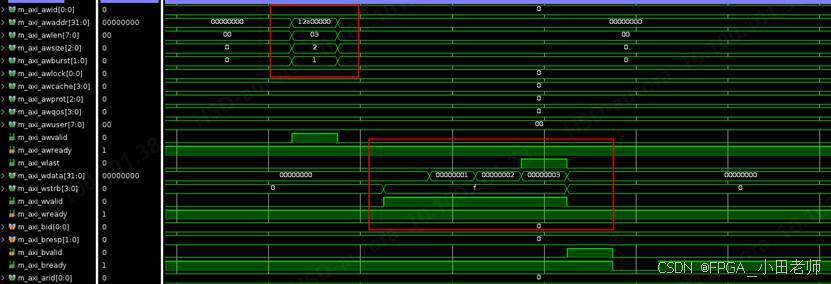

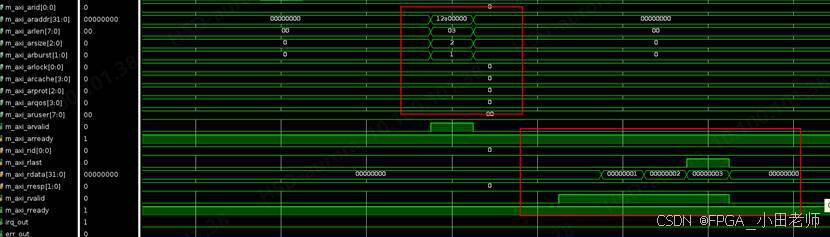

我们在Master端看到的如下,写地址为0x12a0_0000,也就是我们往0x0000_9000配置值,对应的Len为3,即一次burst传输4笔数据,位宽为32bit,传输的数据为0xc000到0xc00c出存储的值,与Driver模块发来的配置一致

读取端,可以看出,读取的与写入的数据一致,

但是为什么Slave端在Master RAM上写入那么多的数据,但是Master端却只传输了一笔burst?

检查配置可以看出,在0x0000_0000寄存器上我们写入了0x0010_0000,也就是说只是使能了 Master Enable,这样的话,值从Command RAM中取一次配置,发起一次传输,如果要发起多次,需要使能Loop Enable

我们对配置进行修改,这个例程的配置是写在coe文件里面的。

会看见Master端发起了多笔burst传输。

我们也可以配置Addrmode,决定传输地址是递增的,还是随机产生的,然后配置PARAMRAM可以决定其重复事务,依据vivado的GUI界面的配置产生,还是依据寄存器的配置产生,这些都是可以的。

3.2 Basic模式 - 轻量级解决方案

特点:Advanced模式的简化版,资源开销更小

-

不支持功能:Narrow传输、非对齐访问、乱序传输

-

无PARAMRAM:无法自动重复事务序列

-

应用场景:基础功能验证、资源受限项目

从配置界面可以看出,与Advance mode相比少了Repeat Count和Address Gen seed,在手册里面也有说,这个模式不支持PARAMRAM的配置,也就是说起无法配置自动重复从CAMRAM中取配置信息,必须自己在0x8000的地址上手动输入,也无法配置地址随机产生,是Advance mode的缩减版.

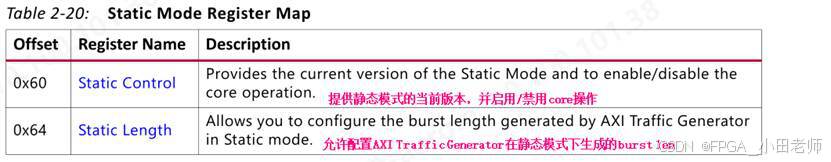

3.3 Static模式 - 极简高效

特点:以最小处理器开销生成简单流量

-

固定模式:持续生成固定数据和长度的INCR类型传输

-

可配置参数:基地址、突发长度(通过

0x64寄存器) -

重要限制:事务不能跨越4K边界

-

应用场景:系统压力测试、互联性能分析

静态模式允许您以更少的资源开销和最少的处理器干预生成简单的axis4流量。在内核使用静态控制寄存器在静态模式下启用后,它不断生成固定数据和固定长度的INCR类型读写传输,并具有可选的地址扫描功能。当地址扫描选项被启用时,IP生成一个在基地址和高地址之间递增的交易。

您可以根据系统配置和从Vivado集成设计环境(IDE)参数传输的长度来配置读写地址。传输长度也可以通过静态长度寄存器配置。读或写通道可以从Vivado IDE参数单独启用。此模式可用于强调互连和系统中的其他模块。突发长度、数据宽度和起始地址的选择应使事务不跨越4K边界。如果不这样做,可能会导致生成的地址出现空白。

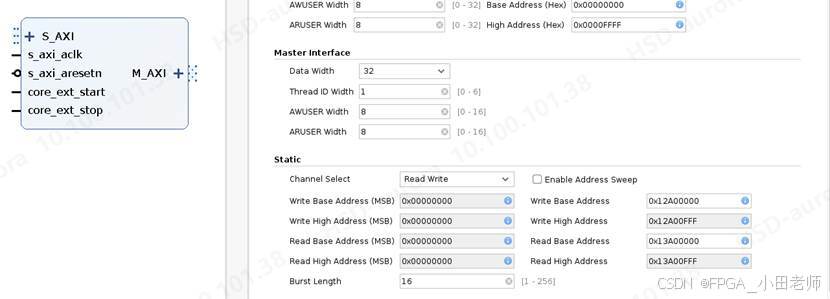

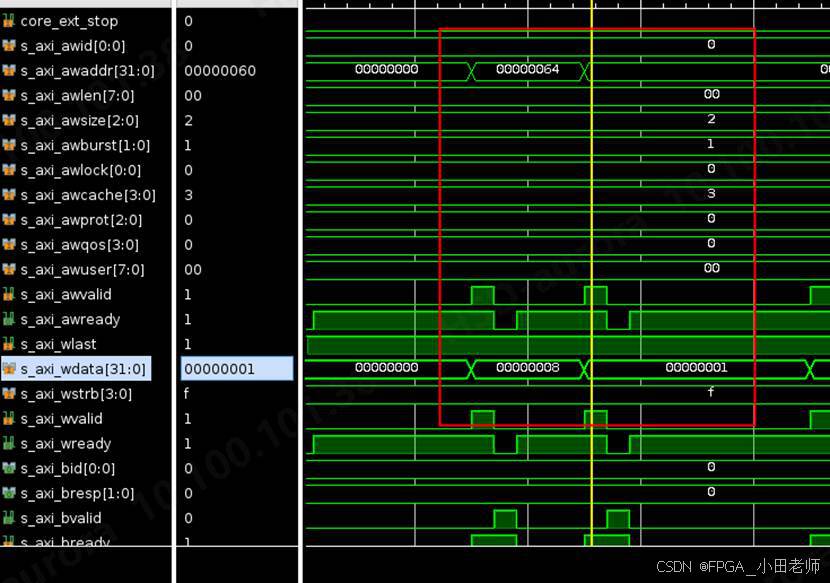

其可配置的寄存器就上述两个,界面如下图,其中写数据的基地址和读数据的基地址是在界面配置好的,Burst Len界面配置是16对应f,可以使用0x64寄存器进行修改,其余均不可修改

例如,在此将0x64配置成8

Mster端写数据的突发长度便从f变成了8

3.4 System Init/Test模式 - 系统初始化专家

特点:专为AXI4-Lite设计,支持系统启动配置

-

System Init:仅支持写操作,用于外设初始化

-

System Test:支持读写操作,用于系统测试

-

COE文件驱动:通过配置文件定义初始化序列

-

应用场景:无处理器系统初始化、外设寄存器配置

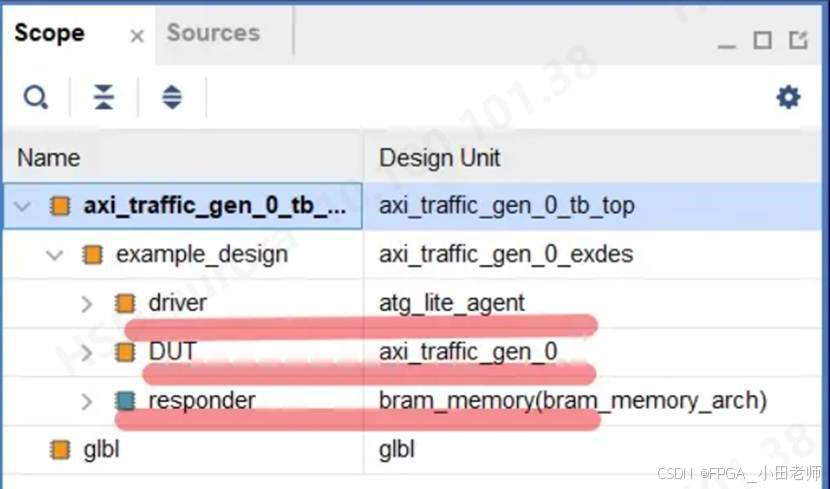

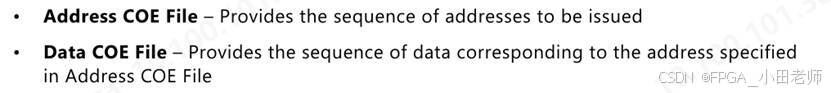

System Init模式是一种特殊模式,core提供了AXI4-Lite Master接口。这种模式可以在没有处理器的系统中使用,在系统重置或简单的系统测试时,用预配置的值初始化系统外设。

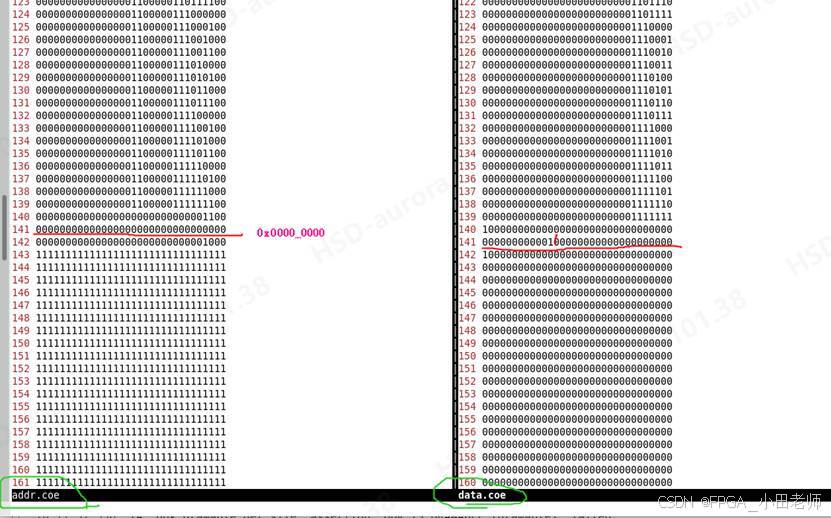

内核在System Init模式下完成重置后,它从ROM中读取系数(COE)文件(地址和数据)并生成axi4 - lite事务。您必须为该模式提供两个COE文件。所有COE文件中的条目都是32位的。

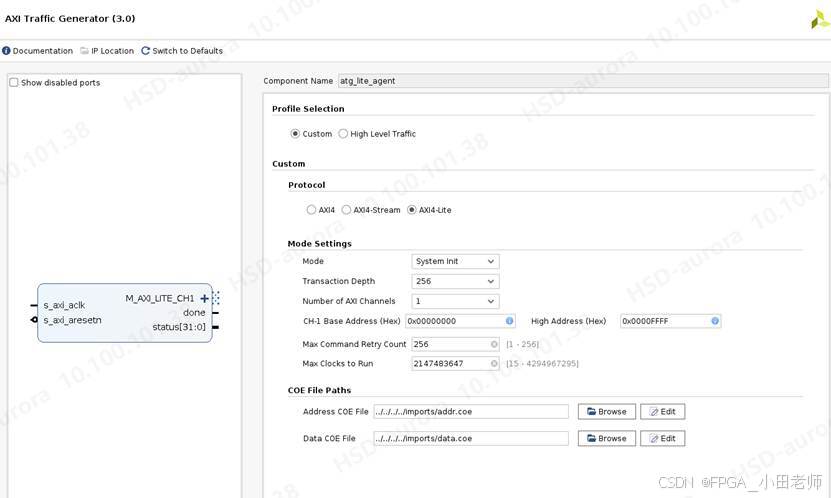

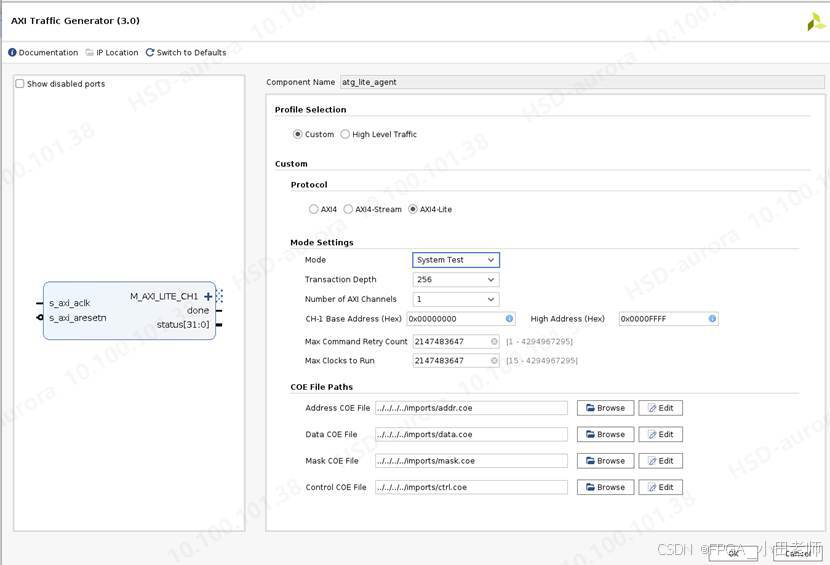

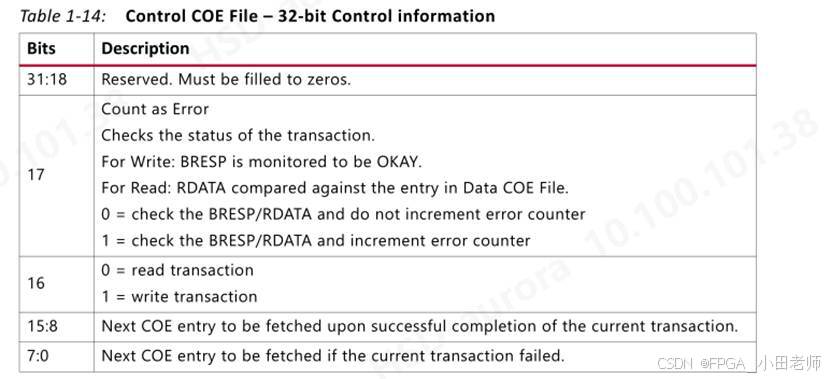

System Init 和Test mode,都是针对于AXI4Lite使用的,配置如下图所示,可以看出,这两种模式的配置都是通过coe文件写入的,但是Test模式比Init模式多了两个coe文件。原因是因为System Init模式只支持写不支持读,所以只需要地址和数据即可,Test模式读写都可以支持,所以除了地址和数据之外,还在ctrl.coe和mask中配置了读还是写模式,

3.5 Streaming模式 - 数据流专家

三种子模式:

-

Master Only:在M_AXIS接口生成可编程流数据,此模式允许您在M_AXIS_MASTER接口上生成具有可编程长度、大小和延迟的原始流数据。

-

Master Loopback:内置生成器和检查器,自动比较收发数据,在这种模式下,core在M_AXIS_MASTER上生成流流量。同样的流量(经过目标IP处理后)在提供给S_AXIS_MASTER接口时,将M_AXIS_MASTER生成的事务与S_AXIS_MASTER接收的事务进行比较。比较时会考虑字段TDATA、TSTRB和TKEEP,并通过axis_err_count端口报告错误计数。

-

Slave Loopback:简单环回功能,带14深度FIFO缓冲,在此模式下,核心通过S_AXIS_SLAVE接口接收流流量,并通过M_AXIS_SLAVE回送相同的流量。核心使用深度为14的内部FIFO来允许对M_AXIS_SLAVE进行节流,同时仍然接受数据S_AXIS_SLAVE接口

-

应用场景:AXI-Stream接口验证、数据通路测试

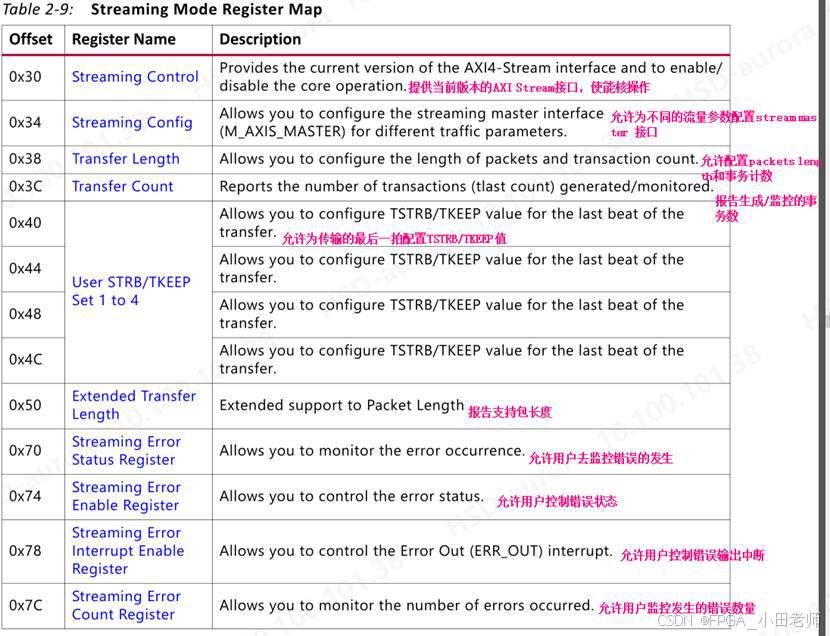

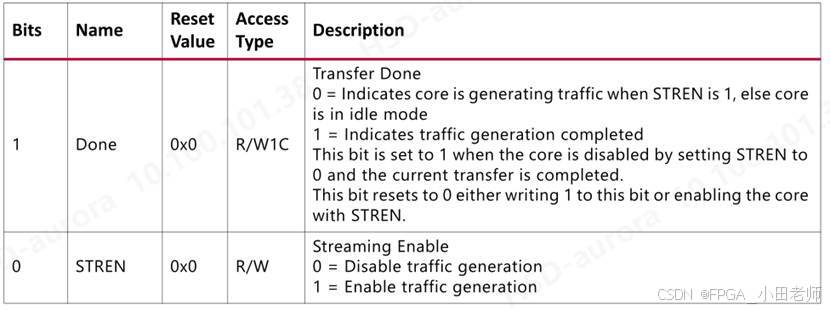

相关寄存器如下:

Streaming Control

3.6 High Level Traffic模式 - 协议仿真大师

特点:模拟真实IP的吞吐量特性,支持五种预定义协议

支持的协议配置文件:

-

Video模式:模拟视频IP,可配置分辨率、像素深度

-

PCIe模式:模拟PCIe IP,配置通道数、速率、负载

-

Ethernet模式:模拟以太网IP,配置速度、负载类型

-

USB模式:模拟USB IP,支持ISOC或BULK模式

-

Data模式:通用模式,用户自定义长度和间隔约束

重要提示:

-

这些模式不生成实际协议数据包,只模拟AXI端吞吐量特性

-

突发长度需足够大才能达到目标吞吐量

-

启用地址扫描(Address Sweep)可生成递增地址

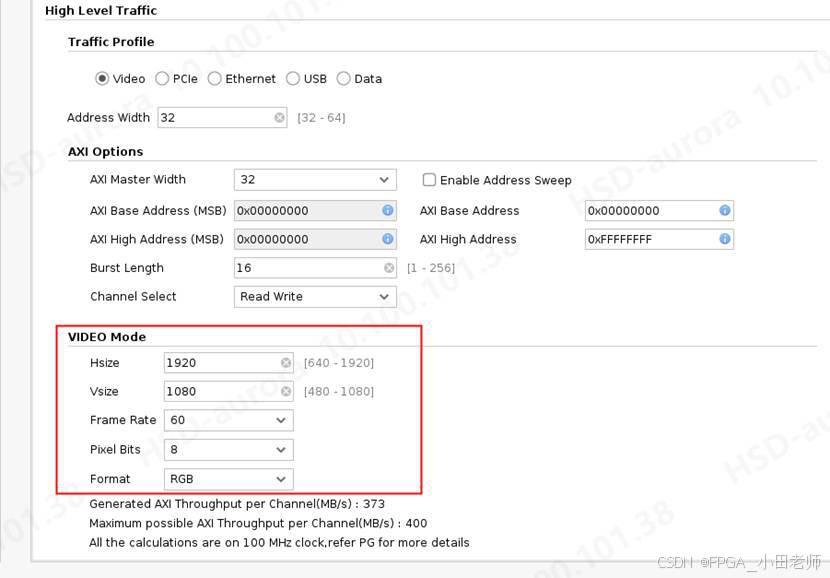

3.6.1 Video模式

这个选择可以用来模拟视频IP,它处理视频信息并产生AXI流量。不同的可用选项包括HSize、Vsize、像素位等

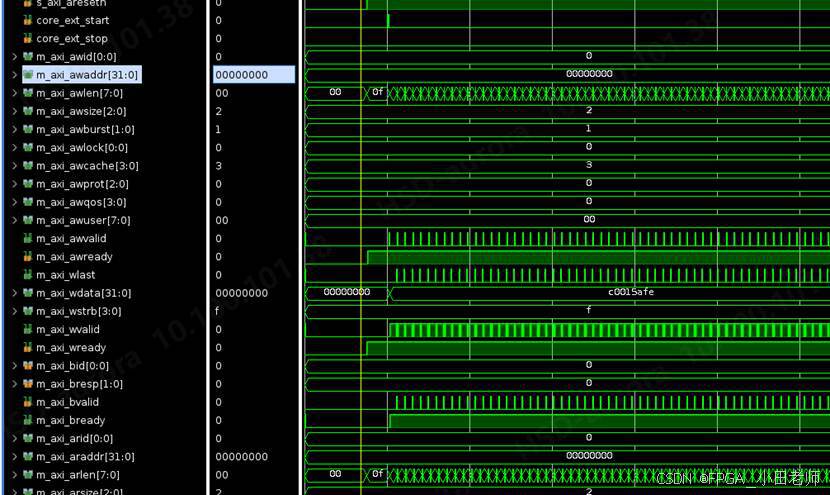

产生的数据:读写地址固定为0x0000_0000,读写数据亦为固定数0xc001_5afe,单纯只是为了产生AXI端的吞吐率

可以在仿真中加入apm去统计读写事务,延迟以及吞吐量。

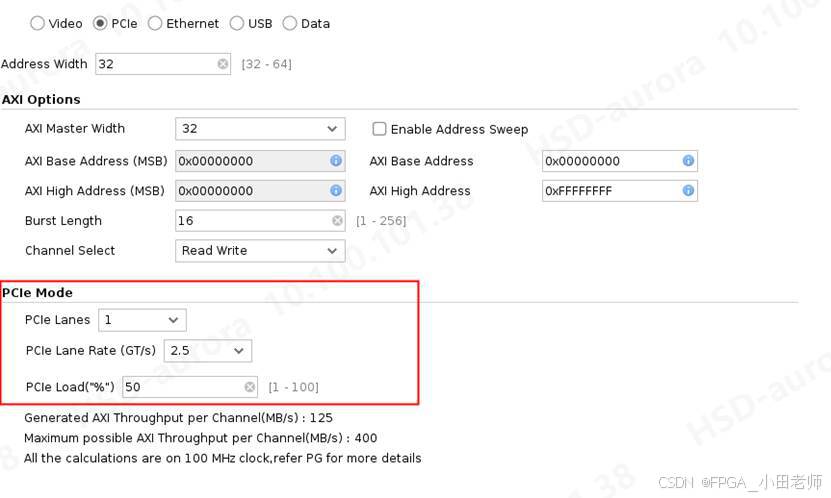

3.6.2 PCIe模式

这个选择模拟PCIe IP,它处理PCIe数据包并产生AXI流量。不同的可用选项包括PCIe通道,通道速率等。PCIe加载选项可用于在总线上生成与PCIe相关选项相结合的部分负载。

注意上述的Enable Address Sweep需要勾选,如果不勾选的话,读写的地址将一直都是0x0000_0000

勾选之后,就会生成递增的地址,但是数据一直都是固定数

其外部接有apm,通过配置apm,便可以对吞吐量进行统计。

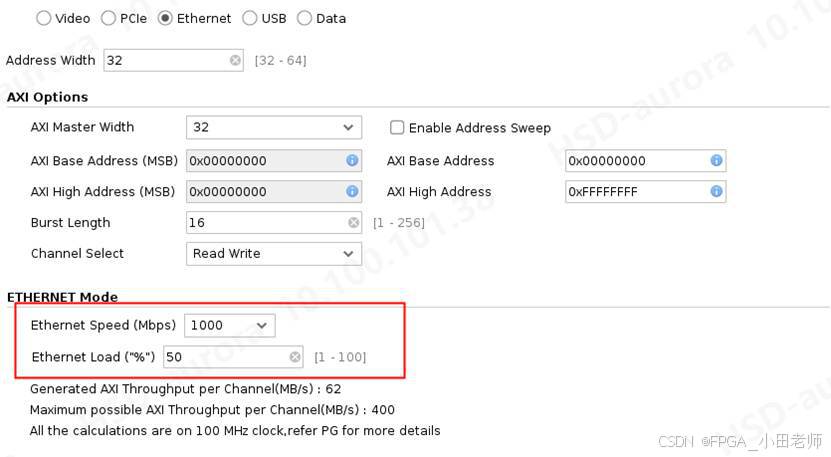

3.6.3 Ethernet模式

这个选择模拟以太网IP,它处理以太网数据包并生成AXI流量。不同的可用选项包括以太网速度和以太网负载。负载选项可用于在总线上生成与以太网相关选项相结合的部分负载。

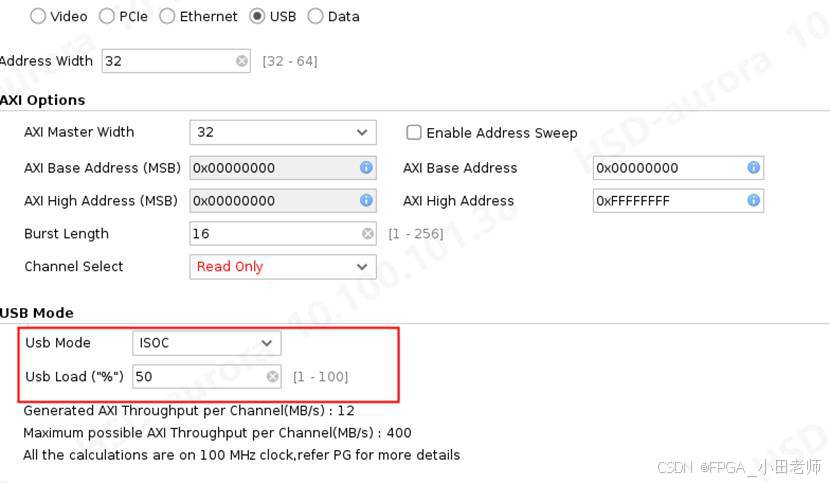

3.6.4 USB模式

这个选择模仿USB IP,它处理USB数据包并产生AXI流量。可用的选项包括USB模式,可以是ISOC或BULK。加载选项可用于在总线上生成与USB相关选项相结合的部分负载。

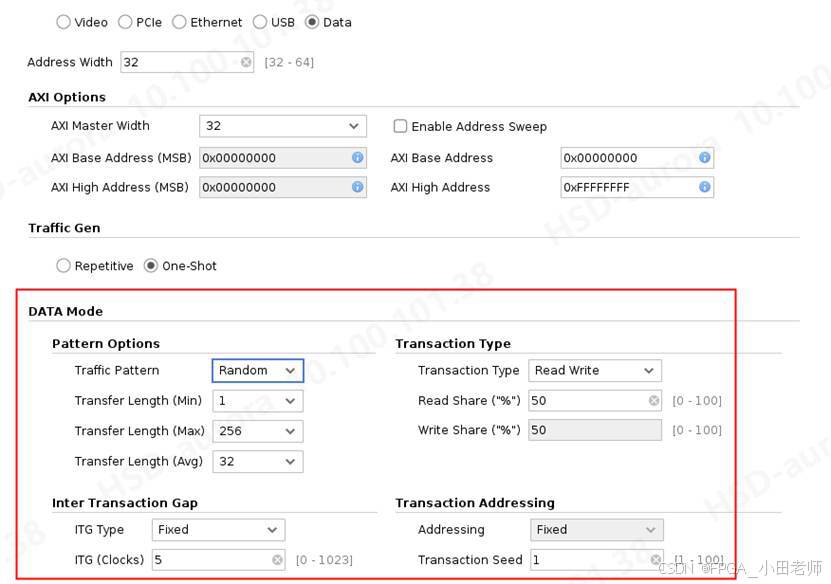

3.6.5 通用Data模式

这是一种通用模式,可用于在上述选项之一不符合要求时生成用户预期流量。可用的选项包括读通道/写通道共享、最小、最大、对生成的事务长度的平均约束等。

4 实战应用技巧

性能监控

-

集成AXI Performance Monitor(APM)IP核

-

实时统计读写吞吐量、延迟、事务计数

-

分析系统瓶颈,优化架构设计

自动化测试

-

通过COE文件预定义测试序列

-

结合Vivado Tcl脚本实现自动化验证

-

批量执行多种流量模式,全面覆盖测试场景

5 模式选择指南

| 模式 | 接口类型 | 资源开销 | 适用场景 |

|---|---|---|---|

| Advanced | AXI4 | 高 | 复杂协议验证、全面测试 |

| Basic | AXI4 | 中 | 基础功能验证、快速原型 |

| Static | AXI4 | 低 | 压力测试、性能分析 |

| System Init/Test | AXI4-Lite | 低 | 系统初始化、寄存器测试 |

| Streaming | AXI4-Stream | 中 | 数据流验证、环回测试 |

| High Level Traffic | AXI4 | 高 | 系统级性能验证、IP仿真 |

6 总结

Xilinx AXI Traffic Generator IP核是FPGA系统验证的瑞士军刀,其六大工作模式覆盖了从简单寄存器访问到复杂系统级性能测试的全场景需求:

-

灵活性:从极简Static到全功能Advanced,满足不同复杂度需求

-

实用性:预定义的High Level Traffic模式大幅减少测试搭建时间

-

可靠性:内置错误检测和统计功能,确保测试结果准确可信

无论是验证单个IP核的AXI接口,还是测试整个系统的吞吐量性能,AXI Traffic Generator都能提供专业级的解决方案。掌握这一工具的使用,将显著提升FPGA系统开发的效率和质量保证水平。

1302

1302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?