目录

为什么使用 ila ?

1.ila可以直接在 FPGA 或 ASIC 硬件上运行,在 ila 查看到的数据是硬件真实的情况

2.ila可以在线调试,不需要额外添加逻辑分析仪

怎么使用 ila ?

1.使用 IP 核创建 ila 调试环境

1.1搭建环境

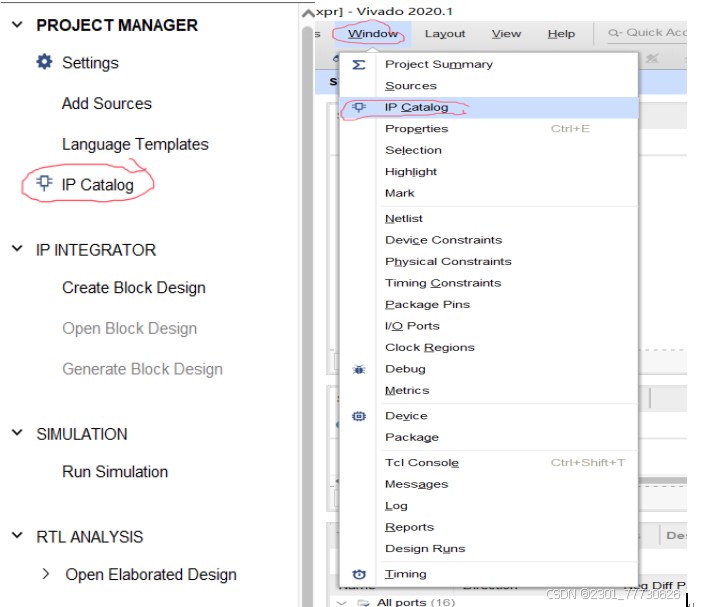

通过这两个地方都可以找到IP核的设置

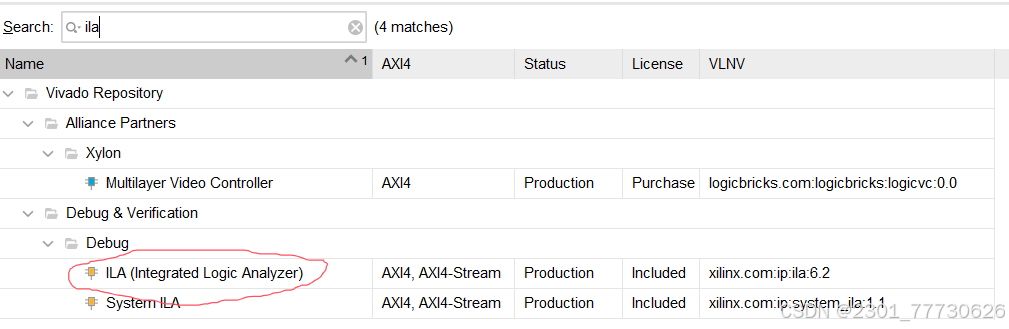

在 ip 查找 ila ,点击第一个 ila 使用,第二个 system ila 具有更高级的调试功能,但是需要在 block design 才可以使用

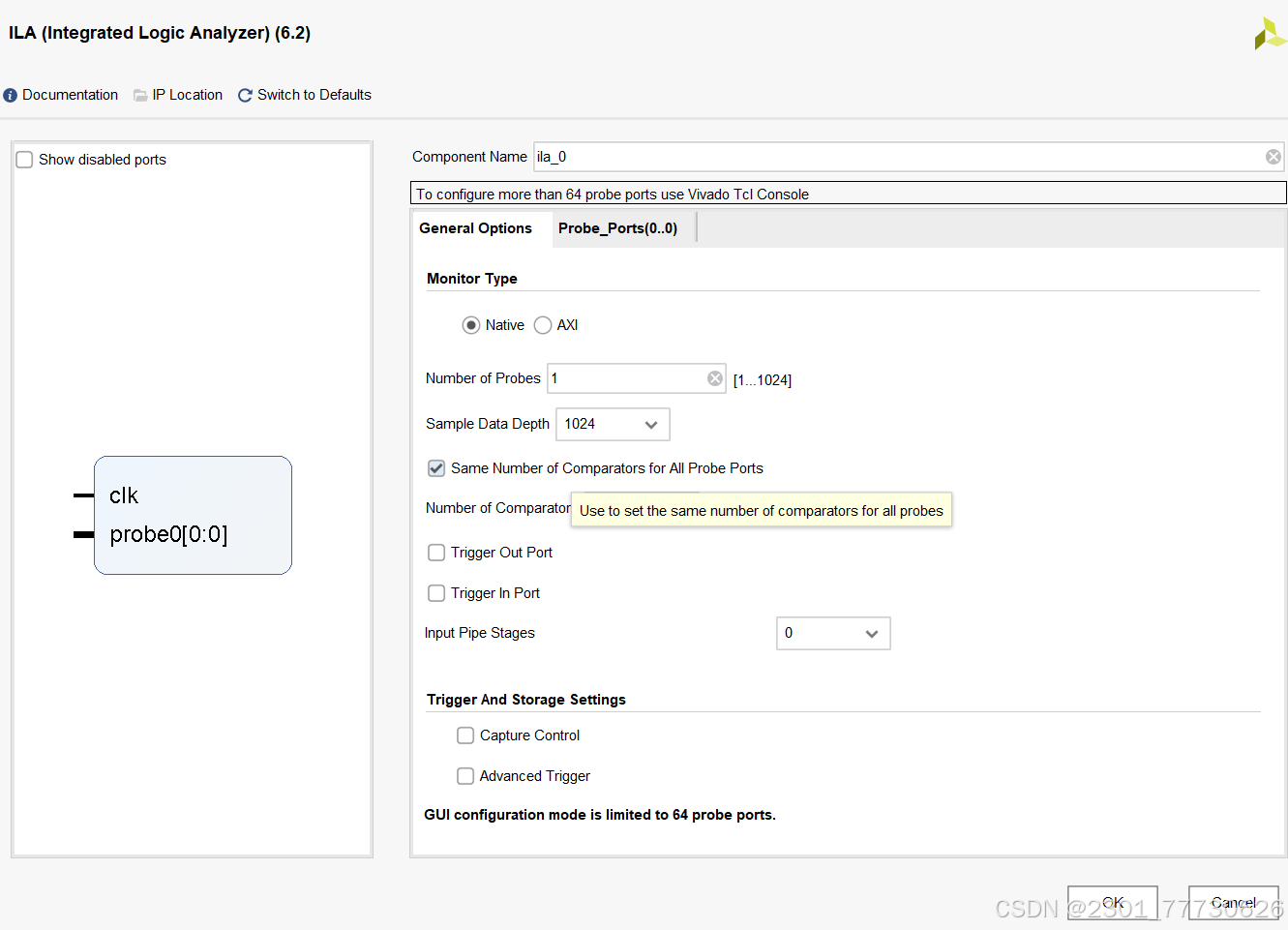

Documentation 相当于辅助文件夹

第一个的Product Guide 是 IP 手册查看入口,点击可自动跳转到 Xilinx 官方文档 DocNav 软件的这个 IP 手册的界面。

第二个的Change Log 是 IP 版本更新记录,点击可以看到如图 1.2-7 所示的 ILA IP 更新记录。

第三个的Product Webpage 是 IP 相关介绍的网页版,点击可跳转到如下图所示的 Xilinx 官方有关这个 IP 介绍的网站。

第四个的Answer Records 是Xilinx 官方网站,同时可以在里面问问题。

IP Location 设置 IP 的存放路径入口,点击出现如下图所示窗口,在窗口 里可以通过点击“…”设置更换存放路径,默认是存放在工程路径下的.....<工程名>.srcs\ sources_1\ ip.

Switch to Default 点击后所有的设置恢复到默认值。

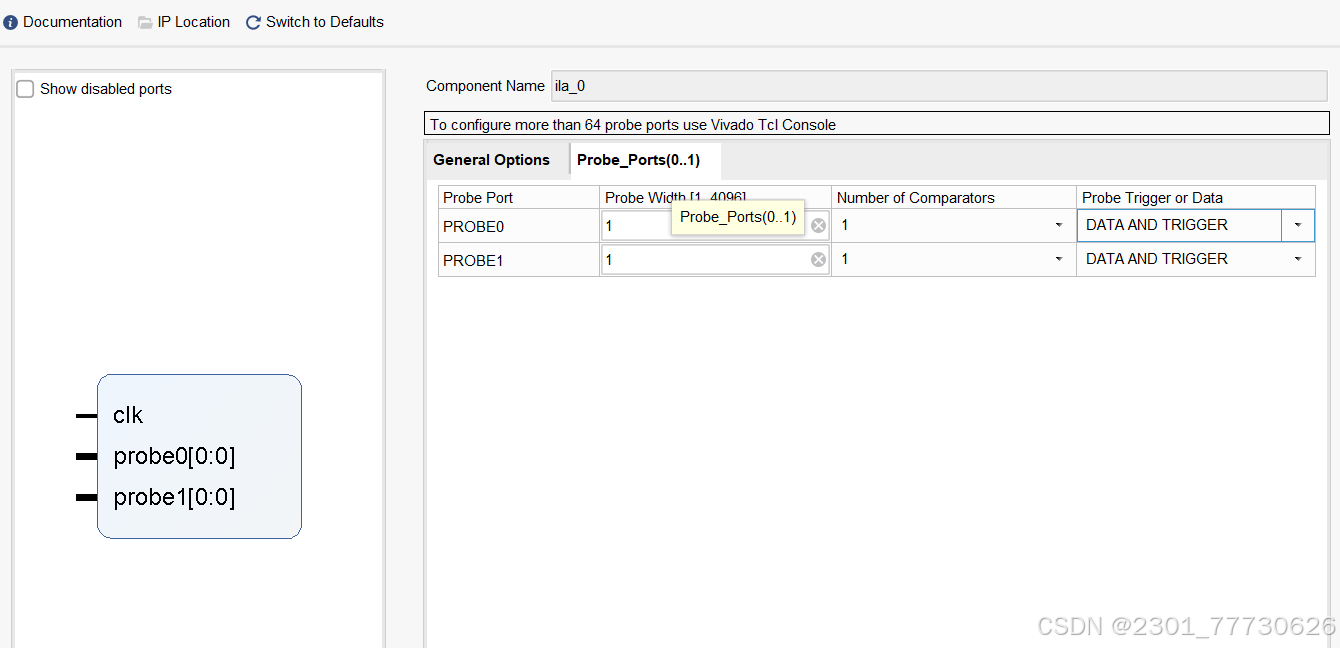

Component Name 设置生成 IP Core 的名称,这里可以自己设置名字。

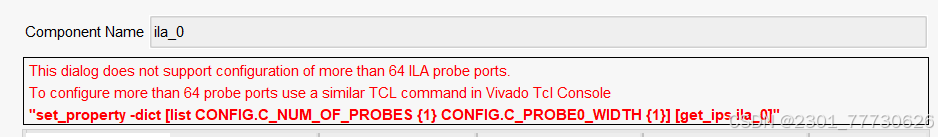

To configure more than 64 probe ports use Vivado Tcl Console 表示通过该界面设置最多可设置 64 个探针,如果想设置 更多的探针需要使用 Tcl 脚本命令去设置

ila 探针接口类型设置有两个,Native和AXI

Native 常规普通接口模式,用于一般代码

AXI AXI 接口模式,用于调试 AXI 接口信号

Number of Probes 设置探针数量设置,如果超过64个,会报错

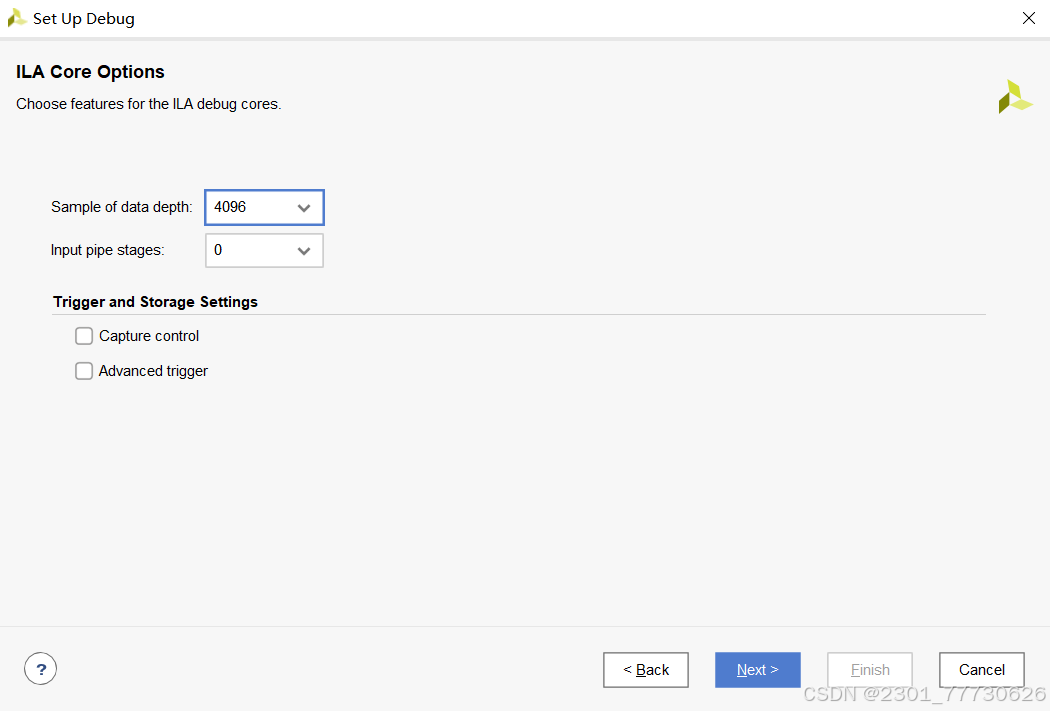

Sample Data Depth:采样数据深度,设置的数值越大,采样的数据越多,看

到的波形数据越多,但是最终占用的资源也会越多

Same Number of Comparators for All Probe Ports设置相同探针接口的 Comparators 的个数,不勾选,下面的 Number of Comparators 就会消失。默认勾选,后面的参数也保持默认。

Trigger Out Port 触发输出端口,可用于 ILA 模块的级联或一些高级功能,具体使用参考 IP 手册,这里保持默认不勾选。

Trigger In Port 触发输入端口,可用于手工设置添加触发信号或进行 ila 模块的级联或一些高级功能,具体使用参考 IP 手册,这里保持默认不勾选。

Input Pipe Stages 设置待探测信号打拍次数,如下图所示,可设置数值 0~6,一般情况下,采样时钟和探测信号是一个时钟域下,一般默认设置为 0 即可

Capture Control 这里勾选后可在调试查看波形窗口进行对 Capture mode 的设置

Advanced Trigger 这里勾选后可在调试查看波形窗口进行对 Trigger mode 的设置

Show disabled ports 在 IP 核的模拟示意图中展示出未使用信号引脚。

Probe Width:探针数据信号的位宽设置

Probe Trigger or Data:对探针设置触发器或数据,分3钟:

(1)DATAAND TRIGGER:既是数据又可作为触发条件;

(2)DATA:仅作为数据,不可作为触发条件;

(3)TRIGGER:仅可作为触发条件;

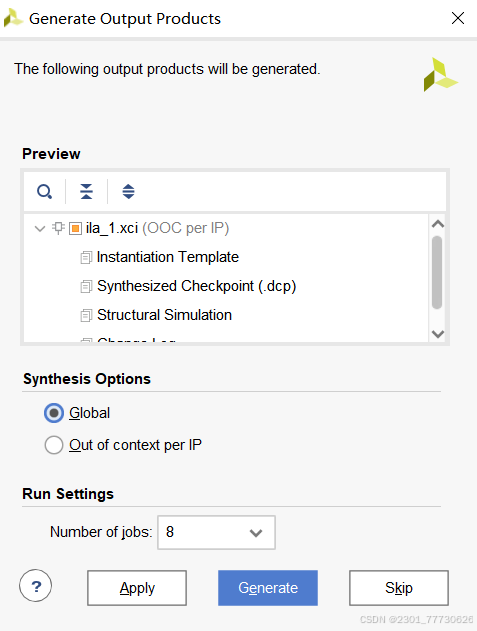

创建IP核

完成创建

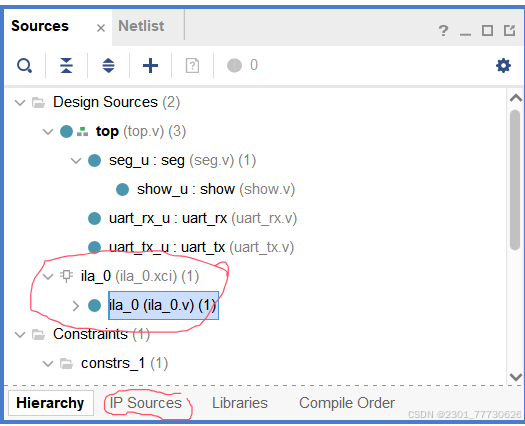

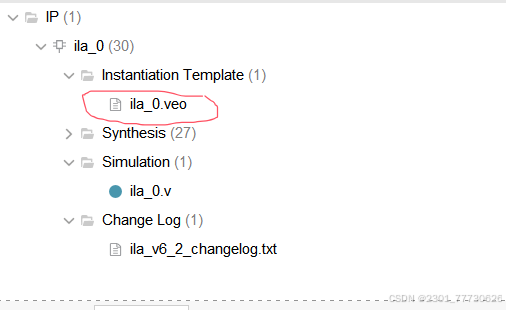

说明ila的IP核存在在工程里,点击IP Source,打开IP工程文件

在IP工程文件找到.veo文件

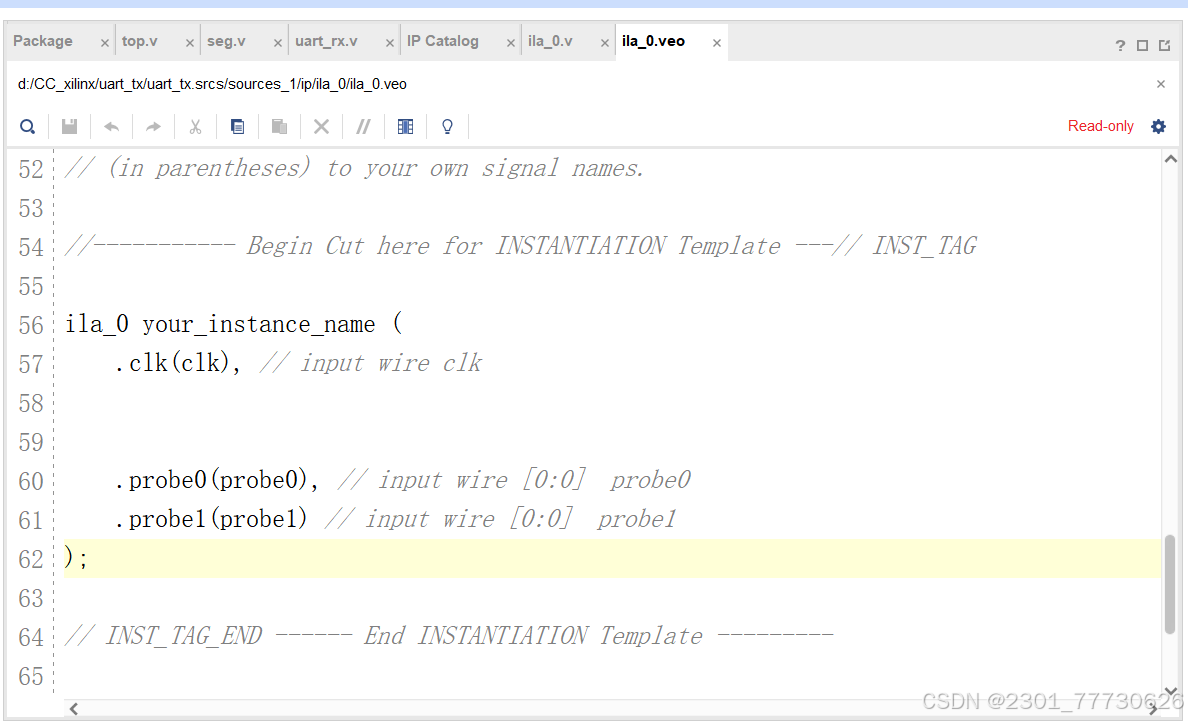

这是例化代码中提供了时钟端口和刚刚配置完成的两组探针端口。同时在注释中提示了生成 IP 核时给出的位宽配置(自己设置的Probe Width),并且该文件无法自己修改。(如果要改只能重新将IP核生成)

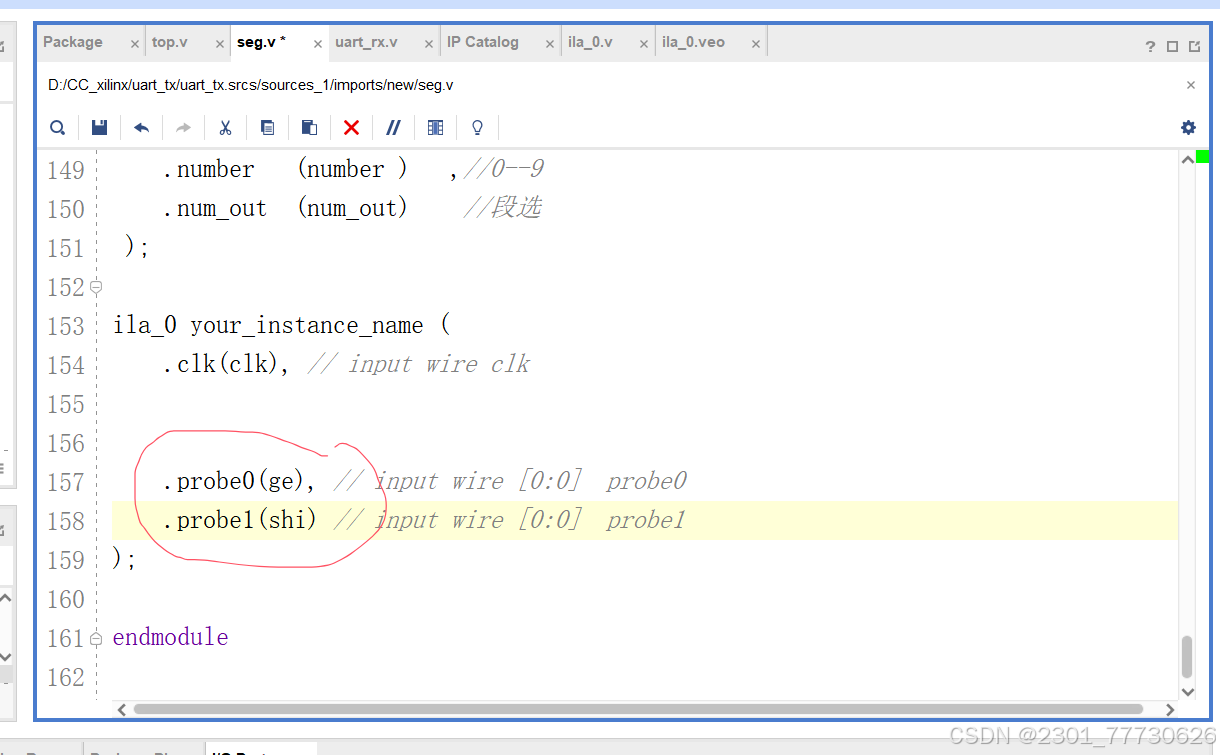

把需要测试的信号放在探针里,这里要保证探针和测试的信号的位宽一样,例如ge的位宽为4,设置的Probe Width也应该为4.

2.使用 Debug 标记创建 ila 调试环境

2.1搭建环境

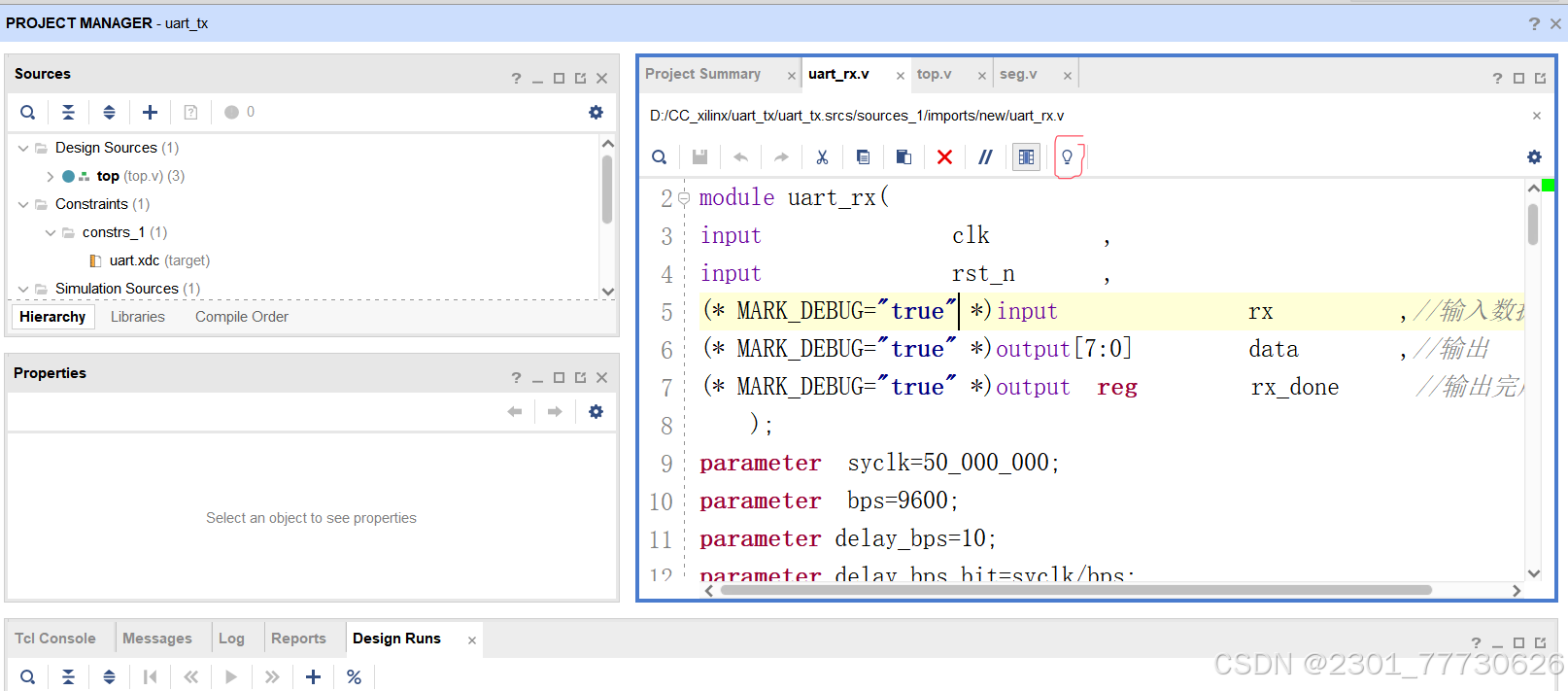

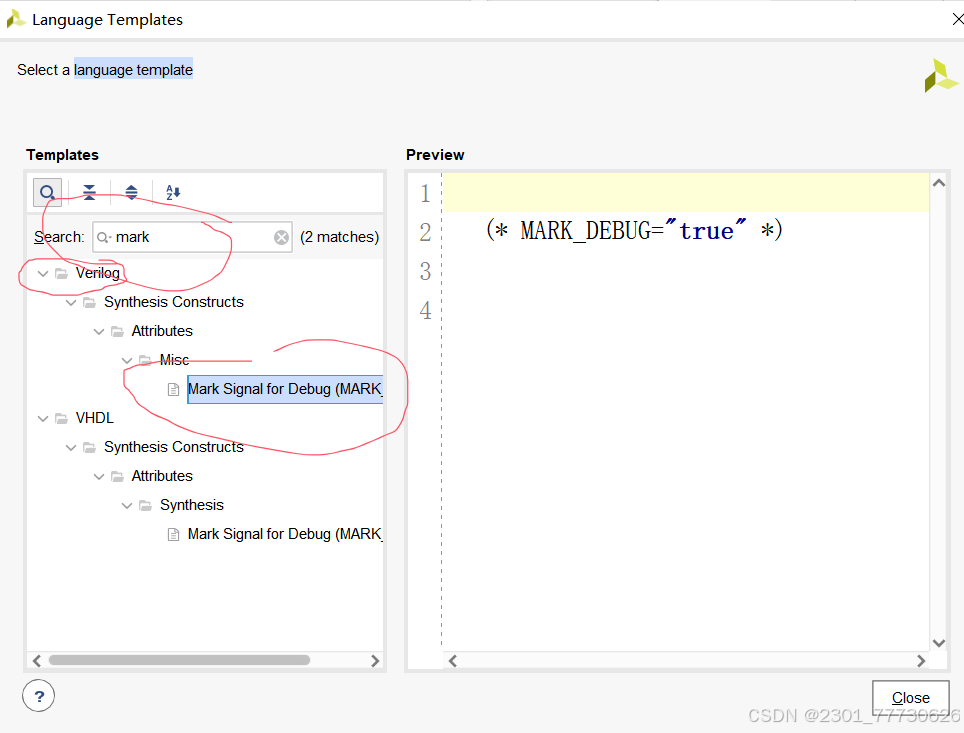

点击红圈的language template

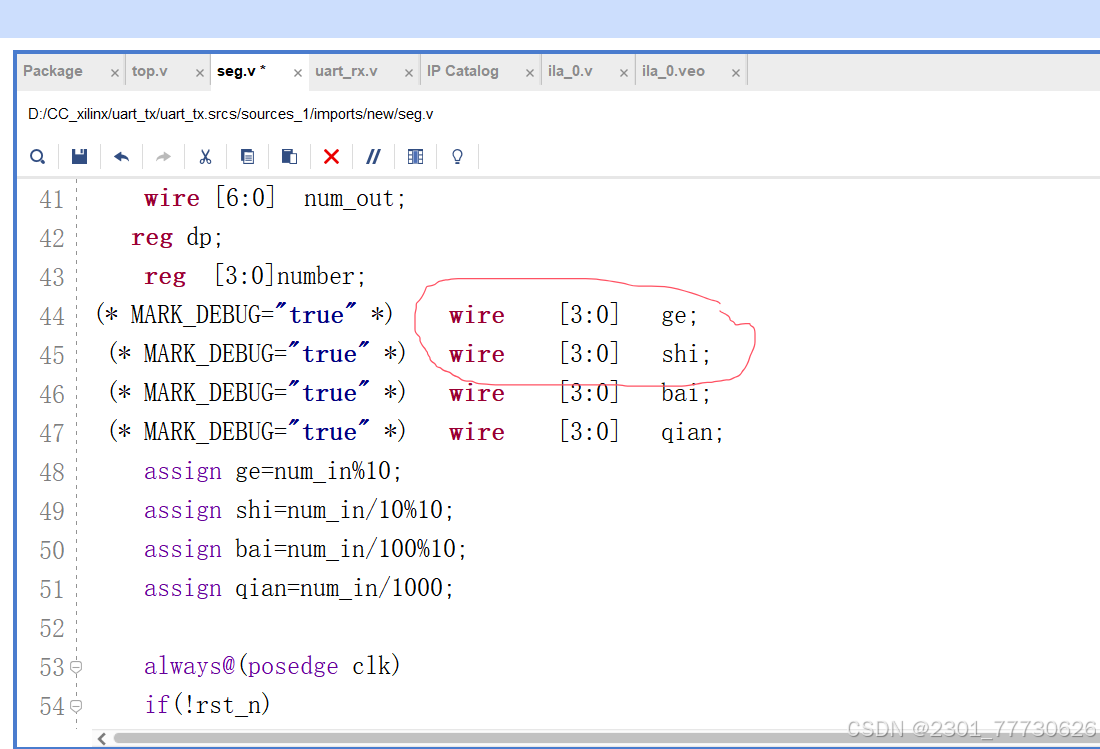

查找mark,选择verilog的语句,将其复制待用

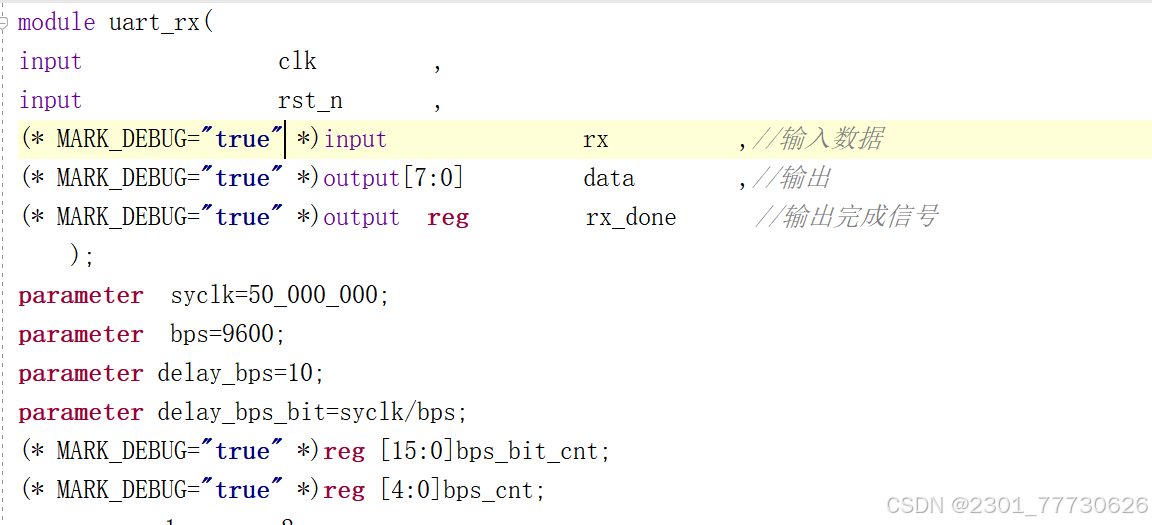

将这个语句放置在需要检测的信号前面

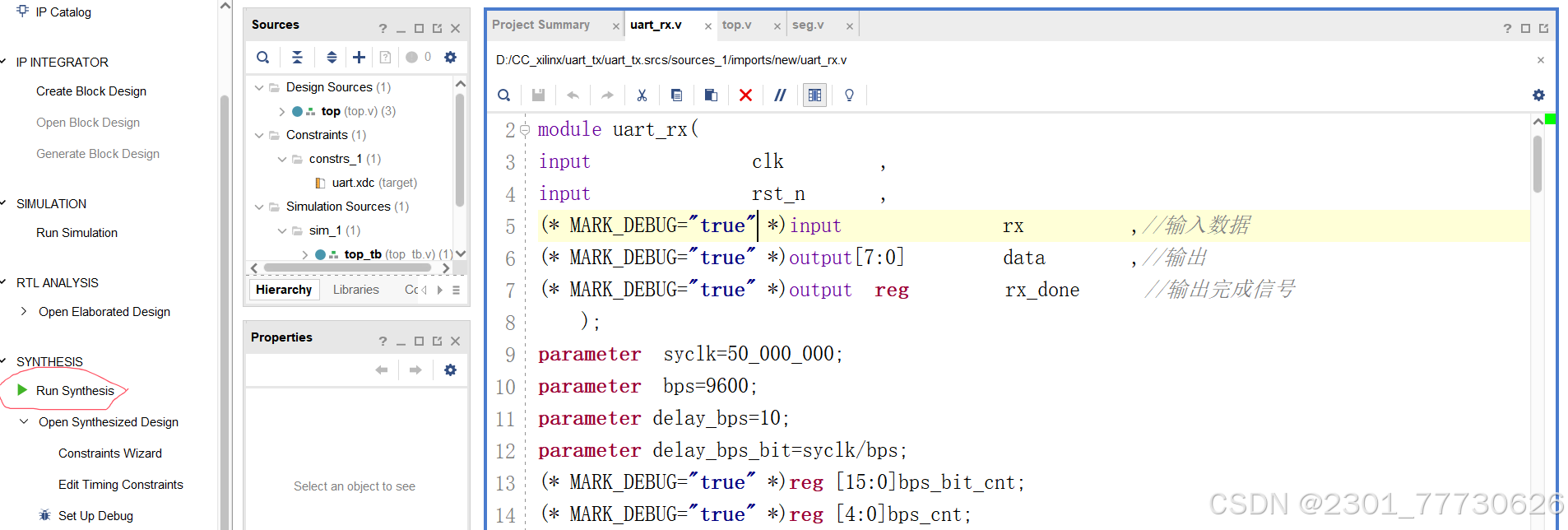

放置完成后保存,进行综合

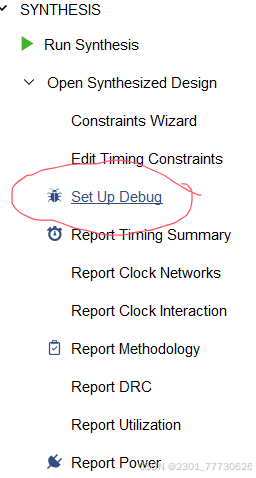

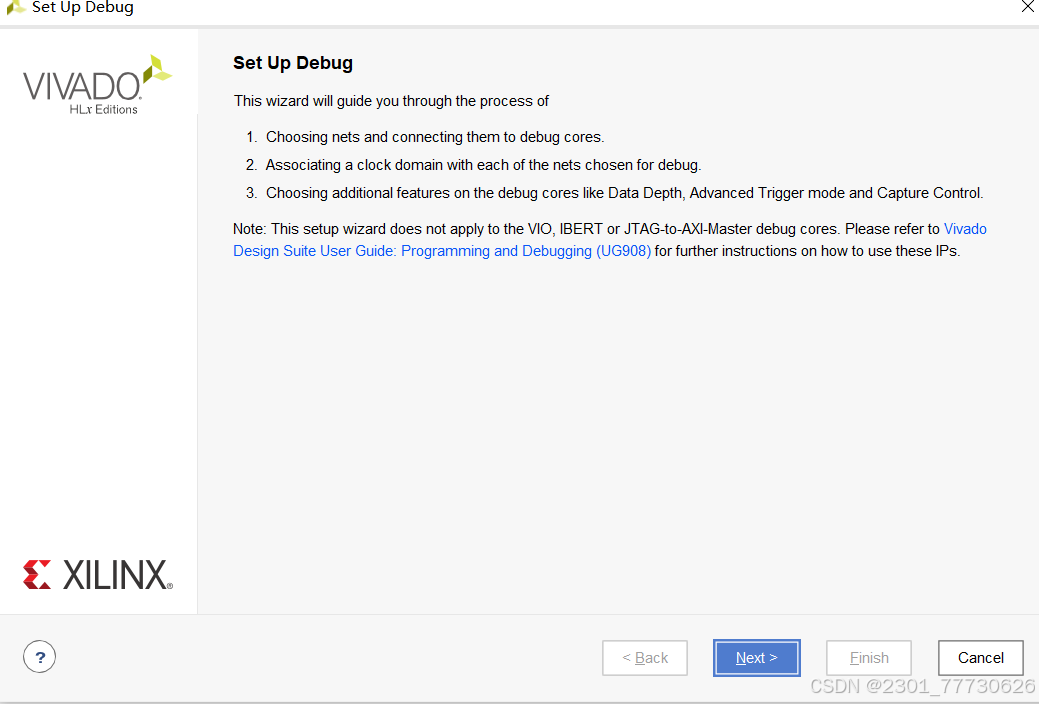

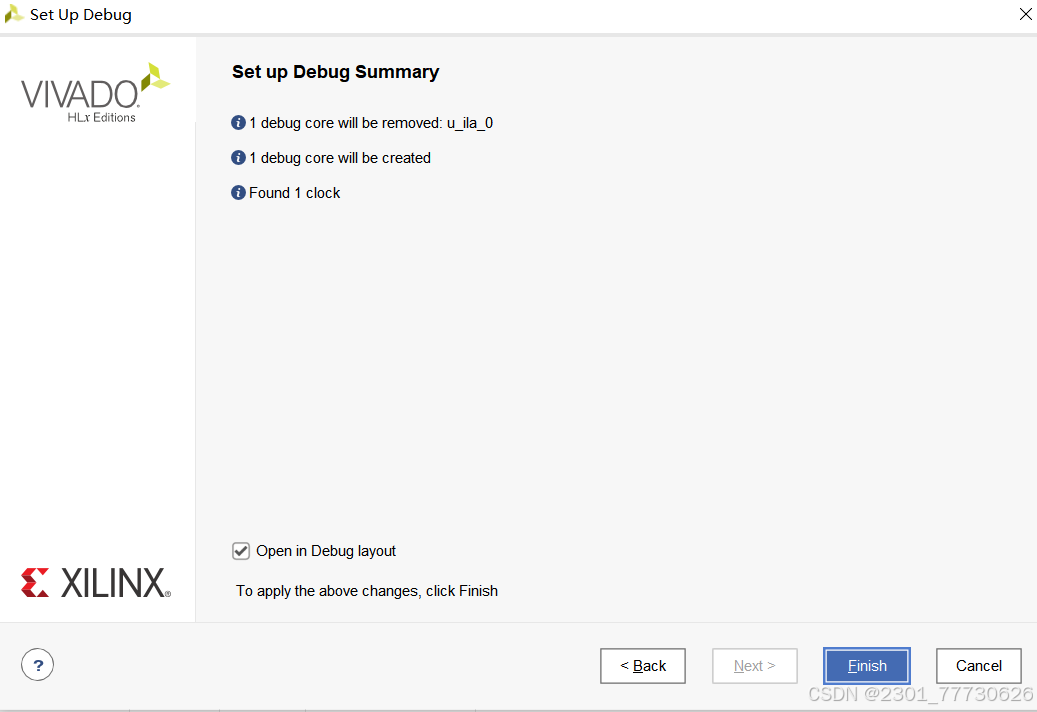

完成综合后,点击Set Up Debug

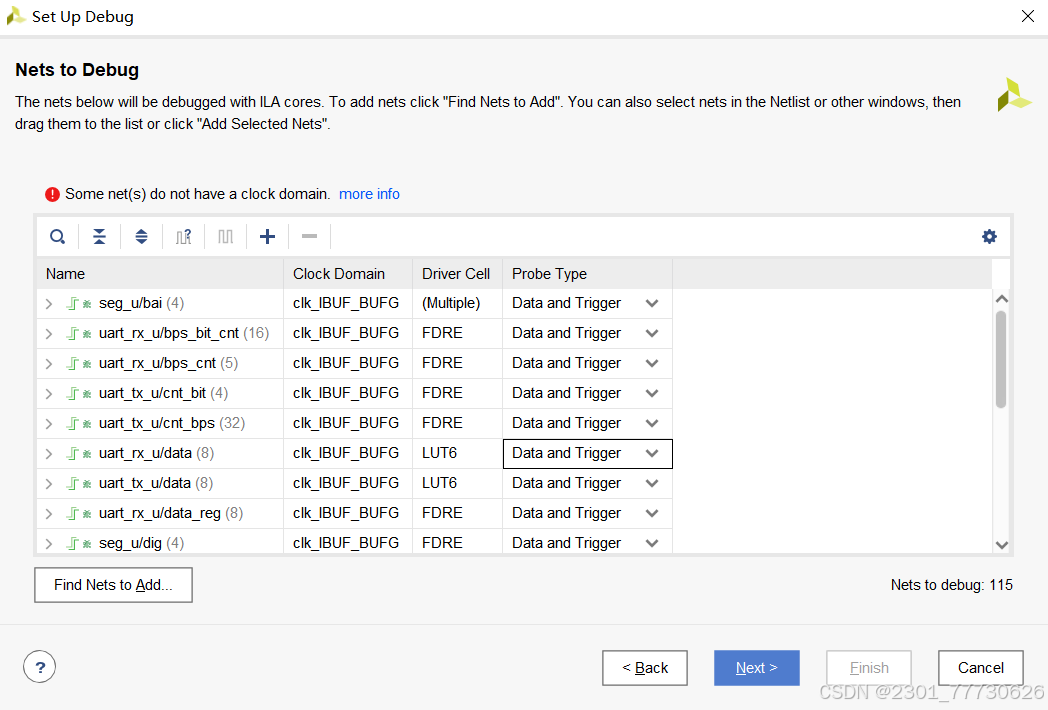

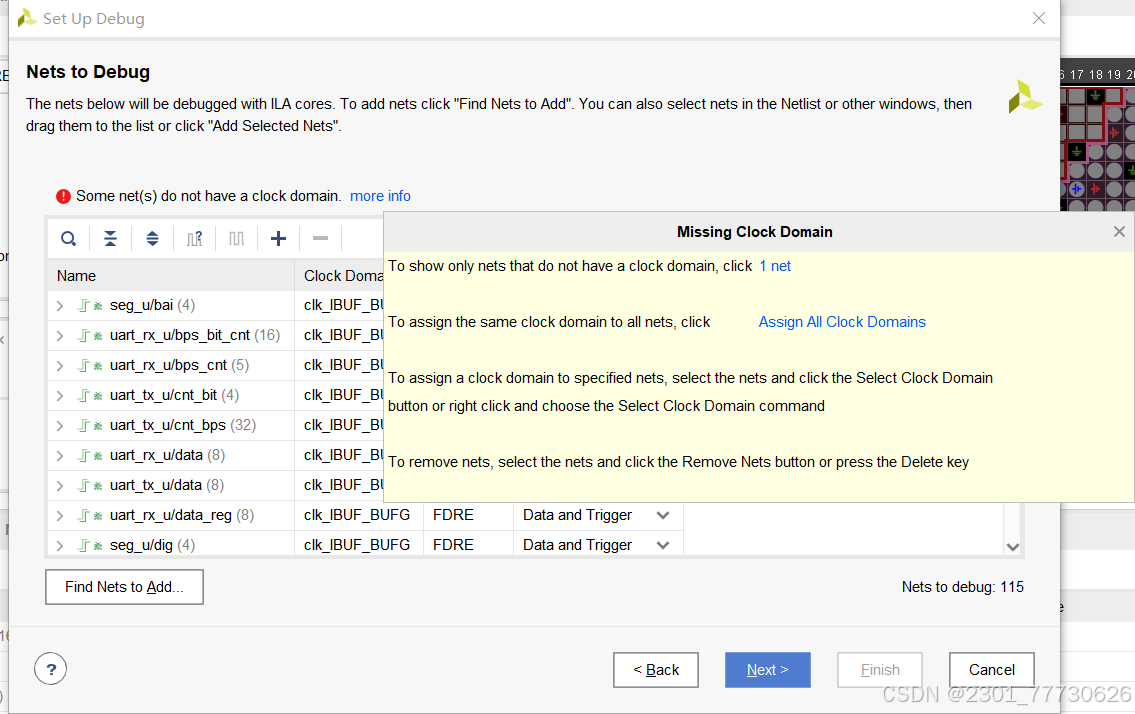

发现有报错的地方点击more info(报错的原因一般是系统无法自动定义该信号的时钟,可以手动添加clock Domain),在这里,针对每组待观察信号,时钟域可以有不同的选择(可以自己手动调整想要的时钟域)。

Missing Clock Domain可以快速定位到没有定义时钟的信号上。

这里和IP核的用法一样

然后就完成环境搭建。

3.ILA 调试及板级验证

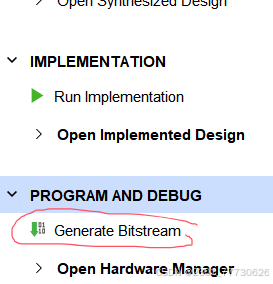

生成 bit 文件

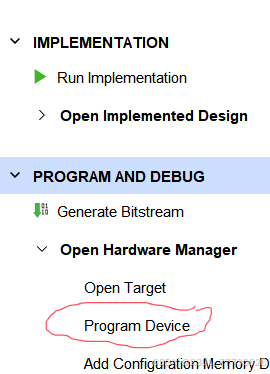

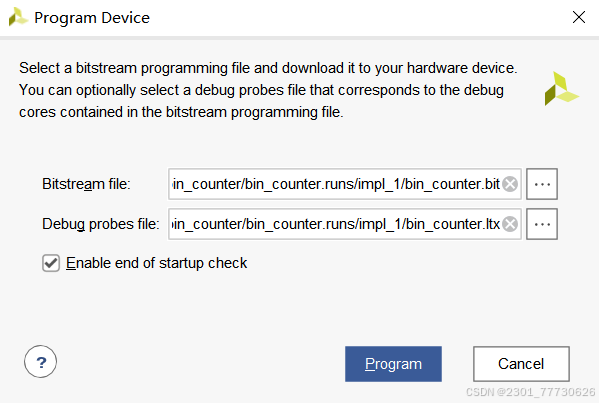

Open Target 是连接开发板,Program Device将生成文件下载到开发板

将生成文件下载到开发板

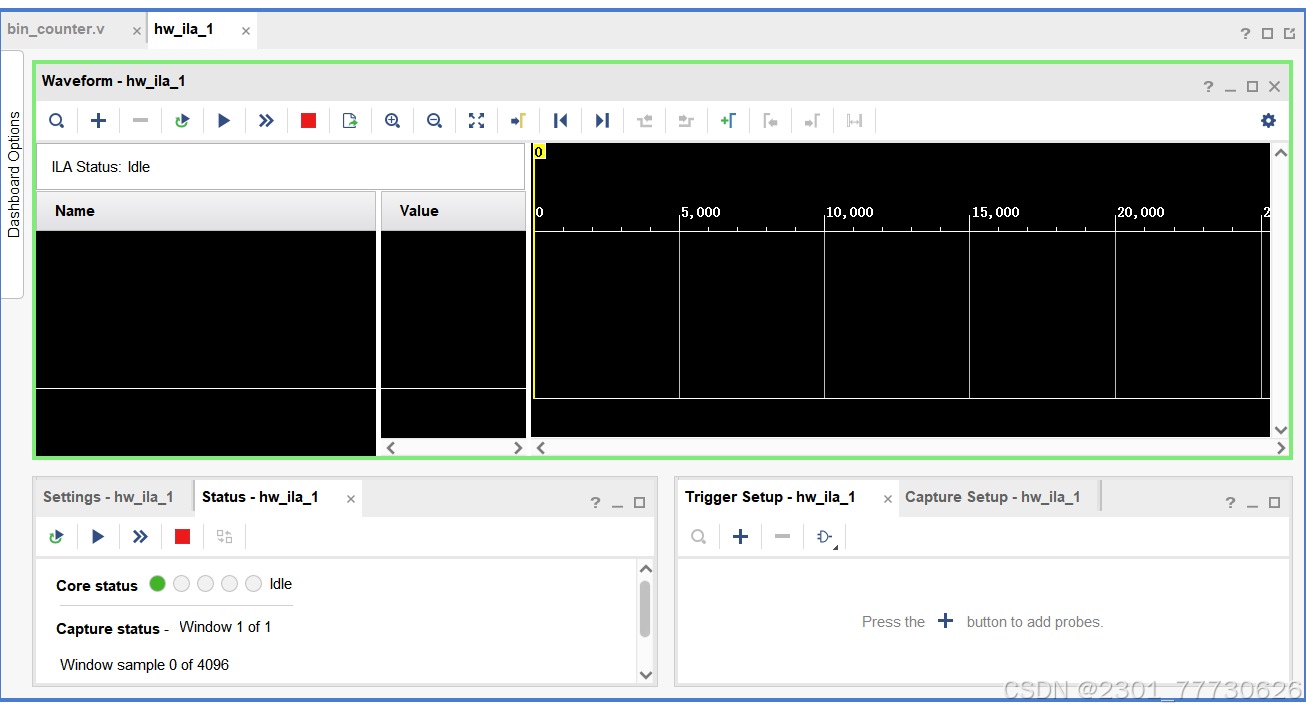

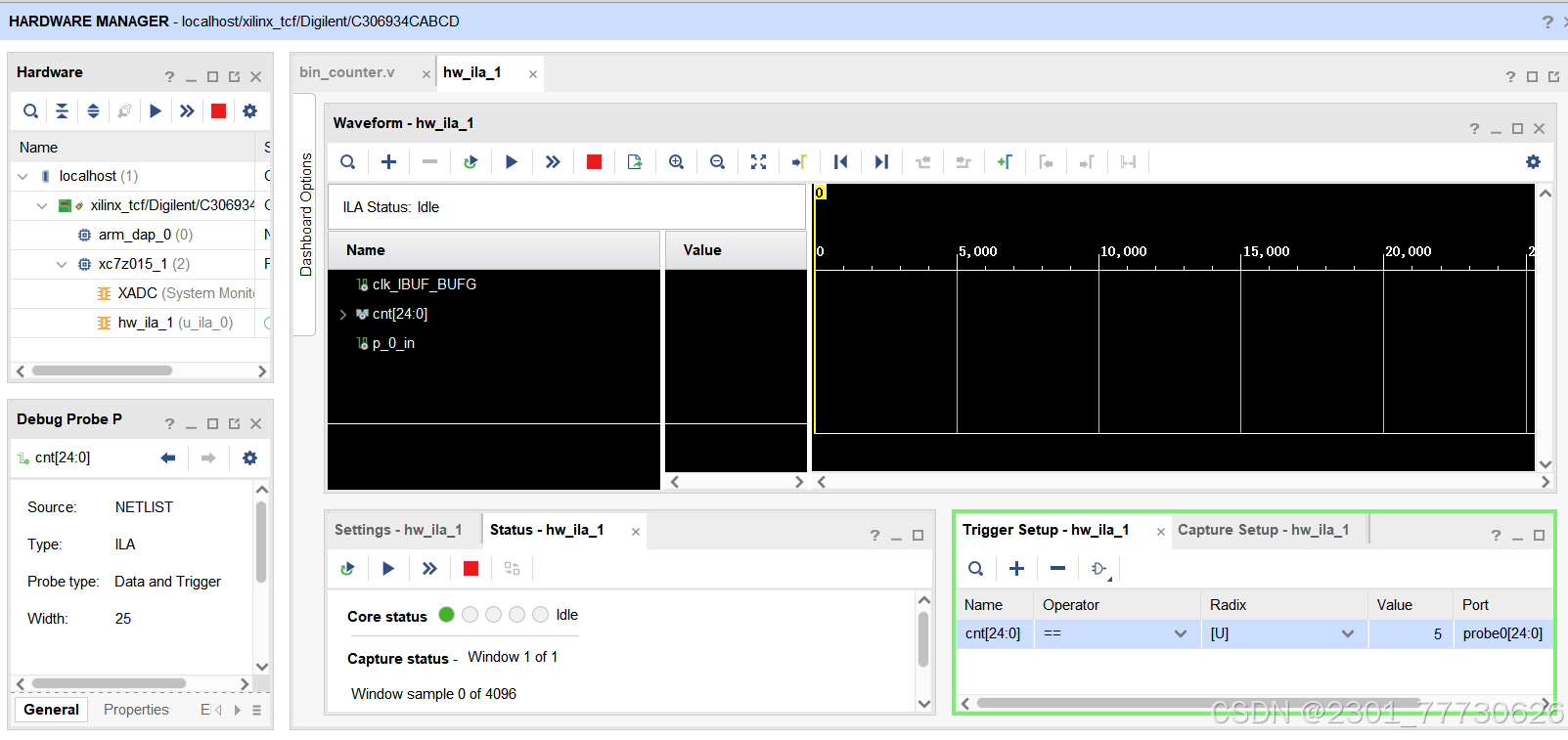

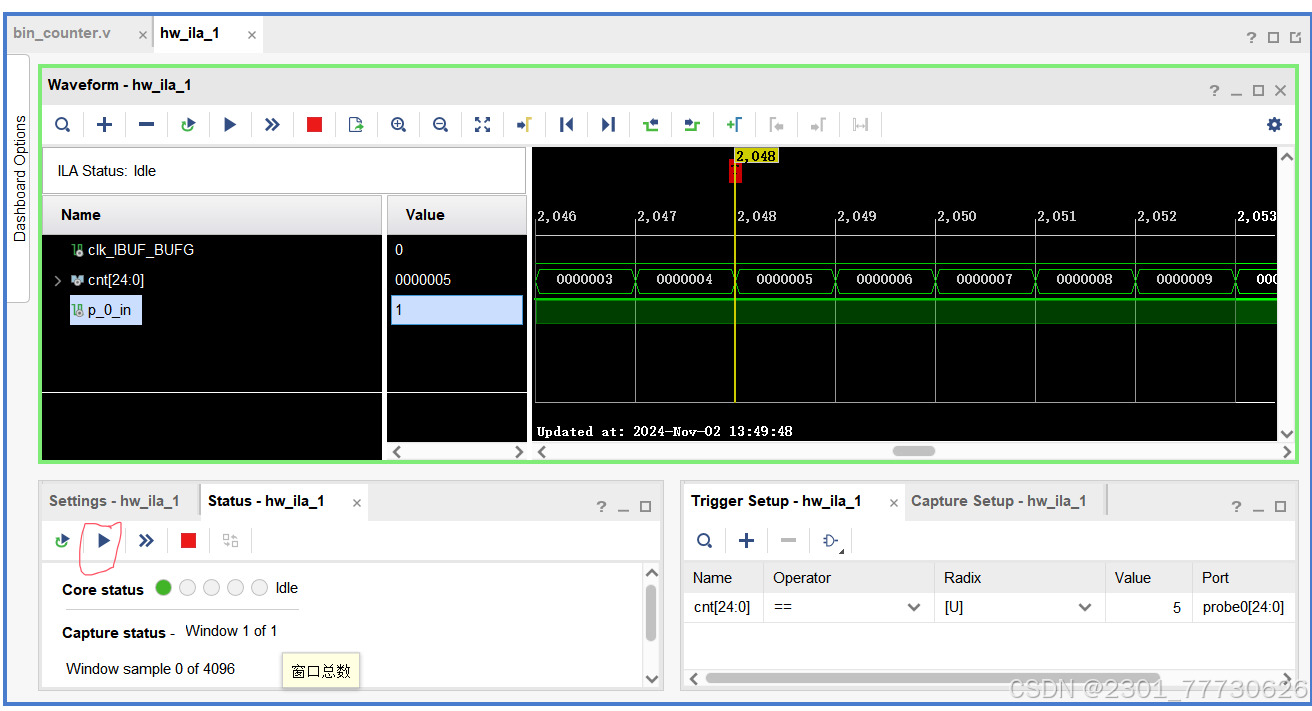

这个是ila的界面

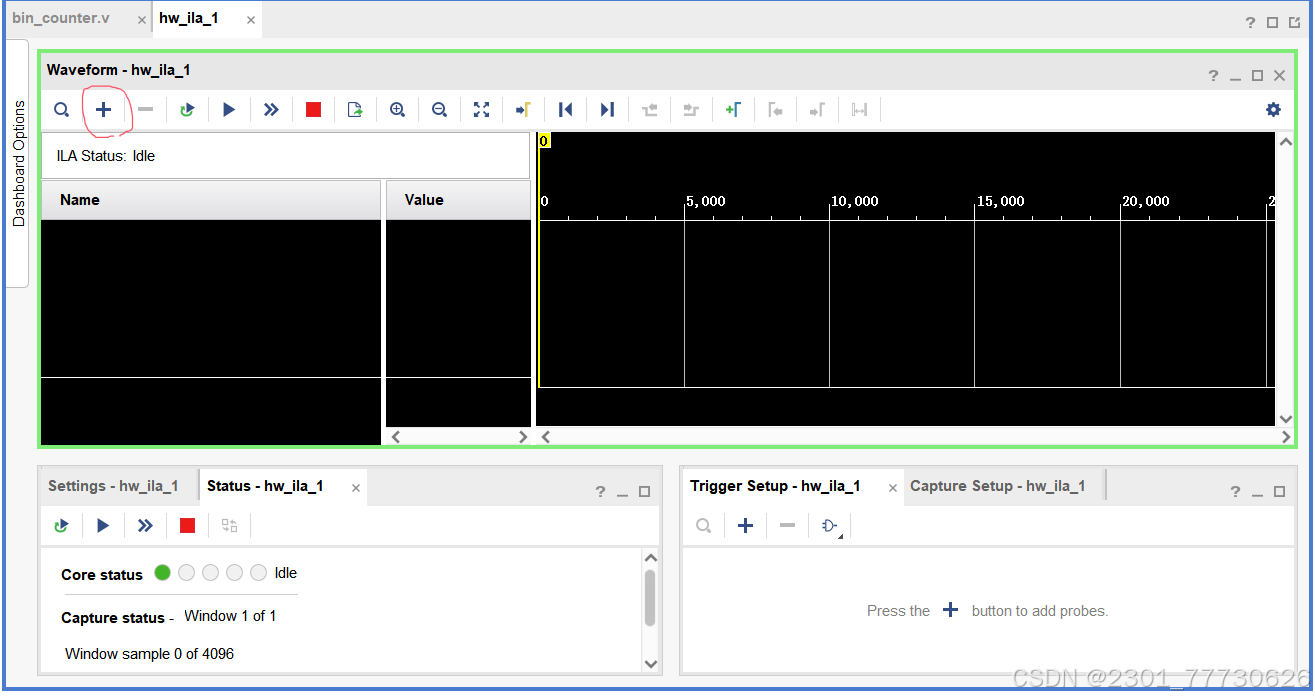

这里的加号可以将你想要查看的标志信号添加出来

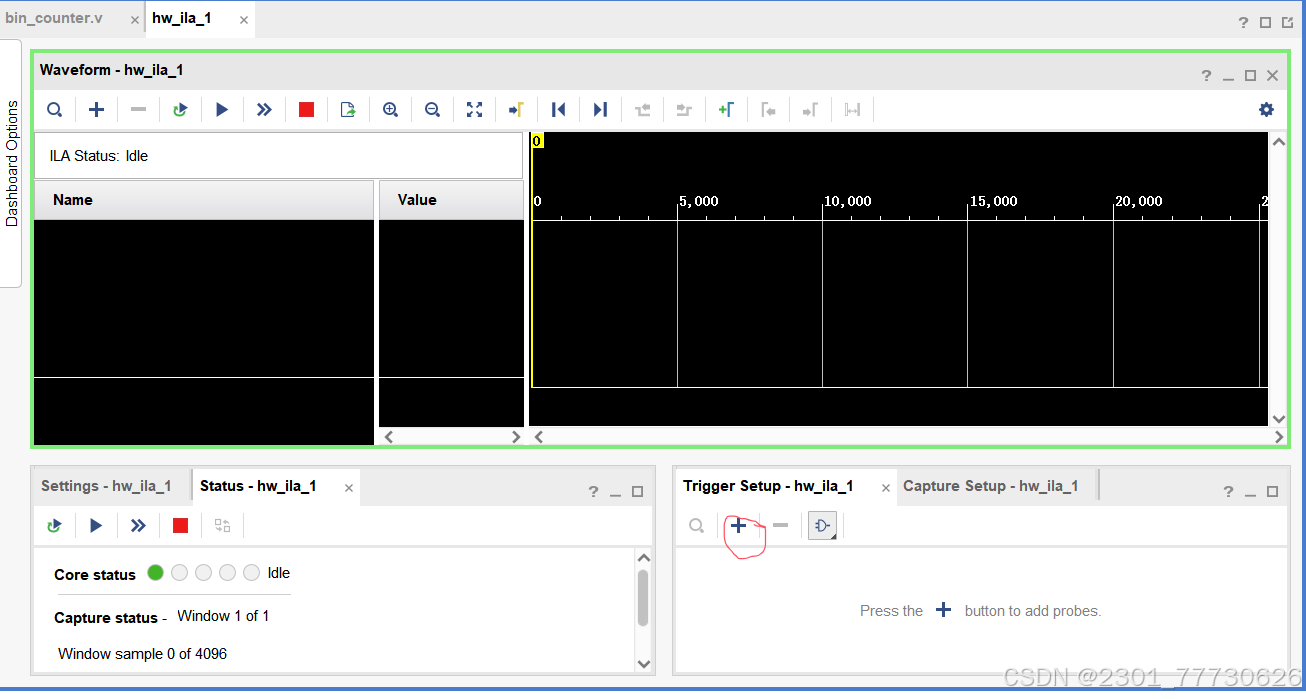

这里的加号可以将你标志的信号添加出来作为查看的条件

右下角的Name是你的信号名,Operator是比较符号,Value是你输入的数据(这个数据是什么取决于你的项目的某个信号的改变或达到某个数值导致其他信号的变化来决定),Port是那个探针。

设置好后,点击运行,就会生成波形

4.使用手感

Ip核:设计时需要手动调整每个探针位宽,比较麻烦,但好处是用完ila后几乎不用处理。

建议大型项目使用

使用Debug:设计时可以直接添加,操作快速,但是在用完ila后需要手动删除语句(如果不删会消耗资源)。建议小型项目使用

4862

4862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?