1、调试目的

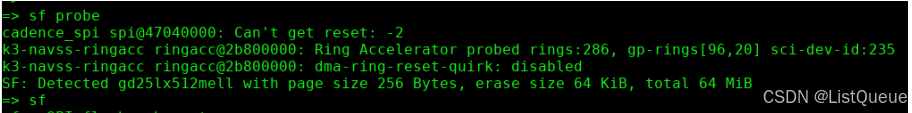

提供的uboot支持OSPI flash(gd25lx512met)正常的读写,而且读写的数据正确。包括OSPI的启动方式下,可以正常启动。

2、遇到的问题

无法从MCU域:R5正常启动spl。

3、解决思路

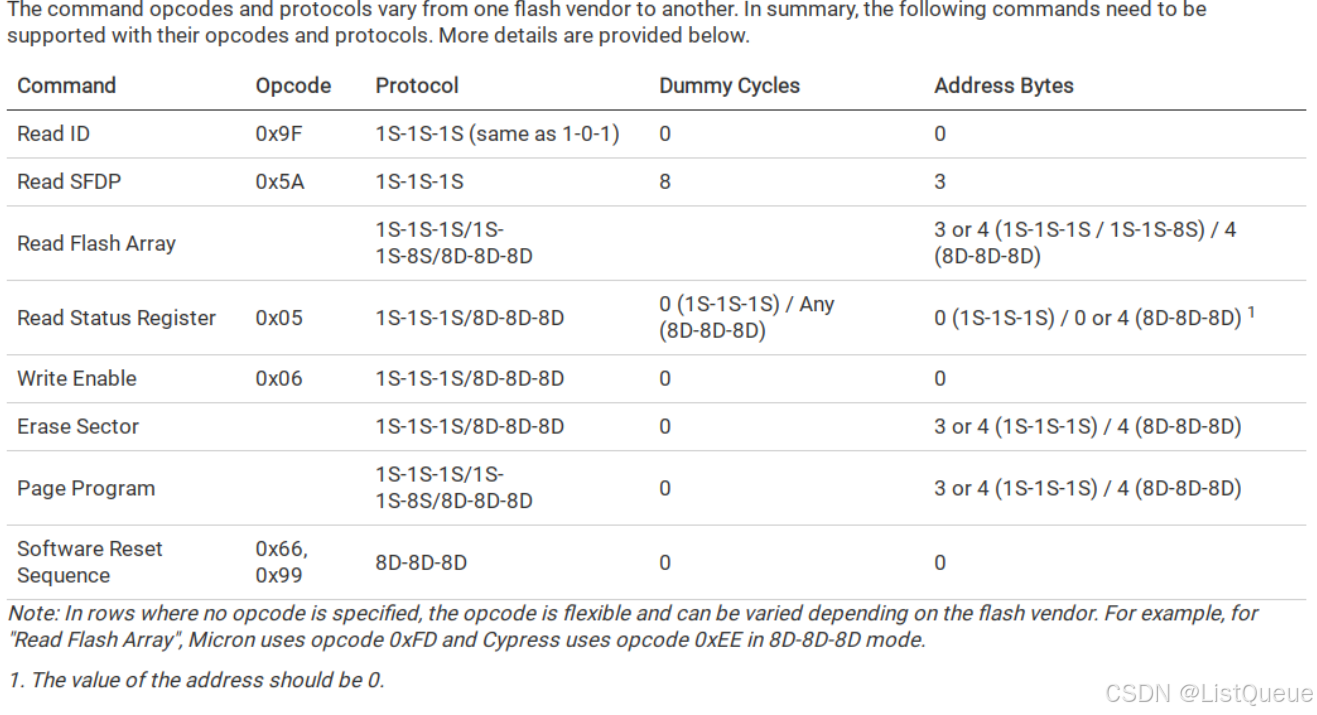

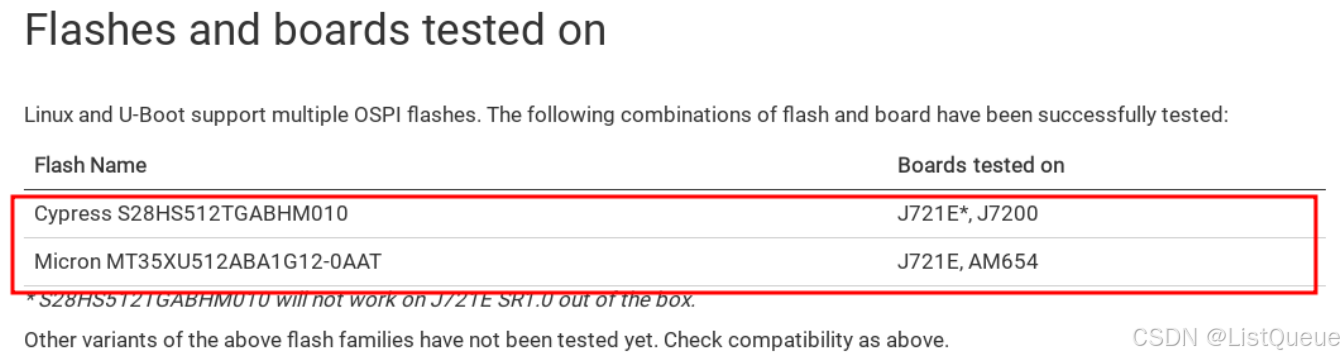

3.1、从TI相关的资料上,查看OSPI FLASH的要求。

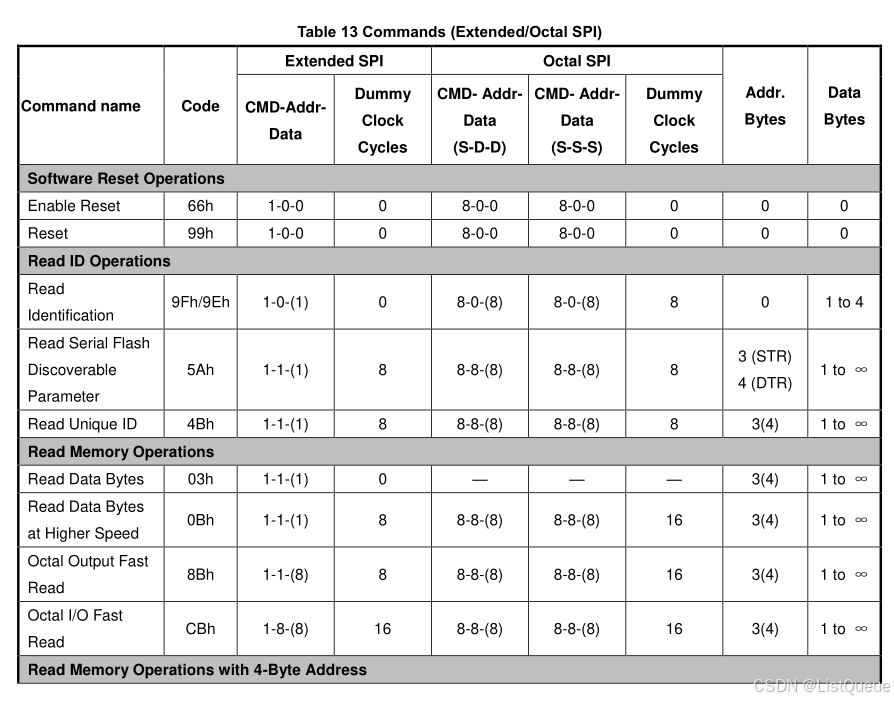

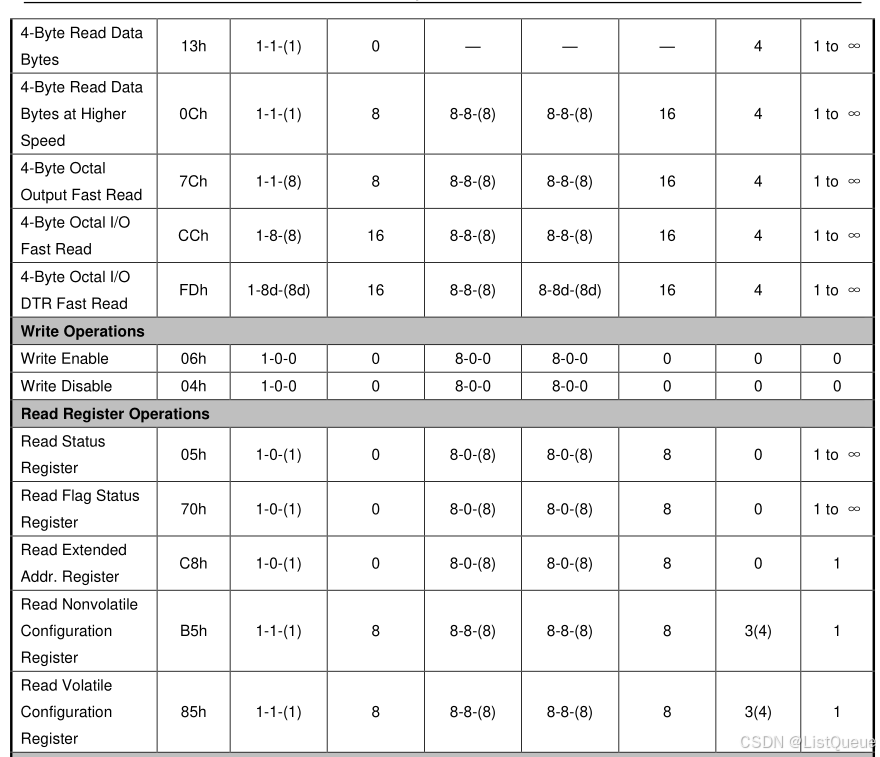

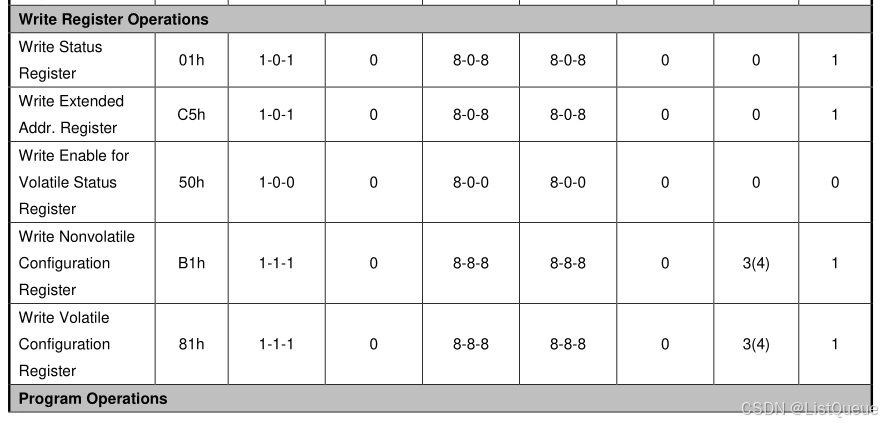

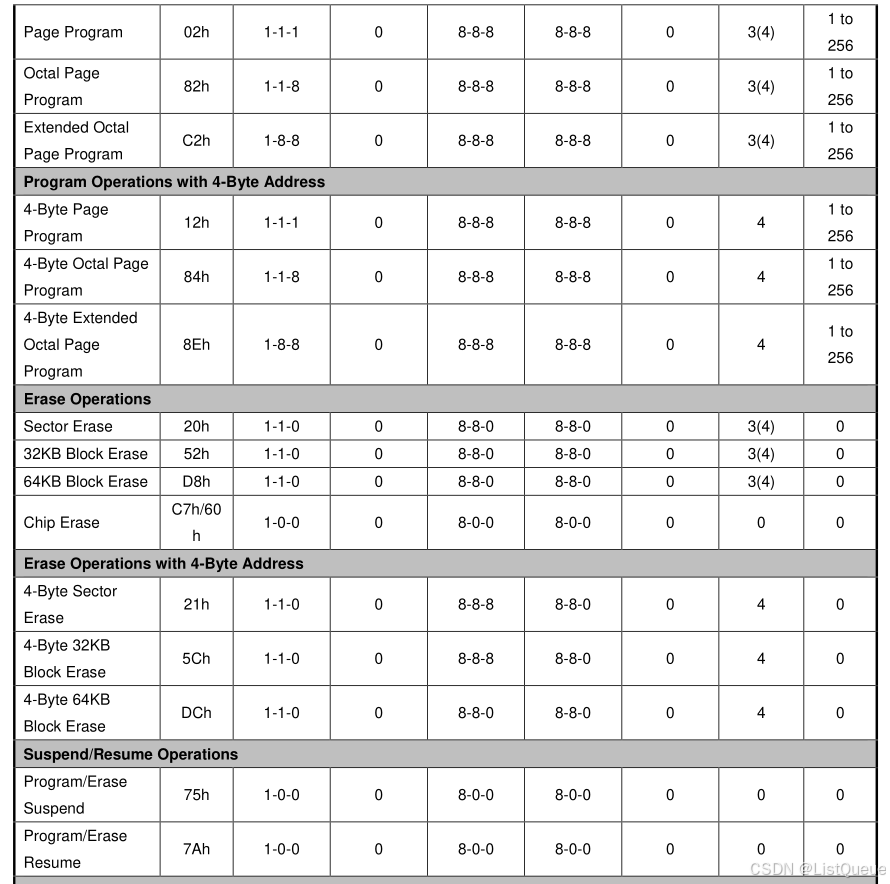

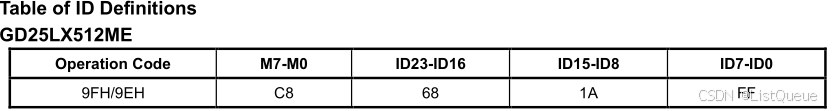

查看gd25lx512met的芯片手册以及与GD FAE的沟通是可以满足TI对于OSPI的要求的。

gd25lx512met芯片手册:

故:初步判定gd25lx512met满足要求。

3.2、开始制作启动镜像和验证flash的功能

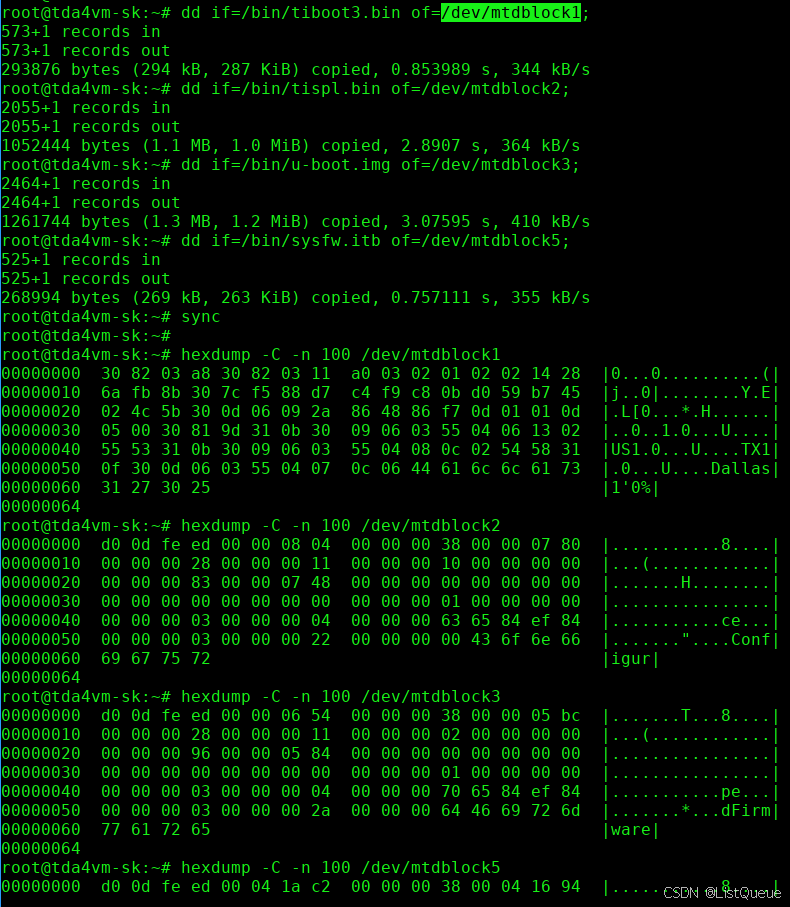

进入kernel后,通过dd命令,按照预设的分区表,烧录相应的镜像。

从dd的命令和hexdump的命令判定,flash在内核可以正常读写。

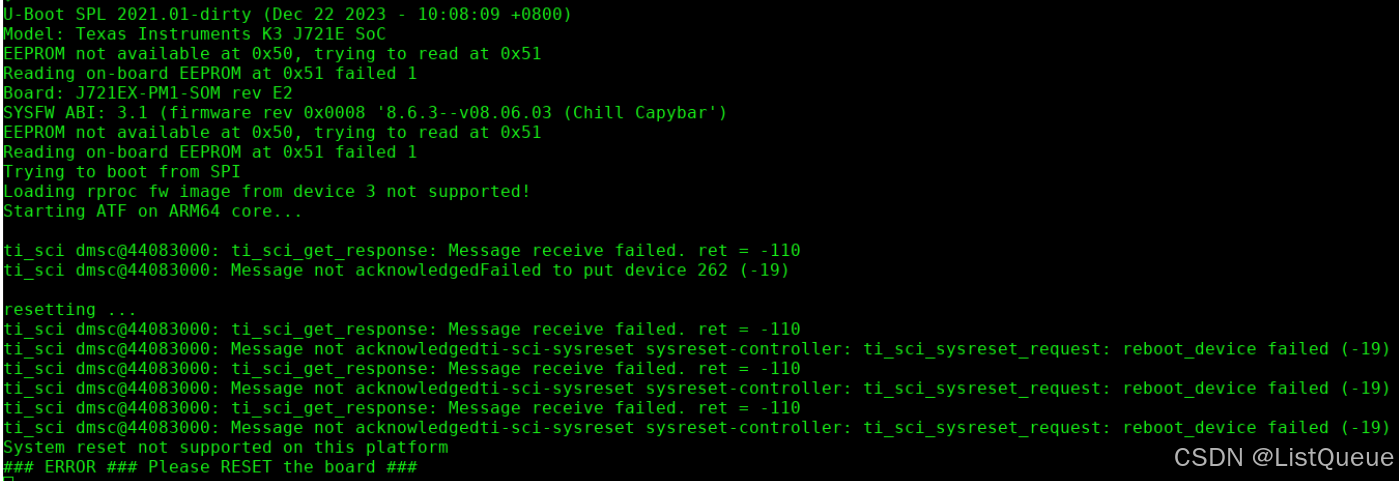

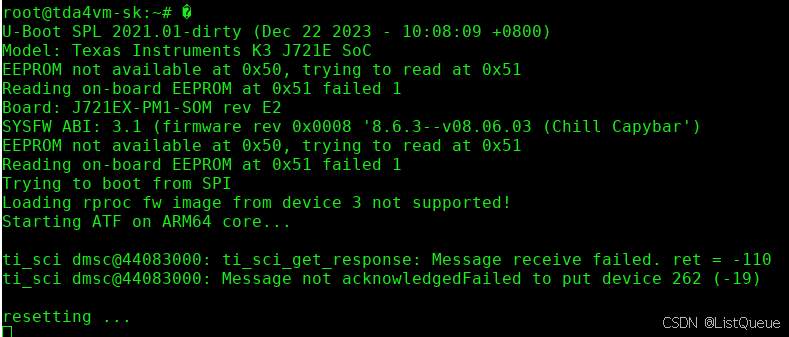

然后重启设备,选择从ospi启动,则出现报错。

为进一步寻找原因,尝试在TI的相关网站和资料库查找资料,然后在TI上找到ospi启动的说明,参考:3.1.1.7. OSPI/QSPI — Processor SDK Linux for J721e Documentation

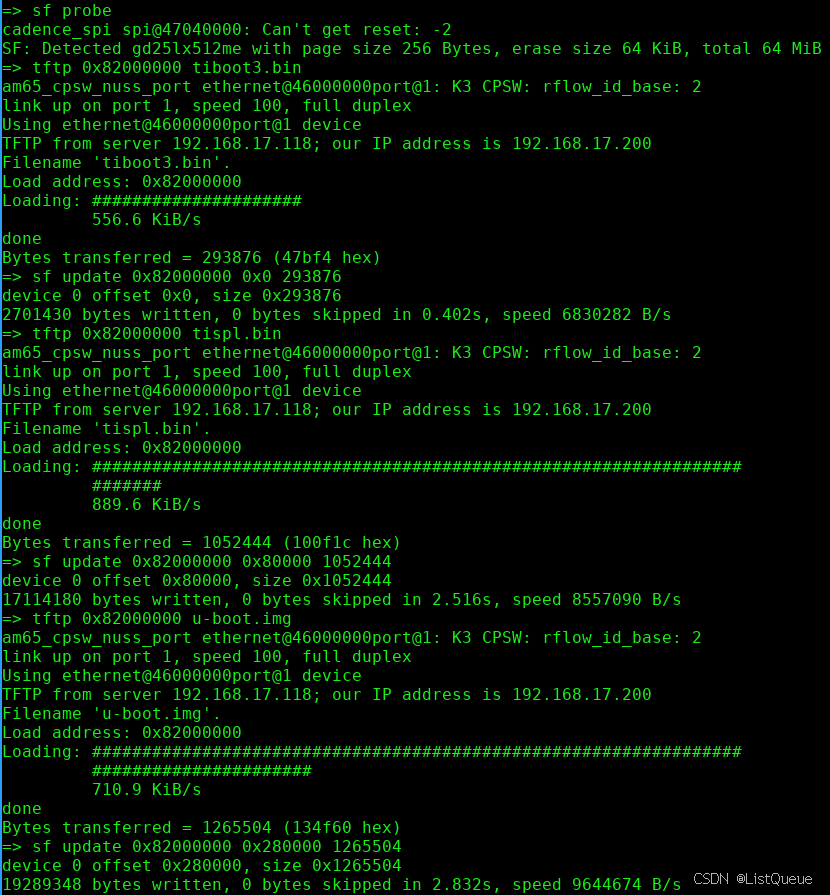

尝试试验:

然而并没有达到预期的效果。

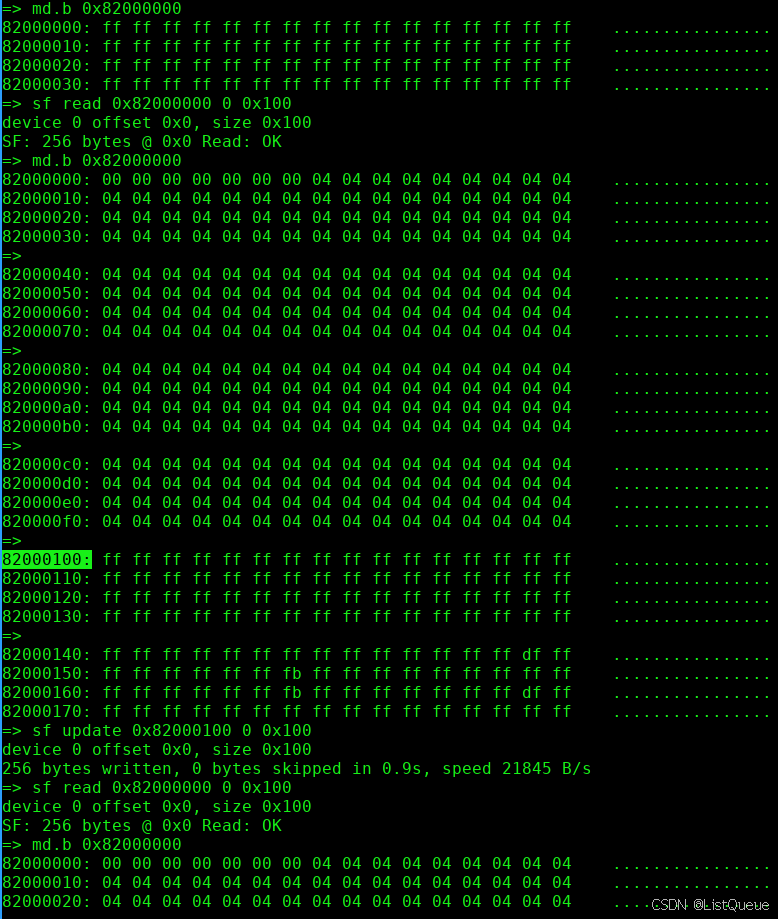

进一步发现,从log上看,并不是我更新的tiboot的镜像,而是原来的,故在uboot做flash的读写试验。

如下:

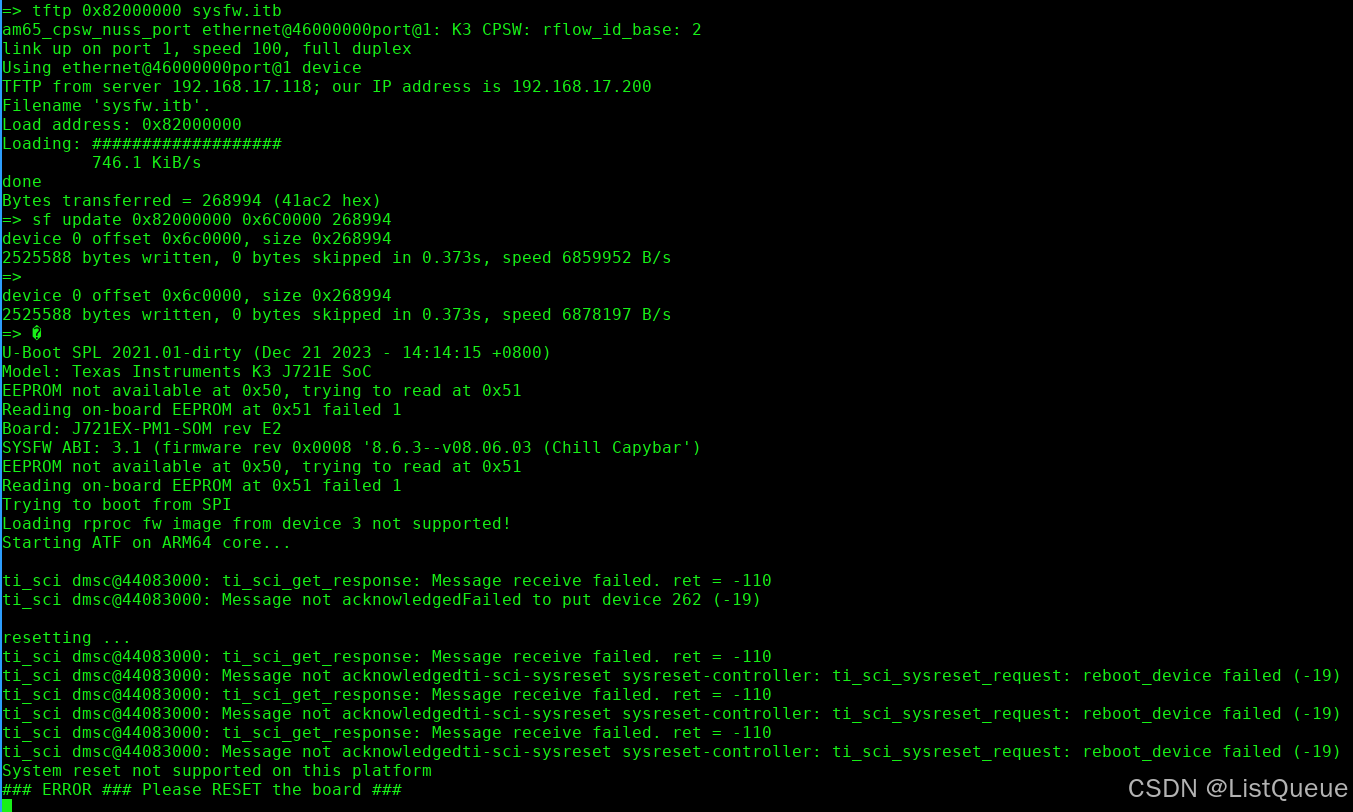

试验证明,在uboot下,对gd25lx512met表现上的日志看起来是读写ok,但实际上并没有读写成功。

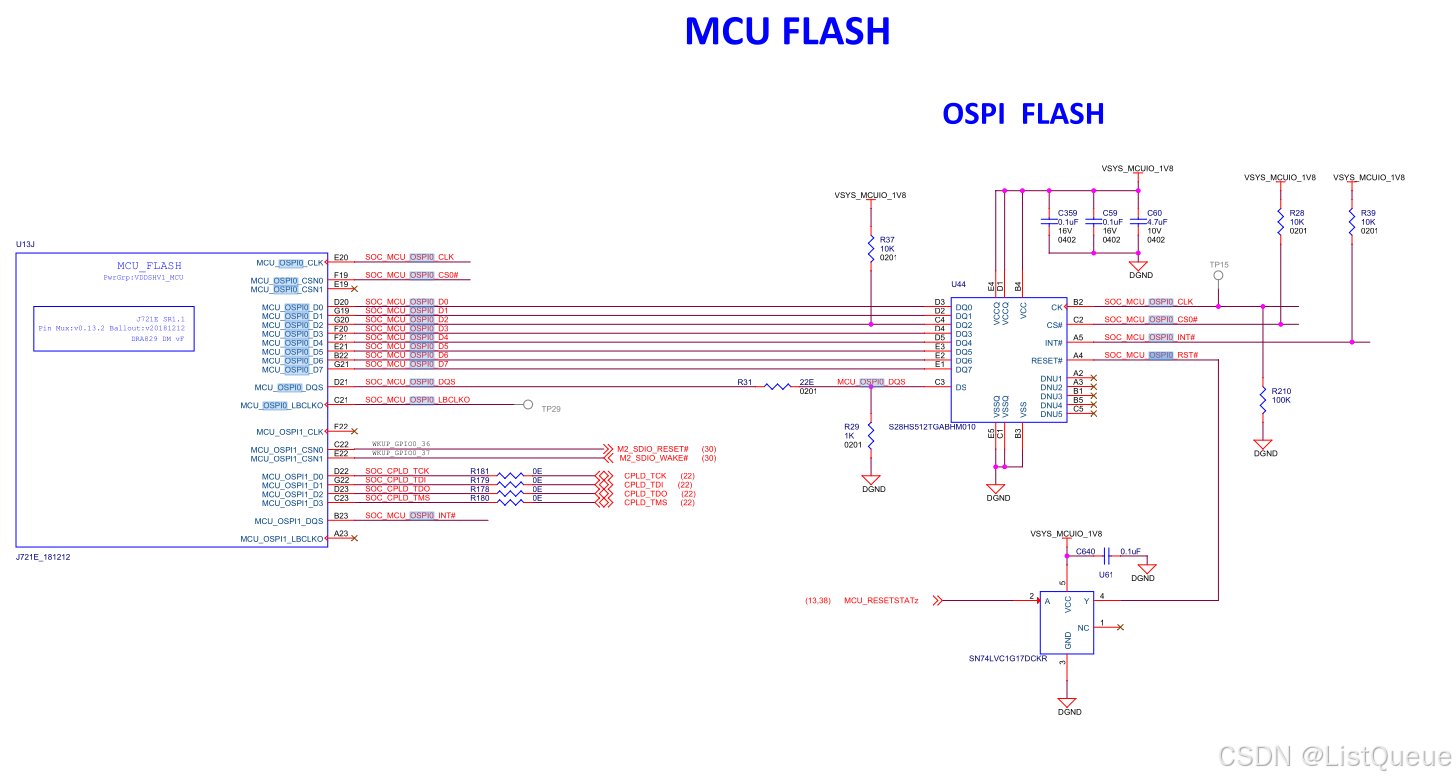

三、查看硬件原理图的接法。

看来还是代码的问题,继续看驱动代码:(经过验证OK的代码修改)

diff --git a/drivers/mtd/spi/sf_internal.h b/drivers/mtd/spi/sf_internal.h

index ade9f15138..13d168454c 100644

--- a/drivers/mtd/spi/sf_internal.h

+++ b/drivers/mtd/spi/sf_internal.h

@@ -18,6 +18,7 @@

#define CONFIG_SPI_FLASH_WINBOND 1

#define CONFIG_SPI_FLASH_GIGADEVICE 1

+#define CONFIG_SPI_FLASH_GD25XX 1

struct flash_info {

#if !CONFIG_IS_ENABLED(SPI_FLASH_TINY)

diff --git a/drivers/mtd/spi/spi-nor-core.c b/drivers/mtd/spi/spi-nor-core.c

index 61c6071e0d..b0b00f906b 100644

--- a/drivers/mtd/spi/spi-nor-core.c

+++ b/drivers/mtd/spi/spi-nor-core.c

@@ -3704,6 +3704,90 @@ int spi_nor_remove(struct spi_nor *nor)

return 0;

}

+

+#ifdef CONFIG_SPI_FLASH_GD25XX

+static int spi_nor_gigadevice_octal_dtr_enable(struct spi_nor *nor)

+{

+ struct spi_mem_op op;

+ u8 buf;

+ u8 addr_width = 3;

+ int ret;

+

+ /* Set dummy cycles for Fast Read to the default of 20. */

+ ret = write_enable(nor);

+ if (ret)

+ return ret;

+

+ buf = 20;

+ op = (struct spi_mem_op)

+ SPI_MEM_OP(SPI_MEM_OP_CMD(SPINOR_OP_MT_WR_ANY_REG, 1),

+ SPI_MEM_OP_ADDR(addr_width, SPINOR_REG_MT_CFR1V, 1),

+ SPI_MEM_OP_NO_DUMMY,

+ SPI_MEM_OP_DATA_OUT(1, &buf, 1));

+ ret = spi_mem_exec_op(nor->spi, &op);

+ if (ret)

+ return ret;

+

+ ret = spi_nor_wait_till_ready(nor);

+ if (ret)

+ return ret;

+

+ nor->read_dummy = 20;

+

+ ret = write_enable(nor);

+ if (ret)

+ return ret;

+

+ buf = SPINOR_MT_OCT_DTR;

+ op = (struct spi_mem_op)

+ SPI_MEM_OP(SPI_MEM_OP_CMD(SPINOR_OP_MT_WR_ANY_REG, 1),

+ SPI_MEM_OP_ADDR(addr_width, SPINOR_REG_MT_CFR0V, 1),

+ SPI_MEM_OP_NO_DUMMY,

+ SPI_MEM_OP_DATA_OUT(1, &buf, 1));

+ ret = spi_mem_exec_op(nor->spi, &op);

+ if (ret) {

+ dev_err(nor->dev, "Failed to enable octal DTR mode\n");

+ return ret;

+ }

+

+ return 0;

+}

+

+static void gd25lx512me_default_init(struct spi_nor *nor)

+{

+ nor->octal_dtr_enable = spi_nor_gigadevice_octal_dtr_enable;

+}

+

+static void gd25lx512me_post_sfdp_fixup(struct spi_nor *nor,

+ struct spi_nor_flash_parameter *params)

+{

+ /* Set the Fast Read settings. */

+ params->hwcaps.mask |= SNOR_HWCAPS_READ_8_8_8_DTR;

+ spi_nor_set_read_settings(¶ms->reads[SNOR_CMD_READ_8_8_8_DTR],

+ 0, 20, SPINOR_OP_MT_DTR_RD,

+ SNOR_PROTO_8_8_8_DTR);

+

+ params->hwcaps.mask |= SNOR_HWCAPS_PP_8_8_8_DTR;

+

+ nor->cmd_ext_type = SPI_NOR_EXT_REPEAT;

+ params->rdsr_dummy = 8;

+ params->rdsr_addr_nbytes = 0;

+

+ /*

+ * The BFPT quad enable field is set to a reserved value so the quad

+ * enable function is ignored by spi_nor_parse_bfpt(). Make sure we

+ * disable it.

+ */

+ params->quad_enable = NULL;

+}

+

+static struct spi_nor_fixups gd25lx512me_fixups = {

+ .default_init = gd25lx512me_default_init,

+ .post_sfdp = gd25lx512me_post_sfdp_fixup,

+};

+#endif /* CONFIG_SPI_FLASH_GD25XX */

+

+

void spi_nor_set_fixups(struct spi_nor *nor)

{

#ifdef CONFIG_SPI_FLASH_SPANSION

@@ -3729,6 +3813,12 @@ void spi_nor_set_fixups(struct spi_nor *nor)

if (!strcmp(nor->info->name, "mt35xu512aba"))

nor->fixups = &mt35xu512aba_fixups;

#endif

+

+#ifdef CONFIG_SPI_FLASH_GD25XX

+ if (!strcmp(nor->info->name, "gd25lx512me"))

+ nor->fixups = &gd25lx512me_fixups;

+#endif

+

}

int spi_nor_scan(struct spi_nor *nor)

diff --git a/drivers/mtd/spi/spi-nor-ids.c b/drivers/mtd/spi/spi-nor-ids.c

index de6ba1d22d..0a9d1e97ed 100644

--- a/drivers/mtd/spi/spi-nor-ids.c

+++ b/drivers/mtd/spi/spi-nor-ids.c

@@ -107,11 +107,6 @@ const struct flash_info spi_nor_ids[] = {

SECT_4K | SPI_NOR_DUAL_READ | SPI_NOR_QUAD_READ |

SPI_NOR_HAS_LOCK | SPI_NOR_HAS_TB)

},

- {

- INFO("gd25lx512me", 0xc8681a, 0, 64 * 1024, 1024,

- SECT_4K | SPI_NOR_DUAL_READ | SPI_NOR_QUAD_READ |

- SPI_NOR_HAS_LOCK | SPI_NOR_HAS_TB)

- },

{

INFO("gd25q128", 0xc84018, 0, 64 * 1024, 256,

SECT_4K | SPI_NOR_DUAL_READ | SPI_NOR_QUAD_READ |

@@ -192,6 +187,8 @@ const struct flash_info spi_nor_ids[] = {

{ INFO("n25q00a", 0x20bb21, 0, 64 * 1024, 2048, SECT_4K | USE_FSR | SPI_NOR_QUAD_READ | NO_CHIP_ERASE) },

{ INFO("mt25ql01g", 0x21ba20, 0, 64 * 1024, 2048, SECT_4K | USE_FSR | SPI_NOR_QUAD_READ | NO_CHIP_ERASE) },

{ INFO("mt25qu02g", 0x20bb22, 0, 64 * 1024, 4096, SECT_4K | USE_FSR | SPI_NOR_QUAD_READ | NO_CHIP_ERASE) },

+ { INFO("gd25lx512me", 0xc8681a, 0, 64 * 1024, 1024, SECT_4K | USE_FSR | SPI_NOR_OCTAL_READ | SPI_NOR_4B_OPCODES | SPI_NOR_OCTAL_DTR_READ)},

+

#ifdef CONFIG_SPI_FLASH_MT35XU

{ INFO("mt35xu512aba", 0x2c5b1a, 0, 128 * 1024, 512, USE_FSR | SPI_NOR_OCTAL_READ | SPI_NOR_4B_OPCODES | SPI_NOR_OCTAL_DTR_READ) },

#endif /* CONFIG_SPI_FLASH_MT35XU */

474

474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?