说明:J721E这个芯片 TI官方是没有提供相关的配置支持的,芯片手册是有相关的gpmc的说明,故调试记录如下:

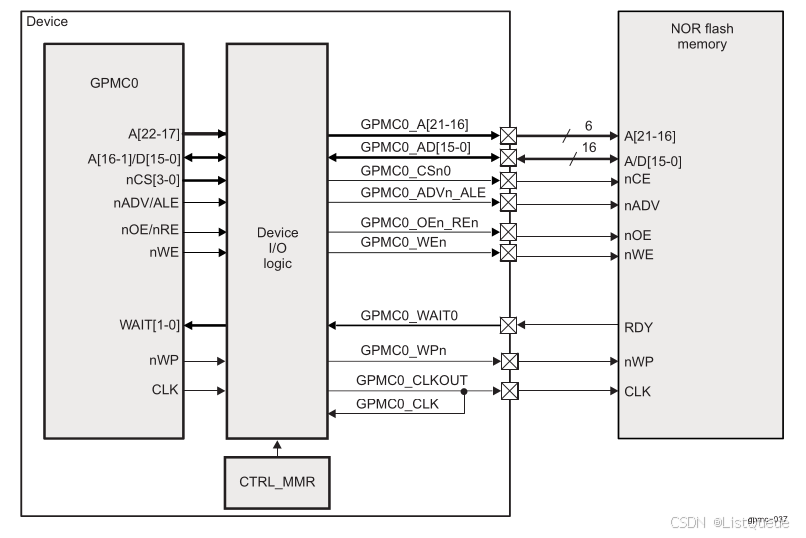

我们这个GPMC接口硬件上连接的是FPGA,作为大数据传输通信使用。

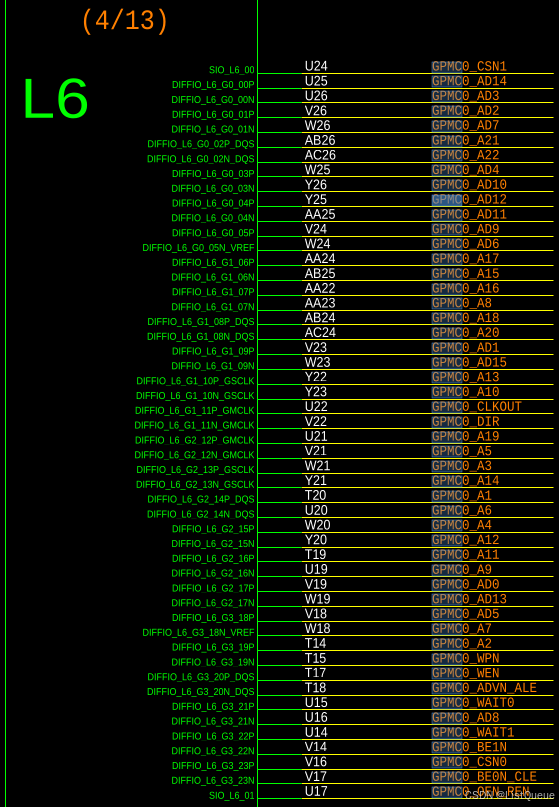

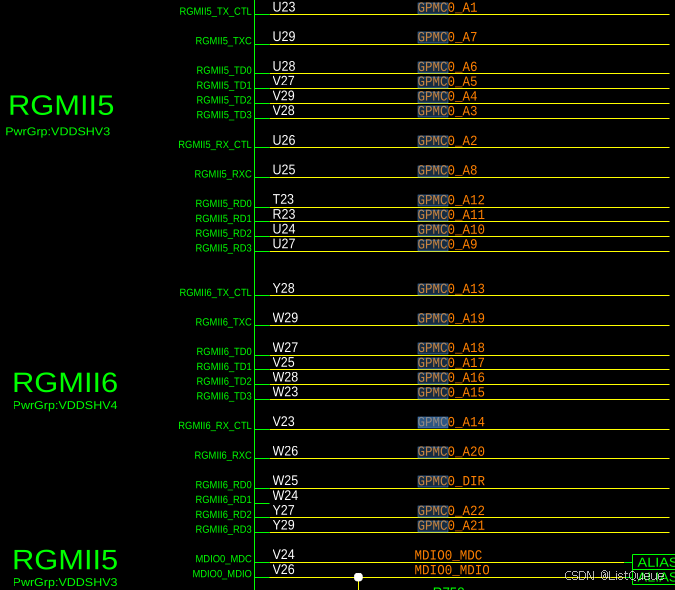

硬件原理图:

从硬件上使用了引脚复用的情况,故使用PinMux工具配置时特别注意

先给出完整设备树配置:

diff --git a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

index 36d245780..2a3fa1cb8 100644

--- a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

+++ b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

@@ -12,7 +12,7 @@

/ {

compatible = "ti,j721e-sk", "ti,j721e";

model = "Texas Instruments J721E Common";

chosen {

stdout-path = "serial2:115200n8";

@@ -418,7 +418,7 @@ J721E_IOPAD(0x20c, PIN_OUTPUT, 0) /* (W6) MCAN0_TX */

main_mcan0_gpio_pins_default: main-mcan0-gpio-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x108, PIN_INPUT, 7) /* (AD27) PRG0_PRU1_GPO2.GPIO0_65 */

+ //J721E_IOPAD(0x108, PIN_INPUT, 7) /* (AD27) PRG0_PRU1_GPO2.GPIO0_65 */

>;

};

@@ -437,14 +437,14 @@ J721E_IOPAD(0x10c, PIN_INPUT, 7) /* (AC25) PRG0_PRU1_GPO3.GPIO0_66 */

main_mcan9_pins_default: main-mcan9-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0xd0, PIN_INPUT, 6) /* (AC27) PRG0_PRU0_GPO8.MCAN9_RX */

- J721E_IOPAD(0xcc, PIN_OUTPUT, 6) /* (AC28) PRG0_PRU0_GPO7.MCAN9_TX */

+ //J721E_IOPAD(0xd0, PIN_INPUT, 6) /* (AC27) PRG0_PRU0_GPO8.MCAN9_RX */

+ //J721E_IOPAD(0xcc, PIN_OUTPUT, 6) /* (AC28) PRG0_PRU0_GPO7.MCAN9_TX */

>;

};

main_mcan9_gpio_pins_default: main-mcan9-gpio-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x110, PIN_INPUT, 7) /* (AD29) PRG0_PRU1_GPO4.GPIO0_67 */

+ //J721E_IOPAD(0x110, PIN_INPUT, 7) /* (AD29) PRG0_PRU1_GPO4.GPIO0_67 */

>;

};

@@ -467,12 +467,12 @@ dss_vout0_pins_default: dss-vout0-pins-default {

//J721E_IOPAD(0x60, PIN_OUTPUT, 10) /* (AF23) PRG1_PRU1_GPO2.VOUT0_DATA2 */

//J721E_IOPAD(0x64, PIN_OUTPUT, 10) /* (AD23) PRG1_PRU1_GPO3.VOUT0_DATA3 */

//J721E_IOPAD(0x68, PIN_OUTPUT, 10) /* (AH24) PRG1_PRU1_GPO4.VOUT0_DATA4 */

- J721E_IOPAD(0x6c, PIN_OUTPUT, 10) /* (AG21) PRG1_PRU1_GPO5.VOUT0_DATA5 */

+ //J721E_IOPAD(0x6c, PIN_OUTPUT, 10) /* (AG21) PRG1_PRU1_GPO5.VOUT0_DATA5 */

//J721E_IOPAD(0x70, PIN_OUTPUT, 10) /* (AE23) PRG1_PRU1_GPO6.VOUT0_DATA6 */

J721E_IOPAD(0x74, PIN_OUTPUT, 10) /* (AC21) PRG1_PRU1_GPO7.VOUT0_DATA7 */

J721E_IOPAD(0x78, PIN_OUTPUT, 10) /* (Y23) PRG1_PRU1_GPO8.VOUT0_DATA8 */

- J721E_IOPAD(0x7c, PIN_OUTPUT, 10) /* (AF21) PRG1_PRU1_GPO9.VOUT0_DATA9 */

- J721E_IOPAD(0x80, PIN_OUTPUT, 10) /* (AB23) PRG1_PRU1_GPO10.VOUT0_DATA10 */

+ //J721E_IOPAD(0x7c, PIN_OUTPUT, 10) /* (AF21) PRG1_PRU1_GPO9.VOUT0_DATA9 */

+ //J721E_IOPAD(0x80, PIN_OUTPUT, 10) /* (AB23) PRG1_PRU1_GPO10.VOUT0_DATA10 */

//J721E_IOPAD(0x84, PIN_OUTPUT, 10) /* (AJ25) PRG1_PRU1_GPO11.VOUT0_DATA11 */

//J721E_IOPAD(0x88, PIN_OUTPUT, 10) /* (AH25) PRG1_PRU1_GPO12.VOUT0_DATA12 */

//J721E_IOPAD(0x8c, PIN_OUTPUT, 10) /* (AG25) PRG1_PRU1_GPO13.VOUT0_DATA13 */

@@ -484,8 +484,8 @@ J721E_IOPAD(0x38, PIN_OUTPUT, 10) /* (AG24) PRG1_PRU0_GPO13.VOUT0_DATA18 */

J721E_IOPAD(0x3c, PIN_OUTPUT, 10) /* (AD24) PRG1_PRU0_GPO14.VOUT0_DATA19 */

J721E_IOPAD(0x40, PIN_OUTPUT, 10) /* (AC24) PRG1_PRU0_GPO15.VOUT0_DATA20 */

J721E_IOPAD(0x44, PIN_OUTPUT, 10) /* (AE24) PRG1_PRU0_GPO16.VOUT0_DATA21 */

- J721E_IOPAD(0x24, PIN_OUTPUT, 10) /* (AJ20) PRG1_PRU0_GPO8.VOUT0_DATA22 */

- J721E_IOPAD(0x28, PIN_OUTPUT, 10) /* (AG20) PRG1_PRU0_GPO9.VOUT0_DATA23 */

+ //J721E_IOPAD(0x24, PIN_OUTPUT, 10) /* (AJ20) PRG1_PRU0_GPO8.VOUT0_DATA22 */

+ //J721E_IOPAD(0x28, PIN_OUTPUT, 10) /* (AG20) PRG1_PRU0_GPO9.VOUT0_DATA23 */

J721E_IOPAD(0x9c, PIN_OUTPUT, 10) /* (AC22) PRG1_PRU1_GPO17.VOUT0_DE */

//J721E_IOPAD(0x98, PIN_OUTPUT, 10) /* (AJ26) PRG1_PRU1_GPO16.VOUT0_HSYNC */

J721E_IOPAD(0xa4, PIN_OUTPUT, 10) /* (AH22) PRG1_PRU1_GPO19.VOUT0_PCLK */

@@ -508,13 +508,13 @@ hdmi_pdn_pins_default: hdmi-pdn-pins-default {

/* Reset for M.2 E Key slot on PCIe0 */

ekey_reset_pins_default: ekey-reset-pns-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x124, PIN_INPUT, 7) /* (Y24) PRG0_PRU1_GPO9.GPIO0_72 */

+ //J721E_IOPAD(0x124, PIN_INPUT, 7) /* (Y24) PRG0_PRU1_GPO9.GPIO0_72 */

>;

};

main_i2c5_pins_default: main-i2c5-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x150, PIN_INPUT_PULLUP, 2) /* (Y26) PRG0_MDIO0_MDIO.I2C5_SCL */

+ //J721E_IOPAD(0x150, PIN_INPUT_PULLUP, 2) /* (Y26) PRG0_MDIO0_MDIO.I2C5_SCL */

J721E_IOPAD(0x154, PIN_INPUT_PULLUP, 2) /* (AA27) PRG0_MDIO0_MDC.I2C5_SDA */

>;

};

@@ -522,28 +522,28 @@ J721E_IOPAD(0x154, PIN_INPUT_PULLUP, 2) /* (AA27) PRG0_MDIO0_MDC.I2C5_SDA */

rpi_header_gpio0_pins_default: rpi-header-gpio0-pins-default {

pinctrl-single,pins = <

J721E_IOPAD(0x01C, PIN_INPUT, 7) /* (AD22) PRG1_PRU0_GPO6.GPIO0_7 */

- J721E_IOPAD(0x120, PIN_INPUT, 7) /* (AA28) PRG0_PRU1_GPO8.GPIO0_71 */

- J721E_IOPAD(0x14C, PIN_INPUT, 7) /* (AA29) PRG0_PRU1_GPO19.GPIO0_82 */

+ //J721E_IOPAD(0x120, PIN_INPUT, 7) /* (AA28) PRG0_PRU1_GPO8.GPIO0_71 */

+ //J721E_IOPAD(0x14C, PIN_INPUT, 7) /* (AA29) PRG0_PRU1_GPO19.GPIO0_82 */

J721E_IOPAD(0x02C, PIN_INPUT, 7) /* (AD21) PRG1_PRU0_GPO10.GPIO0_11 */

- J721E_IOPAD(0x198, PIN_INPUT, 7) /* (V25) RGMII6_TD1.GPIO0_101 */

+ //J721E_IOPAD(0x198, PIN_INPUT, 7) /* (V25) RGMII6_TD1.GPIO0_101 */

J721E_IOPAD(0x1B0, PIN_INPUT, 7) /* (W24) RGMII6_RD1.GPIO0_107 */

- J721E_IOPAD(0x1A0, PIN_INPUT, 7) /* (W29) RGMII6_TXC.GPIO0_103 */

+ //J721E_IOPAD(0x1A0, PIN_INPUT, 7) /* (W29) RGMII6_TXC.GPIO0_103 */

J721E_IOPAD(0x008, PIN_INPUT, 7) /* (AG22) PRG1_PRU0_GPO1.GPIO0_2 */

//J721E_IOPAD(0x1D0, PIN_INPUT, 7) /* (AA3) SPI0_D1.GPIO0_115 */

- J721E_IOPAD(0x11C, PIN_INPUT, 7) /* (AA24) PRG0_PRU1_GPO7.GPIO0_70 */

- J721E_IOPAD(0x148, PIN_INPUT, 7) /* (AA26) PRG0_PRU1_GPO18.GPIO0_81 */

+ //J721E_IOPAD(0x11C, PIN_INPUT, 7) /* (AA24) PRG0_PRU1_GPO7.GPIO0_70 */

+ //J721E_IOPAD(0x148, PIN_INPUT, 7) /* (AA26) PRG0_PRU1_GPO18.GPIO0_81 */

J721E_IOPAD(0x004, PIN_INPUT, 7) /* (AC23) PRG1_PRU0_GPO0.GPIO0_1 */

J721E_IOPAD(0x014, PIN_INPUT, 7) /* (AH23) PRG1_PRU0_GPO4.GPIO0_5 */

J721E_IOPAD(0x020, PIN_INPUT, 7) /* (AE20) PRG1_PRU0_GPO7.GPIO0_8 */

- };

-

-

gpmc0: memory-controller@3b000000 {

compatible = "ti,am64-gpmc";

power-domains = <&k3_pds 80 TI_SCI_PD_EXCLUSIVE>;

diff --git a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

index 36d245780..2a3fa1cb8 100644

--- a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

+++ b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

@@ -12,7 +12,7 @@

/ {

compatible = "ti,j721e-sk", "ti,j721e";

model = "Texas Instruments J721E Common";

chosen {

stdout-path = "serial2:115200n8";

@@ -418,7 +418,7 @@ J721E_IOPAD(0x20c, PIN_OUTPUT, 0) /* (W6) MCAN0_TX */

main_mcan0_gpio_pins_default: main-mcan0-gpio-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x108, PIN_INPUT, 7) /* (AD27) PRG0_PRU1_GPO2.GPIO0_65 */

+ //J721E_IOPAD(0x108, PIN_INPUT, 7) /* (AD27) PRG0_PRU1_GPO2.GPIO0_65 */

>;

};

@@ -437,14 +437,14 @@ J721E_IOPAD(0x10c, PIN_INPUT, 7) /* (AC25) PRG0_PRU1_GPO3.GPIO0_66 */

main_mcan9_pins_default: main-mcan9-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0xd0, PIN_INPUT, 6) /* (AC27) PRG0_PRU0_GPO8.MCAN9_RX */

- J721E_IOPAD(0xcc, PIN_OUTPUT, 6) /* (AC28) PRG0_PRU0_GPO7.MCAN9_TX */

+ //J721E_IOPAD(0xd0, PIN_INPUT, 6) /* (AC27) PRG0_PRU0_GPO8.MCAN9_RX */

+ //J721E_IOPAD(0xcc, PIN_OUTPUT, 6) /* (AC28) PRG0_PRU0_GPO7.MCAN9_TX */

>;

};

main_mcan9_gpio_pins_default: main-mcan9-gpio-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x110, PIN_INPUT, 7) /* (AD29) PRG0_PRU1_GPO4.GPIO0_67 */

+ //J721E_IOPAD(0x110, PIN_INPUT, 7) /* (AD29) PRG0_PRU1_GPO4.GPIO0_67 */

>;

};

@@ -467,12 +467,12 @@ dss_vout0_pins_default: dss-vout0-pins-default {

//J721E_IOPAD(0x60, PIN_OUTPUT, 10) /* (AF23) PRG1_PRU1_GPO2.VOUT0_DATA2 */

//J721E_IOPAD(0x64, PIN_OUTPUT, 10) /* (AD23) PRG1_PRU1_GPO3.VOUT0_DATA3 */

//J721E_IOPAD(0x68, PIN_OUTPUT, 10) /* (AH24) PRG1_PRU1_GPO4.VOUT0_DATA4 */

- J721E_IOPAD(0x6c, PIN_OUTPUT, 10) /* (AG21) PRG1_PRU1_GPO5.VOUT0_DATA5 */

+ //J721E_IOPAD(0x6c, PIN_OUTPUT, 10) /* (AG21) PRG1_PRU1_GPO5.VOUT0_DATA5 */

//J721E_IOPAD(0x70, PIN_OUTPUT, 10) /* (AE23) PRG1_PRU1_GPO6.VOUT0_DATA6 */

J721E_IOPAD(0x74, PIN_OUTPUT, 10) /* (AC21) PRG1_PRU1_GPO7.VOUT0_DATA7 */

J721E_IOPAD(0x78, PIN_OUTPUT, 10) /* (Y23) PRG1_PRU1_GPO8.VOUT0_DATA8 */

- J721E_IOPAD(0x7c, PIN_OUTPUT, 10) /* (AF21) PRG1_PRU1_GPO9.VOUT0_DATA9 */

- J721E_IOPAD(0x80, PIN_OUTPUT, 10) /* (AB23) PRG1_PRU1_GPO10.VOUT0_DATA10 */

+ //J721E_IOPAD(0x7c, PIN_OUTPUT, 10) /* (AF21) PRG1_PRU1_GPO9.VOUT0_DATA9 */

+ //J721E_IOPAD(0x80, PIN_OUTPUT, 10) /* (AB23) PRG1_PRU1_GPO10.VOUT0_DATA10 */

//J721E_IOPAD(0x84, PIN_OUTPUT, 10) /* (AJ25) PRG1_PRU1_GPO11.VOUT0_DATA11 */

//J721E_IOPAD(0x88, PIN_OUTPUT, 10) /* (AH25) PRG1_PRU1_GPO12.VOUT0_DATA12 */

//J721E_IOPAD(0x8c, PIN_OUTPUT, 10) /* (AG25) PRG1_PRU1_GPO13.VOUT0_DATA13 */

@@ -484,8 +484,8 @@ J721E_IOPAD(0x38, PIN_OUTPUT, 10) /* (AG24) PRG1_PRU0_GPO13.VOUT0_DATA18 */

J721E_IOPAD(0x3c, PIN_OUTPUT, 10) /* (AD24) PRG1_PRU0_GPO14.VOUT0_DATA19 */

J721E_IOPAD(0x40, PIN_OUTPUT, 10) /* (AC24) PRG1_PRU0_GPO15.VOUT0_DATA20 */

J721E_IOPAD(0x44, PIN_OUTPUT, 10) /* (AE24) PRG1_PRU0_GPO16.VOUT0_DATA21 */

- J721E_IOPAD(0x24, PIN_OUTPUT, 10) /* (AJ20) PRG1_PRU0_GPO8.VOUT0_DATA22 */

- J721E_IOPAD(0x28, PIN_OUTPUT, 10) /* (AG20) PRG1_PRU0_GPO9.VOUT0_DATA23 */

+ //J721E_IOPAD(0x24, PIN_OUTPUT, 10) /* (AJ20) PRG1_PRU0_GPO8.VOUT0_DATA22 */

+ //J721E_IOPAD(0x28, PIN_OUTPUT, 10) /* (AG20) PRG1_PRU0_GPO9.VOUT0_DATA23 */

J721E_IOPAD(0x9c, PIN_OUTPUT, 10) /* (AC22) PRG1_PRU1_GPO17.VOUT0_DE */

//J721E_IOPAD(0x98, PIN_OUTPUT, 10) /* (AJ26) PRG1_PRU1_GPO16.VOUT0_HSYNC */

J721E_IOPAD(0xa4, PIN_OUTPUT, 10) /* (AH22) PRG1_PRU1_GPO19.VOUT0_PCLK */

@@ -508,13 +508,13 @@ hdmi_pdn_pins_default: hdmi-pdn-pins-default {

/* Reset for M.2 E Key slot on PCIe0 */

ekey_reset_pins_default: ekey-reset-pns-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x124, PIN_INPUT, 7) /* (Y24) PRG0_PRU1_GPO9.GPIO0_72 */

+ //J721E_IOPAD(0x124, PIN_INPUT, 7) /* (Y24) PRG0_PRU1_GPO9.GPIO0_72 */

>;

};

main_i2c5_pins_default: main-i2c5-pins-default {

pinctrl-single,pins = <

- J721E_IOPAD(0x150, PIN_INPUT_PULLUP, 2) /* (Y26) PRG0_MDIO0_MDIO.I2C5_SCL */

+ //J721E_IOPAD(0x150, PIN_INPUT_PULLUP, 2) /* (Y26) PRG0_MDIO0_MDIO.I2C5_SCL */

J721E_IOPAD(0x154, PIN_INPUT_PULLUP, 2) /* (AA27) PRG0_MDIO0_MDC.I2C5_SDA */

>;

};

@@ -522,28 +522,28 @@ J721E_IOPAD(0x154, PIN_INPUT_PULLUP, 2) /* (AA27) PRG0_MDIO0_MDC.I2C5_SDA */

rpi_header_gpio0_pins_default: rpi-header-gpio0-pins-default {

pinctrl-single,pins = <

J721E_IOPAD(0x01C, PIN_INPUT, 7) /* (AD22) PRG1_PRU0_GPO6.GPIO0_7 */

- J721E_IOPAD(0x120, PIN_INPUT, 7) /* (AA28) PRG0_PRU1_GPO8.GPIO0_71 */

- J721E_IOPAD(0x14C, PIN_INPUT, 7) /* (AA29) PRG0_PRU1_GPO19.GPIO0_82 */

+ //J721E_IOPAD(0x120, PIN_INPUT, 7) /* (AA28) PRG0_PRU1_GPO8.GPIO0_71 */

+ //J721E_IOPAD(0x14C, PIN_INPUT, 7) /* (AA29) PRG0_PRU1_GPO19.GPIO0_82 */

J721E_IOPAD(0x02C, PIN_INPUT, 7) /* (AD21) PRG1_PRU0_GPO10.GPIO0_11 */

- J721E_IOPAD(0x198, PIN_INPUT, 7) /* (V25) RGMII6_TD1.GPIO0_101 */

+ //J721E_IOPAD(0x198, PIN_INPUT, 7) /* (V25) RGMII6_TD1.GPIO0_101 */

J721E_IOPAD(0x1B0, PIN_INPUT, 7) /* (W24) RGMII6_RD1.GPIO0_107 */

- J721E_IOPAD(0x1A0, PIN_INPUT, 7) /* (W29) RGMII6_TXC.GPIO0_103 */

+ //J721E_IOPAD(0x1A0, PIN_INPUT, 7) /* (W29) RGMII6_TXC.GPIO0_103 */

J721E_IOPAD(0x008, PIN_INPUT, 7) /* (AG22) PRG1_PRU0_GPO1.GPIO0_2 */

//J721E_IOPAD(0x1D0, PIN_INPUT, 7) /* (AA3) SPI0_D1.GPIO0_115 */

- J721E_IOPAD(0x11C, PIN_INPUT, 7) /* (AA24) PRG0_PRU1_GPO7.GPIO0_70 */

- J721E_IOPAD(0x148, PIN_INPUT, 7) /* (AA26) PRG0_PRU1_GPO18.GPIO0_81 */

+ //J721E_IOPAD(0x11C, PIN_INPUT, 7) /* (AA24) PRG0_PRU1_GPO7.GPIO0_70 */

+ //J721E_IOPAD(0x148, PIN_INPUT, 7) /* (AA26) PRG0_PRU1_GPO18.GPIO0_81 */

J721E_IOPAD(0x004, PIN_INPUT, 7) /* (AC23) PRG1_PRU0_GPO0.GPIO0_1 */

J721E_IOPAD(0x014, PIN_INPUT, 7) /* (AH23) PRG1_PRU0_GPO4.GPIO0_5 */

J721E_IOPAD(0x020, PIN_INPUT, 7) /* (AE20) PRG1_PRU0_GPO7.GPIO0_8 */

- J721E_IOPAD(0x19C, PIN_INPUT, 7) /* (W27) RGMII6_TD0.GPIO0_102 */

+ //J721E_IOPAD(0x19C, PIN_INPUT, 7) /* (W27) RGMII6_TD0.GPIO0_102 */

J721E_IOPAD(0x1B4, PIN_INPUT, 7) /* (W25) RGMII6_RD0.GPIO0_108 */

- J721E_IOPAD(0x188, PIN_INPUT, 7) /* (Y28) RGMII6_TX_CTL.GPIO0_97 */

+ //J721E_IOPAD(0x188, PIN_INPUT, 7) /* (Y28) RGMII6_TX_CTL.GPIO0_97 */

J721E_IOPAD(0x00C, PIN_INPUT, 7) /* (AF22) PRG1_PRU0_GPO2.GPIO0_3 */

J721E_IOPAD(0x010, PIN_INPUT, 7) /* (AJ23) PRG1_PRU0_GPO3.GPIO0_4 */

- J721E_IOPAD(0x178, PIN_INPUT, 7) /* (U27) RGMII5_RD3.GPIO0_93 */

- J721E_IOPAD(0x17C, PIN_INPUT, 7) /* (U24) RGMII5_RD2.GPIO0_94 */

- J721E_IOPAD(0x190, PIN_INPUT, 7) /* (W23) RGMII6_TD3.GPIO0_99 */

- J721E_IOPAD(0x18C, PIN_INPUT, 7) /* (V23) RGMII6_RX_CTL.GPIO0_98 */

+ //J721E_IOPAD(0x178, PIN_INPUT, 7) /* (U27) RGMII5_RD3.GPIO0_93 */

+ //J721E_IOPAD(0x17C, PIN_INPUT, 7) /* (U24) RGMII5_RD2.GPIO0_94 */

+ //J721E_IOPAD(0x190, PIN_INPUT, 7) /* (W23) RGMII6_TD3.GPIO0_99 */

+ //J721E_IOPAD(0x18C, PIN_INPUT, 7) /* (V23) RGMII6_RX_CTL.GPIO0_98 */

>;

};

@@ -593,6 +593,69 @@ J721E_IOPAD(0x98, PIN_OUTPUT, 8) /* (AJ26) PRG1_PRU1_GPO16.RGMII8_TXC */

J721E_IOPAD(0x94, PIN_OUTPUT, 8) /* (AJ27) PRG1_PRU1_GPO15.RGMII8_TX_CTL */

>;

};

+

+gpmc0_pins_default: gpmc0-default-pins {

+ pinctrl-single,pins = <

+ J721E_IOPAD(0x158, PIN_OUTPUT, 8) /* (U23) RGMII5_TX_CTL.GPMC0_A1 */

+ J721E_IOPAD(0x15c, PIN_OUTPUT, 8) /* (U26) RGMII5_RX_CTL.GPMC0_A2 */

+ J721E_IOPAD(0x160, PIN_OUTPUT, 8) /* (V28) RGMII5_TD3.GPMC0_A3 */

+ J721E_IOPAD(0x164, PIN_OUTPUT, 8) /* (V29) RGMII5_TD2.GPMC0_A4 */

+ J721E_IOPAD(0x168, PIN_OUTPUT, 8) /* (V27) RGMII5_TD1.GPMC0_A5 */

+ J721E_IOPAD(0x16c, PIN_OUTPUT, 8) /* (U28) RGMII5_TD0.GPMC0_A6 */

+ J721E_IOPAD(0x170, PIN_OUTPUT, 8) /* (U29) RGMII5_TXC.GPMC0_A7 */

+ J721E_IOPAD(0x174, PIN_OUTPUT, 8) /* (U25) RGMII5_RXC.GPMC0_A8 */

+ J721E_IOPAD(0x178, PIN_OUTPUT, 8) /* (U27) RGMII5_RD3.GPMC0_A9 */

+ J721E_IOPAD(0x17c, PIN_OUTPUT, 8) /* (U24) RGMII5_RD2.GPMC0_A10 */

+ J721E_IOPAD(0x180, PIN_OUTPUT, 8) /* (R23) RGMII5_RD1.GPMC0_A11 */

+ J721E_IOPAD(0x184, PIN_OUTPUT, 8) /* (T23) RGMII5_RD0.GPMC0_A12 */

+ J721E_IOPAD(0x188, PIN_OUTPUT, 8) /* (Y28) RGMII6_TX_CTL.GPMC0_A13 */

+ J721E_IOPAD(0x18c, PIN_OUTPUT, 8) /* (V23) RGMII6_RX_CTL.GPMC0_A14 */

+ J721E_IOPAD(0x190, PIN_OUTPUT, 8) /* (W23) RGMII6_TD3.GPMC0_A15 */

+ J721E_IOPAD(0x194, PIN_OUTPUT, 8) /* (W28) RGMII6_TD2.GPMC0_A16 */

+ J721E_IOPAD(0x198, PIN_OUTPUT, 8) /* (V25) RGMII6_TD1.GPMC0_A17 */

+ J721E_IOPAD(0x19c, PIN_OUTPUT, 8) /* (W27) RGMII6_TD0.GPMC0_A18 */

+ J721E_IOPAD(0x1a0, PIN_OUTPUT, 8) /* (W29) RGMII6_TXC.GPMC0_A19 */

+ J721E_IOPAD(0x1a4, PIN_OUTPUT, 8) /* (W26) RGMII6_RXC.GPMC0_A20 */

+ J721E_IOPAD(0x1a8, PIN_OUTPUT, 8) /* (Y29) RGMII6_RD3.GPMC0_A21 */

+ J721E_IOPAD(0x1ac, PIN_OUTPUT, 8) /* (Y27) RGMII6_RD2.GPMC0_A22 */

+ J721E_IOPAD(0x108, PIN_OUTPUT, 8) /* (AD27) PRG0_PRU1_GPO2.GPMC0_A23 */

+ J721E_IOPAD(0x110, PIN_OUTPUT, 8) /* (AD29) PRG0_PRU1_GPO4.GPMC0_A24 */

+ J721E_IOPAD(0x118, PIN_OUTPUT, 8) /* (AC26) PRG0_PRU1_GPO6.GPMC0_A25 */

+ J721E_IOPAD(0x12c, PIN_OUTPUT, 8) /* (AG26) PRG0_PRU1_GPO11.GPMC0_A26 */

+ J721E_IOPAD(0x150, PIN_OUTPUT, 8) /* (Y26) PRG0_MDIO0_MDIO.GPMC0_A27 */

+ J721E_IOPAD(0xc4, PIN_INPUT, 8) /* (AC29) PRG0_PRU0_GPO5.GPMC0_AD0 */

+ J721E_IOPAD(0xcc, PIN_INPUT, 8) /* (AC28) PRG0_PRU0_GPO7.GPMC0_AD1 */

+ J721E_IOPAD(0xd0, PIN_INPUT, 8) /* (AC27) PRG0_PRU0_GPO8.GPMC0_AD2 */

+ J721E_IOPAD(0xd4, PIN_INPUT, 8) /* (AB26) PRG0_PRU0_GPO9.GPMC0_AD3 */

+ J721E_IOPAD(0xd8, PIN_INPUT, 8) /* (AB25) PRG0_PRU0_GPO10.GPMC0_AD4 */

+ J721E_IOPAD(0xf4, PIN_INPUT, 8) /* (AB24) PRG0_PRU0_GPO17.GPMC0_AD5 */

+ J721E_IOPAD(0xf8, PIN_INPUT, 8) /* (AB29) PRG0_PRU0_GPO18.GPMC0_AD6 */

+ J721E_IOPAD(0xfc, PIN_INPUT, 8) /* (AB28) PRG0_PRU0_GPO19.GPMC0_AD7 */

+ J721E_IOPAD(0x114, PIN_INPUT, 8) /* (AB27) PRG0_PRU1_GPO5.GPMC0_AD8 */

+ J721E_IOPAD(0x11c, PIN_INPUT, 8) /* (AA24) PRG0_PRU1_GPO7.GPMC0_AD9 */

+ J721E_IOPAD(0x120, PIN_INPUT, 8) /* (AA28) PRG0_PRU1_GPO8.GPMC0_AD10 */

+ J721E_IOPAD(0x124, PIN_INPUT, 8) /* (Y24) PRG0_PRU1_GPO9.GPMC0_AD11 */

+ J721E_IOPAD(0x128, PIN_INPUT, 8) /* (AA25) PRG0_PRU1_GPO10.GPMC0_AD12 */

+ J721E_IOPAD(0x144, PIN_INPUT, 8) /* (Y25) PRG0_PRU1_GPO17.GPMC0_AD13 */

+ J721E_IOPAD(0x148, PIN_INPUT, 8) /* (AA26) PRG0_PRU1_GPO18.GPMC0_AD14 */

+ J721E_IOPAD(0x14c, PIN_INPUT, 8) /* (AA29) PRG0_PRU1_GPO19.GPMC0_AD15 */

+ J721E_IOPAD(0x8, PIN_INPUT, 8) /* (AG22) PRG1_PRU0_GPO1.GPMC0_WAIT0 */

+ J721E_IOPAD(0xc, PIN_INPUT, 8) /* (AF22) PRG1_PRU0_GPO2.GPMC0_WAIT1 */

+ J721E_IOPAD(0x4, PIN_OUTPUT, 8) /* (AC23) PRG1_PRU0_GPO0.GPMC0_BE1n */

+ J721E_IOPAD(0x7c, PIN_OUTPUT, 8) /* (AF21) PRG1_PRU1_GPO9.GPMC0_CSn0 */

+ J721E_IOPAD(0x78, PIN_OUTPUT, 8) /* (Y23) PRG1_PRU1_GPO8.GPMC0_CSn1 */

+ J721E_IOPAD(0x80, PIN_OUTPUT, 8) /* (AB23) PRG1_PRU1_GPO10.GPMC0_CLKOUT */

+ J721E_IOPAD(0x28, PIN_OUTPUT, 8) /* (AG20) PRG1_PRU0_GPO9.GPMC0_ADVn_ALE */

+ J721E_IOPAD(0x24, PIN_OUTPUT, 8) /* (AJ20) PRG1_PRU0_GPO8.GPMC0_OEn_REn */

+ J721E_IOPAD(0x18, PIN_OUTPUT, 8) /* (AD20) PRG1_PRU0_GPO5.GPMC0_WEn */

+ J721E_IOPAD(0x2c, PIN_OUTPUT, 8) /* (AD21) PRG1_PRU0_GPO10.GPMC0_BE0n_CLE */

+ J721E_IOPAD(0x6c, PIN_OUTPUT, 8) /* (AG21) PRG1_PRU1_GPO5.GPMC0_WPn */

+ J721E_IOPAD(0x10, PIN_OUTPUT, 8) /* (AJ23) PRG1_PRU0_GPO3.GPMC0_DIR */

+ >;

+ };

+

+

+

};

&wkup_pmx0 {

@@ -1693,3 +1756,40 @@ eeprom@57 {

reg = <0x57>;

};

};

+

+

+&gpmc0 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&gpmc0_pins_default>;

+ ranges = <0x00 0x00 0x00 0x20000000 0x01000000>; /* CS0 space. Min partition = 16MB */

+

+

+ fpga1111@0,0 {

+ reg = <0 0 0x1000000>;

+ phy_base = <0x20000000>;

+ max_size = <0x01000000>;

+ status = "okay";

+ gpmc,device-width = <2>;

+ gpmc,sync-clk-ps = <0>;

+ gpmc,cs-on-ns = <0>;

+ gpmc,cs-rd-off-ns = <120>;

+ gpmc,cs-wr-off-ns = <120>;

+ gpmc,adv-on-ns = <12>;

+ gpmc,adv-rd-off-ns = <48>;

+ gpmc,adv-wr-off-ns = <48>;

+ gpmc,we-on-ns = <54>;

+ gpmc,we-off-ns = <110>;

+ gpmc,oe-on-ns = <54>;

+ gpmc,oe-off-ns = <110>;

+ gpmc,access-ns = <114>;

+ gpmc,rd-cycle-ns = <120>;

+ gpmc,wr-cycle-ns = <120>;

+ gpmc,bus-turnaround-ns = <0>;

+ gpmc,cycle2cycle-delay-ns = <50>;

+ gpmc,cycle2cycle-diffcsen;

+ gpmc,clk-activation-ns = <0>;

+ gpmc,wr-access-ns = <120>;

+ gpmc,wr-data-mux-bus-ns = <90>;

+

+ };

+};

diff --git a/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

index 639fa31b5..bad226848 100644

--- a/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

@@ -2809,13 +2809,24 @@ dphy1: phy@4590000 {

power-domains = <&k3_pds 148 TI_SCI_PD_EXCLUSIVE>;

};

+ gpmc0: memory-controller@5390000 {

+ compatible = "ti,am3352-gpmc";

+ ti,hwmods = "gpmc";

+ power-domains = <&k3_pds 80 TI_SCI_PD_EXCLUSIVE>;

+ clocks = <&k3_clks 80 0>;

+ clock-names = "fck";

+ reg = <0x00 0x05390000 0x00 0x400>,

+ <0x00 0x20000000 0x00 0x8000000>;

+ reg-names = "cfg", "data";

+ interrupts = <GIC_SPI 106 IRQ_TYPE_LEVEL_HIGH>;

+ gpmc,num-cs = <4>;

+ gpmc,num-waitpins = <2>;

+ #address-cells = <2>;

+ #size-cells = <1>;

+ interrupt-controller;

+ #interrupt-cells = <2>;

+ gpio-controller;

+ #gpio-cells = <2>;

};

};

diff --git a/arch/arm64/boot/dts/ti/k3-j721e.dtsi b/arch/arm64/boot/dts/ti/k3-j721e.dtsi

index 36a650fe6..0928f0298 100644

--- a/arch/arm64/boot/dts/ti/k3-j721e.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721e.dtsi

@@ -140,6 +140,8 @@ cbass_main: bus@100000 {

<0x00 0x6f000000 0x00 0x6f000000 0x00 0x00310000>, /* A72 PERIPHBASE */

<0x44 0x00000000 0x44 0x00000000 0x00 0x08000000>, /* PCIe2 DAT */

<0x44 0x10000000 0x44 0x10000000 0x00 0x08000000>, /* PCIe3 DAT */

+ <0x00 0x05390000 0x00 0x05390000 0x00 0x00000400>, /* gpmc cfg */

+ <0x00 0x20000000 0x00 0x20000000 0x00 0x08000000>, /* gpmc data */

<0x4d 0x80800000 0x4d 0x80800000 0x00 0x00800000>, /* C66_0 */

<0x4d 0x81800000 0x4d 0x81800000 0x00 0x00800000>, /* C66_1 */

<0x4e 0x20000000 0x4e 0x20000000 0x00 0x00080000>, /* GPU */

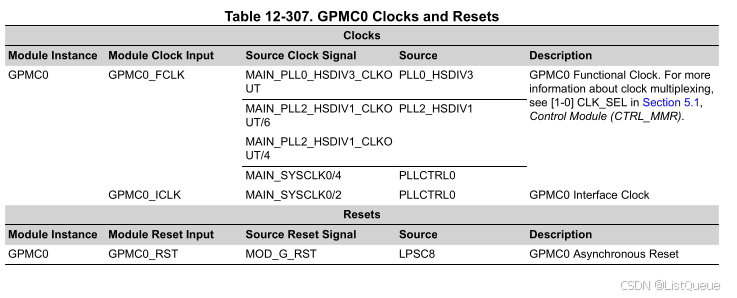

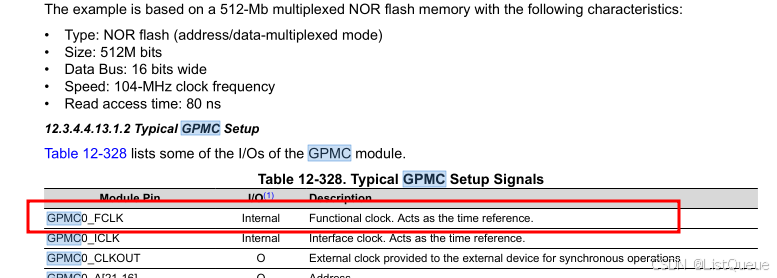

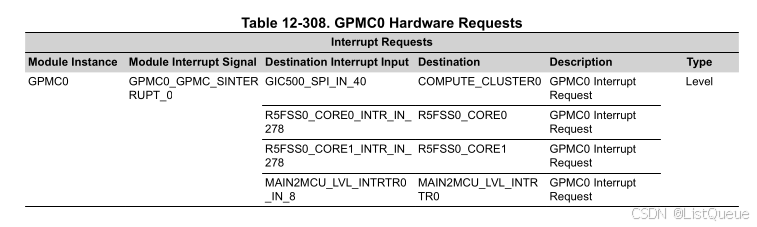

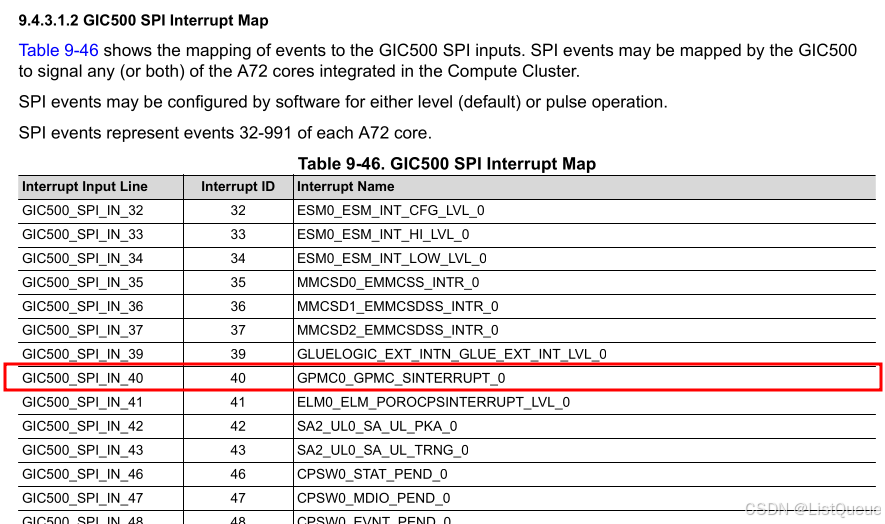

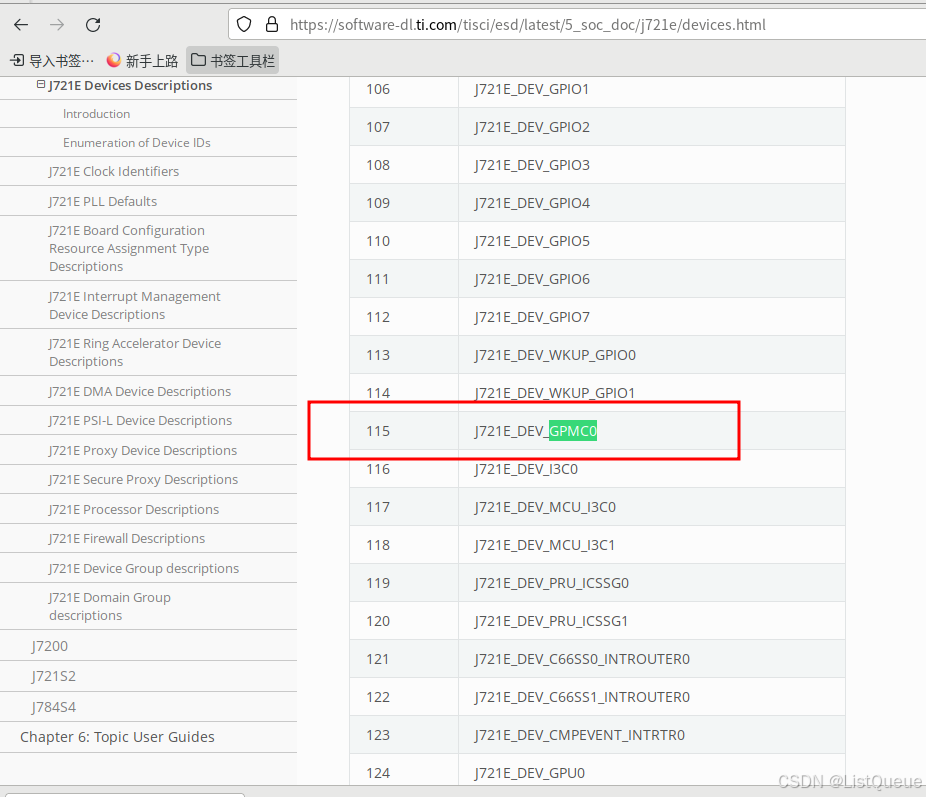

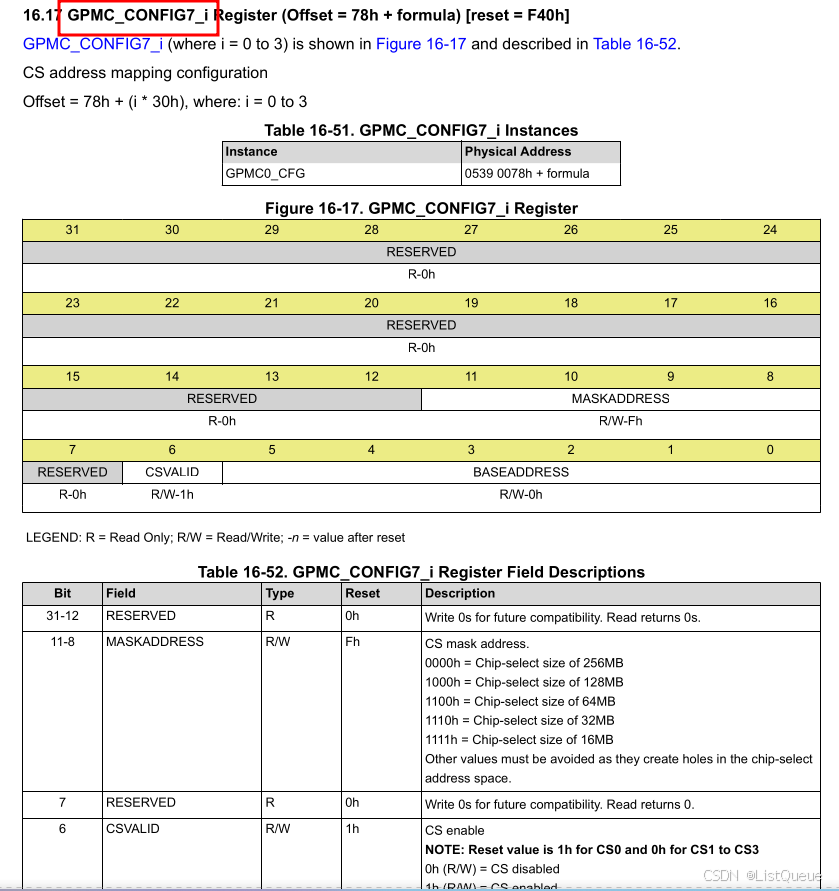

对于关键参数的设置说明:

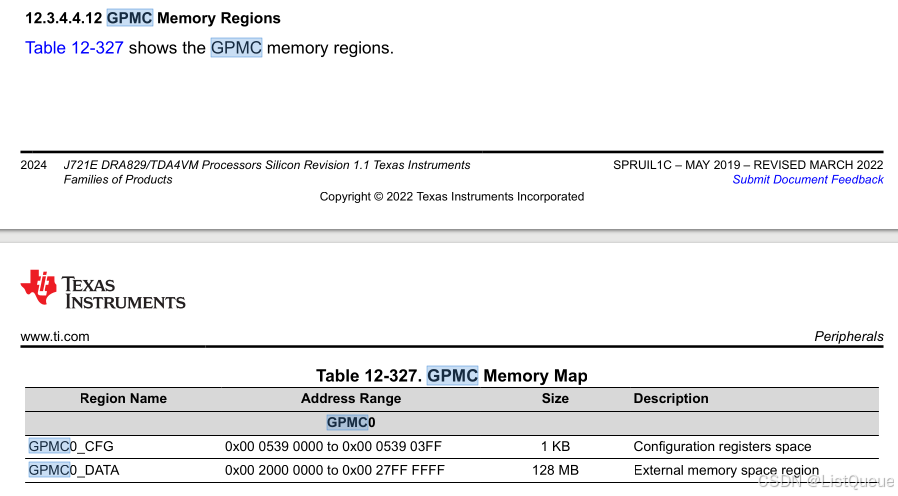

设备树配置的:

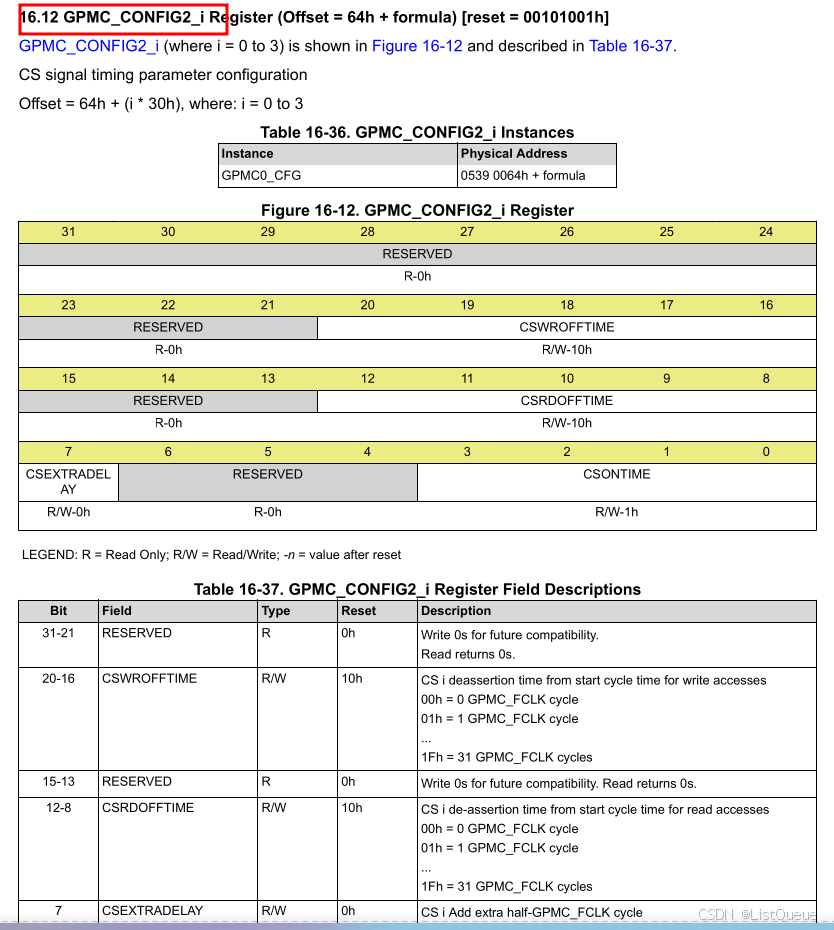

reg = <0x00 0x05390000 0x00 0x400>, <0x00 0x20000000 0x00 0x8000000>; reg-names = "cfg", "data";

对应文档:

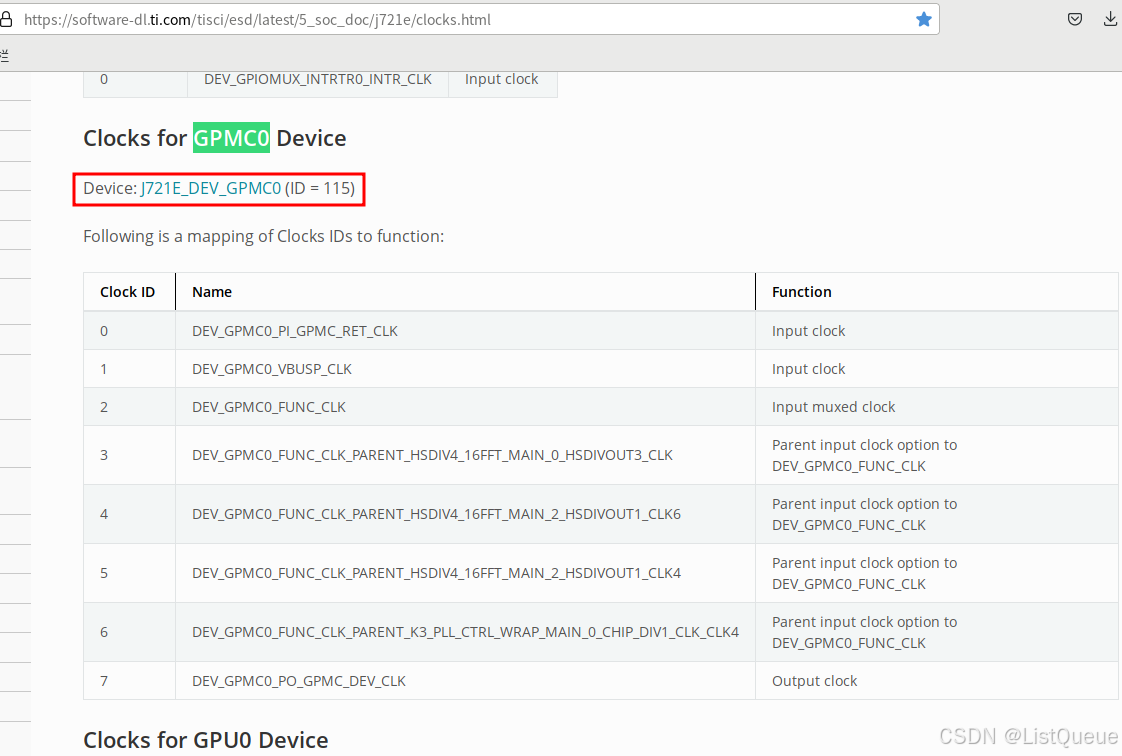

设备树配置:

clocks = <&k3_clks 115 0>; clock-names = "fck";

interrupts = <GIC_SPI 8 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 115 TI_SCI_PD_EXCLUSIVE>;

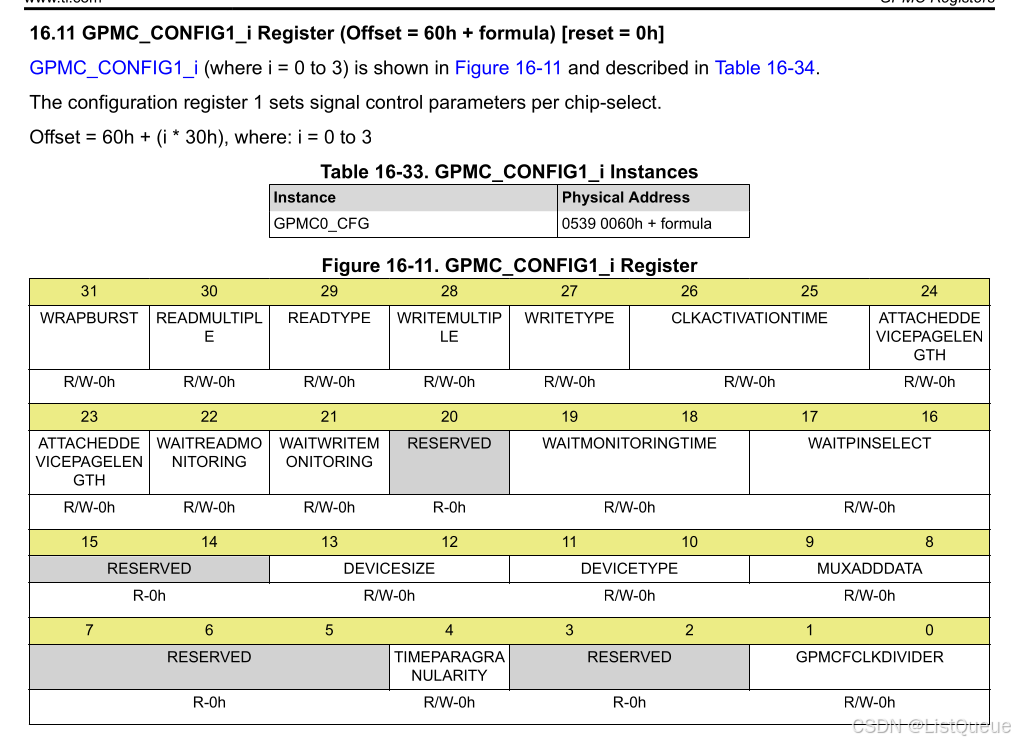

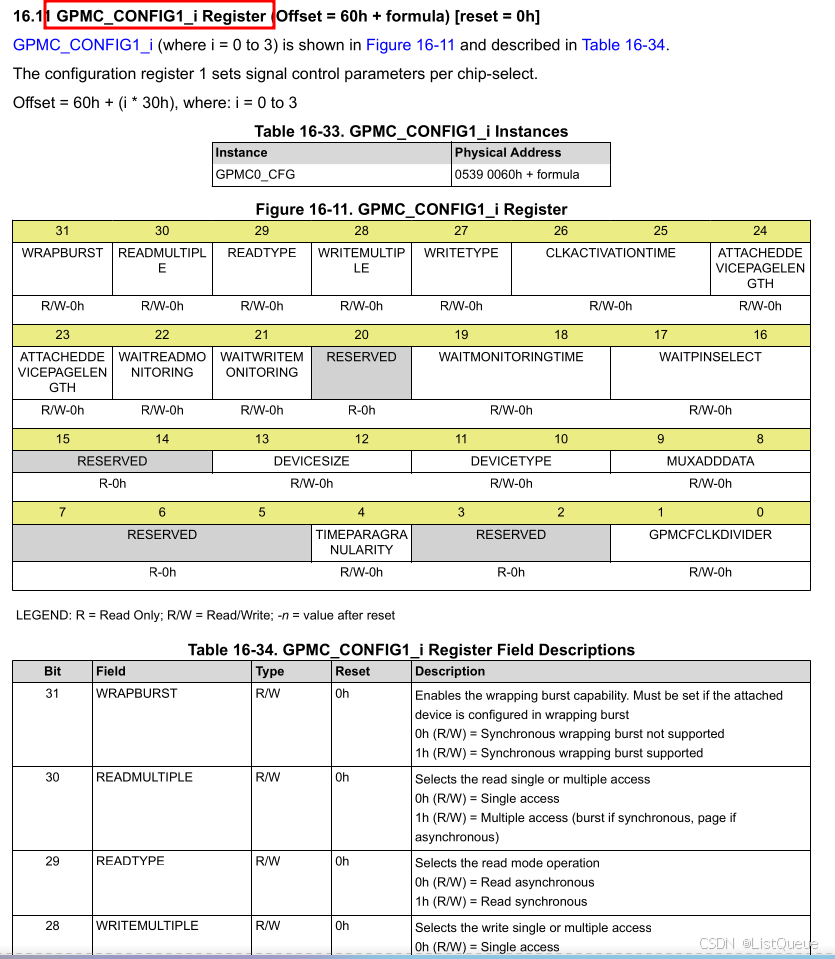

对config1寄存器主要用于配置片寻的模式,比如数据突发模式,同步或者异步模式,地址和数据是16位还是8位模式等

ranges = <0 0 0x00 0x21000000 0x01000000>; /* CS0 space. Min partition = 16MB */

----------------------------------------------------------------------------------------------------------------------------

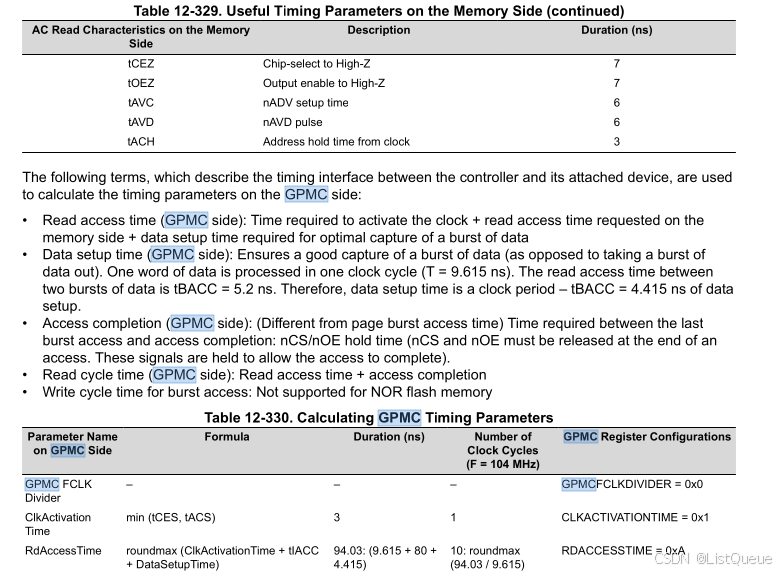

真正的难度在于如何调整好时序的问题,即如下设备的配置这部分:

+ fpga1@0,0 {

+ reg = <0 0 0x1000000>;

+ phy_base = <0x20000000>;

+ max_size = <0x01000000>;

+ status = "okay";

+ gpmc,device-width = <2>;

+ gpmc,sync-clk-ps = <0>;

+ gpmc,cs-on-ns = <0>;

+ gpmc,cs-rd-off-ns = <120>;

+ gpmc,cs-wr-off-ns = <120>;

+ gpmc,adv-on-ns = <12>;

+ gpmc,adv-rd-off-ns = <48>;

+ gpmc,adv-wr-off-ns = <48>;

+ gpmc,we-on-ns = <54>;

+ gpmc,we-off-ns = <110>;

+ gpmc,oe-on-ns = <54>;

+ gpmc,oe-off-ns = <110>;

+ gpmc,access-ns = <114>;

+ gpmc,rd-cycle-ns = <120>;

+ gpmc,wr-cycle-ns = <120>;

+ gpmc,bus-turnaround-ns = <0>;

+ gpmc,cycle2cycle-delay-ns = <50>;

+ gpmc,cycle2cycle-diffcsen;

+ gpmc,clk-activation-ns = <0>;

+ gpmc,wr-access-ns = <120>;

+ gpmc,wr-data-mux-bus-ns = <90>;

+

+ };

+};

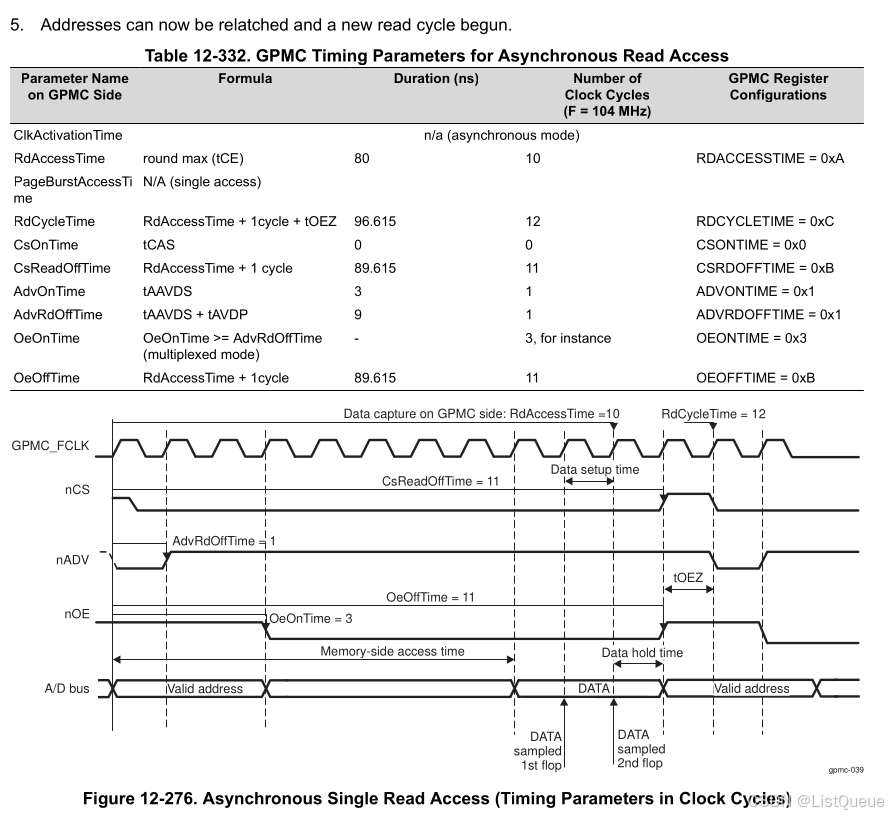

读时序:

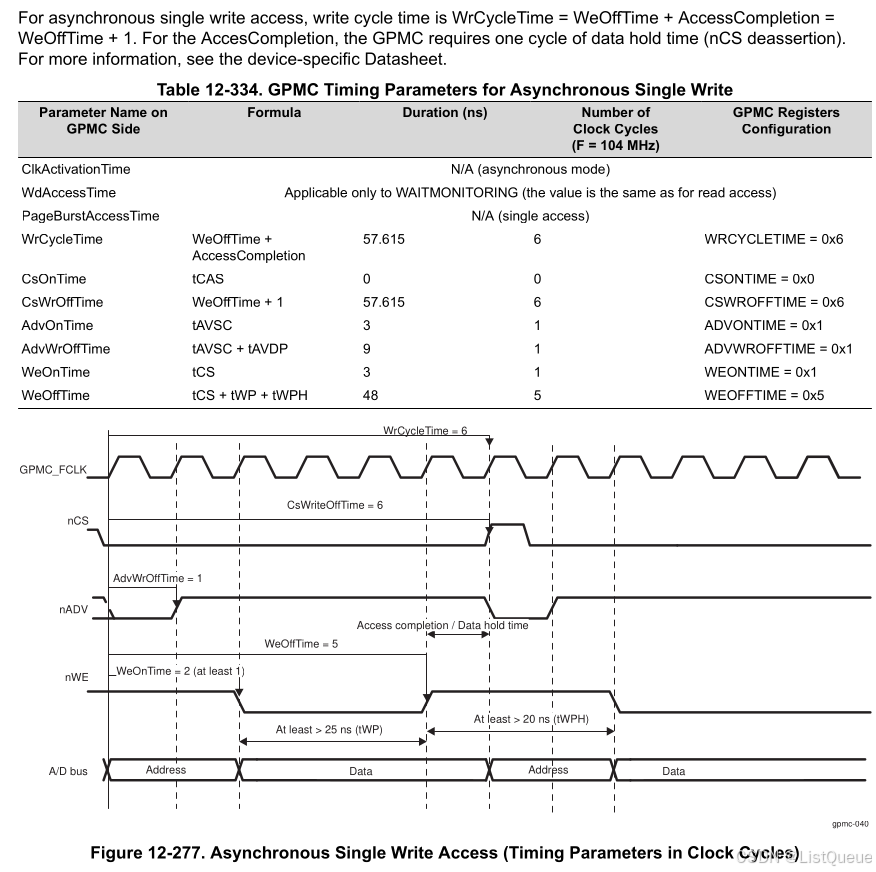

写时序:

解析:

必要的属性(Required properties):

bank-width: NOR Flash字节宽度。GPMC支持8位和16位设备,因此必须是1个或2个字节。

compatible: 参见文档Documentation/devicetree/bindings/mtd/mtd-physmap.txt

gpmc,cs-on-ns: 片选有效前的时间间隔 (从芯片手册的时序上看,CSONTIME是ADV拉高到CS拉低之间的时间段,是否应该理解成片选有效前的时间间隔)

gpmc,cs-rd-off-ns: 读操作时,片选无效前的时间间隔

gpmc,cs-wr-off-ns: 写操作时,片选无效前的时间间隔

gpmc,oe-on-ns: 读使能有效前的时间间隔

gpmc,oe-off-ns: 读使能无效前的时间间隔

gpmc,we-on-ns: 写使能有效前的时间间隔

gpmc,we-off-ns: 写使能无效前的时间间隔

gpmc,access-ns: 从开始循环到第一个数据捕获(读访问)

gpmc,rd-cycle-ns: 总的读操作循环时间

gpmc,wr-cycle-ns: 总的写操作循环时间

linux,mtd-name: 参见Documentation/devicetree/bindings/mtd/mtd-physmap.txt

reg: Chip-select, base address (relative to chip-select) and size of NOR flash. Note that base address will be typically 0

as this is the start of the chip-select.

可选的属性(Optional properties):

gpmc,XXX 额外的GPMC时序和配置参数。参见Documentation/devicetree/bindings/memory-controllers/omap-gpmc.txt

可选的分区表属性解析:

#address-cells: should be set to 1

#size-cells: should be set to 1

必要的属性:

compatible:

reg: 寄存器空间的一个源指示符

ti,hwmods: 应该设置为“tI,gpmc”直到DT发送结束

#address-cells: 必须设置为 2 用以允许内存地址转换

#size-cells: 必须设置为1用以允许内存映射

gpmc,num-cs: 控制器支持的最大片选数

gpmc,num-waitpins: 控制器支持的最大wait引脚数

ranges: 每一个片选必须设置成能够反映内存布局的4个整型数值:

0

目前,从每一个片选寄存器 GPMC_CONFIG7(由引导加载程序设置)推导的计算值被用于物理地址的解码。由于这些值在以后会被改变,必须填充正确的值。

interrupt-controller: GPMC 驱动程序和中断控制器为实现NAND事件“fifoevent”和“termcount”在GPMC_WAIT引脚的上升/下降边沿触发添砖加瓦。

中断号映射如下:

0 – NAND_fifoevent

1 - NAND_termcount

2 - GPMC_WAIT0 pin edge

3 - GPMC_WAIT1 pin edge, and so on.

interrupt-cells: 必须设置为2

gpio-controller: GPMC驱动为GPMC WAIT引脚实现了一个GPIO控制器,该引脚可以被用作普通目的的输入。 0 映射到GPMC_WAIT0引脚。

gpio-cells: 必须设置为2

必要的属性当使用NAND预读取dma时:

dmas GPMC NAND 预读取dma通道

dma-names 必须设置为“rxtx”

子节点的时序属性。所有选项都是可选的并且默认是0.

gpmc,sync-clk-ps: 同步模式下最小的时钟周期,单位皮秒ps

与GPMC_CONFIG2相关的片选信号时序(单位ns)

gpmc,cs-on-ns: Assertion time

gpmc,cs-rd-off-ns: Read deassertion time

gpmc,cs-wr-off-ns: Write deassertion time

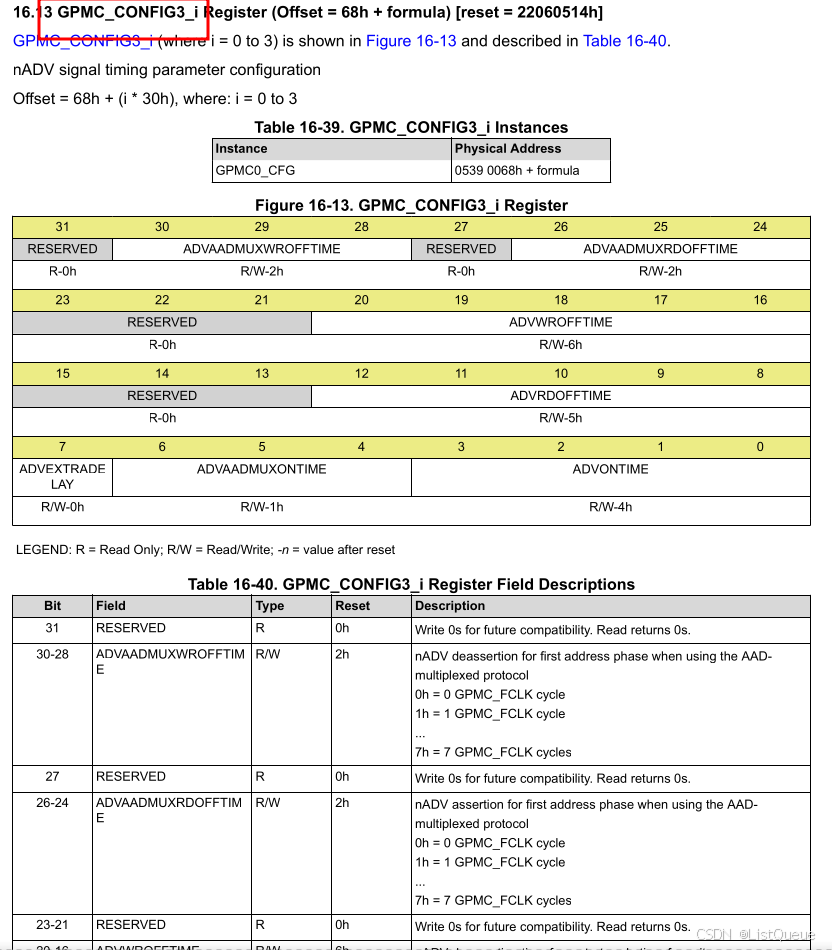

与GPMC_CONFIG3相关的ADV信号时序(单位ns)

gpmc,adv-on-ns: Assertion time

gpmc,adv-rd-off-ns: Read deassertion time

gpmc,adv-wr-off-ns: Write deassertion time

gpmc,adv-aad-mux-on-ns: Assertion time for AAD

gpmc,adv-aad-mux-rd-off-ns: Read deassertion time for AAD

gpmc,adv-aad-mux-wr-off-ns: Write deassertion time for AAD

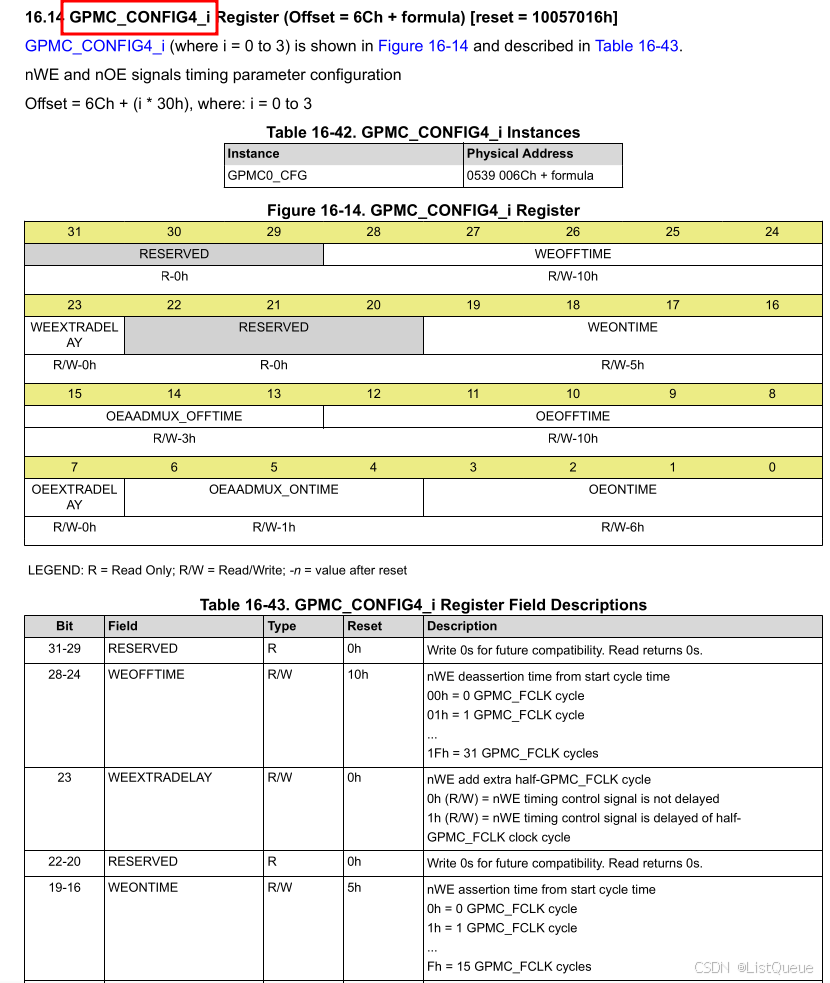

与GPMC_CONFIG4相关的WE信号时序(单位ns)

gpmc,we-on-ns: Assertion time

gpmc,we-off-ns: Deassertion time

与GPMC_CONFIG4相关的OE信号时序(单位ns)

gpmc,oe-on-ns: Assertion time

gpmc,oe-off-ns: Deassertion time

gpmc,oe-aad-mux-on-ns: Assertion time for AAD

gpmc,oe-aad-mux-off-ns: Deassertion time for AAD

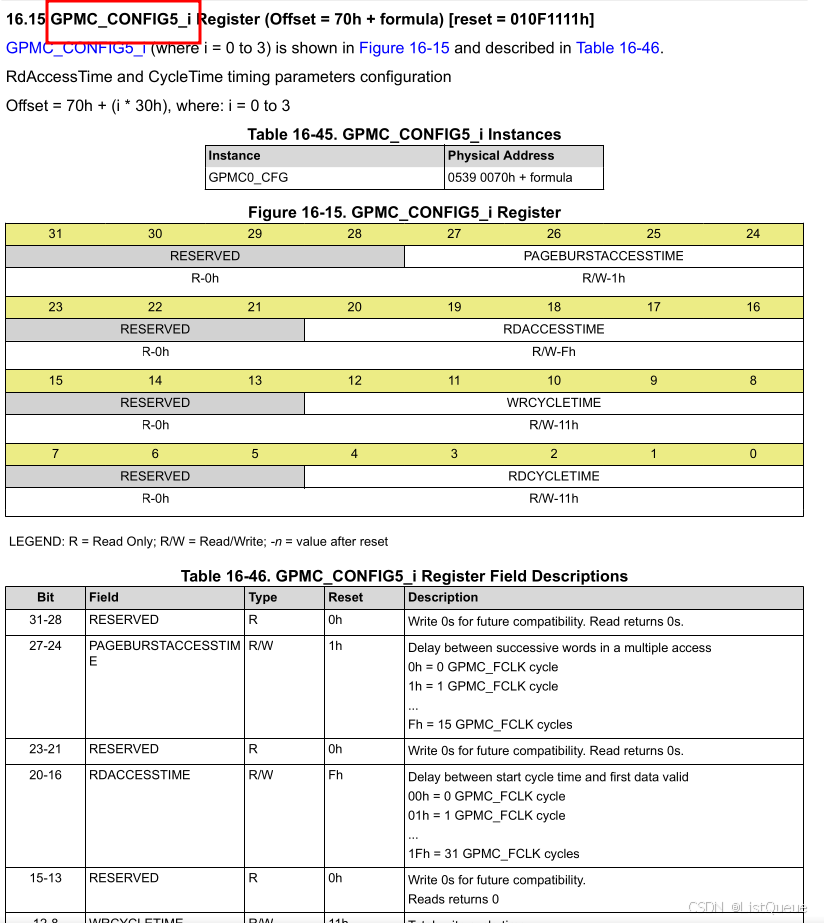

与GPMC_CONFIG5相关的Access time 和cycle time时序(单位ns)

gpmc,page-burst-access-ns: Multiple access word delay

gpmc,access-ns: Start-cycle to first data valid delay

gpmc,rd-cycle-ns: Total read cycle time

gpmc,wr-cycle-ns: Total write cycle time

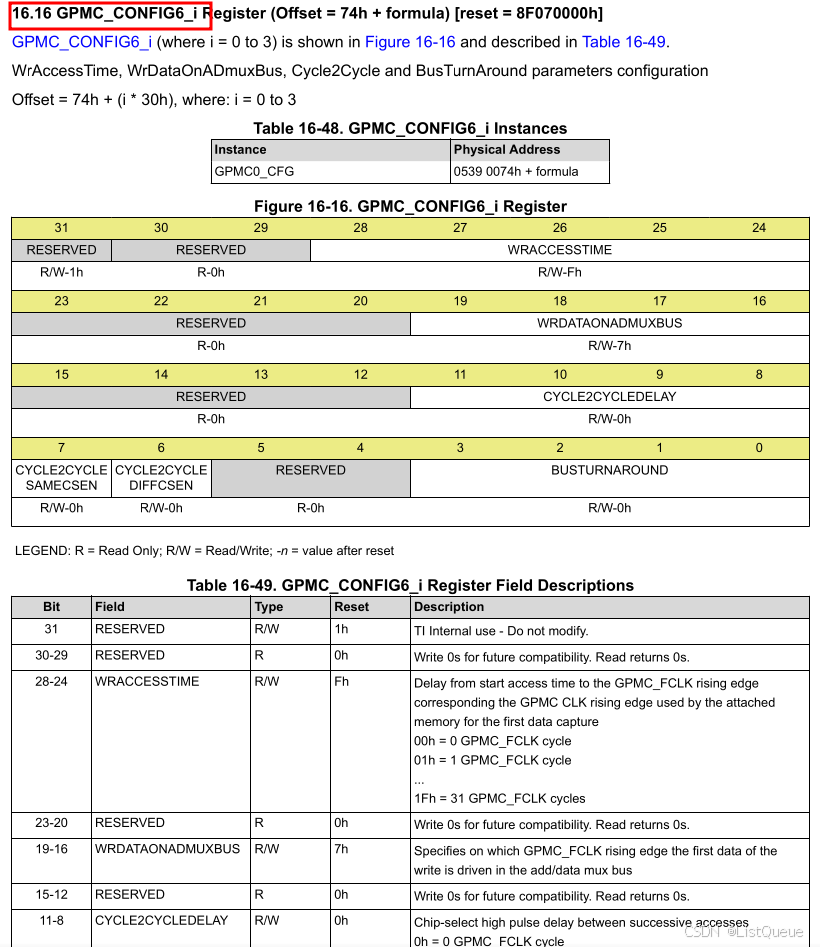

gpmc,bus-turnaround-ns: Turn-around time between successive accesses

gpmc,cycle2cycle-delay-ns: Delay between chip-select pulses

gpmc,clk-activation-ns: GPMC clock activation time

gpmc,wait-monitoring-ns: Start of wait monitoring with regard to valid data

布尔时序参数。如果属性有参数,则启用。如果省略属性,则禁用。

gpmc,adv-extra-delay: ADV signal is delayed by half GPMC clock

gpmc,cs-extra-delay: CS signal is delayed by half GPMC clock

gpmc,cycle2cycle-diffcsen: Add “cycle2cycle-delay” between successive

accesses to a different CS

gpmc,cycle2cycle-samecsen: Add “cycle2cycle-delay” between successive

accesses to the same CS

gpmc,oe-extra-delay: OE signal is delayed by half GPMC clock

gpmc,we-extra-delay: WE signal is delayed by half GPMC clock

gpmc,time-para-granularity: Multiply all access times by 2

7个配置寄存器的定义

1、配置设备类型 GPMC_CONFIG1

2、配置访问时序,主要读写时序 GPMC_CONFIG2~6

3、配置基地址、容量(即掩码地址)、使能CS信号 GPMC_CONFIG7

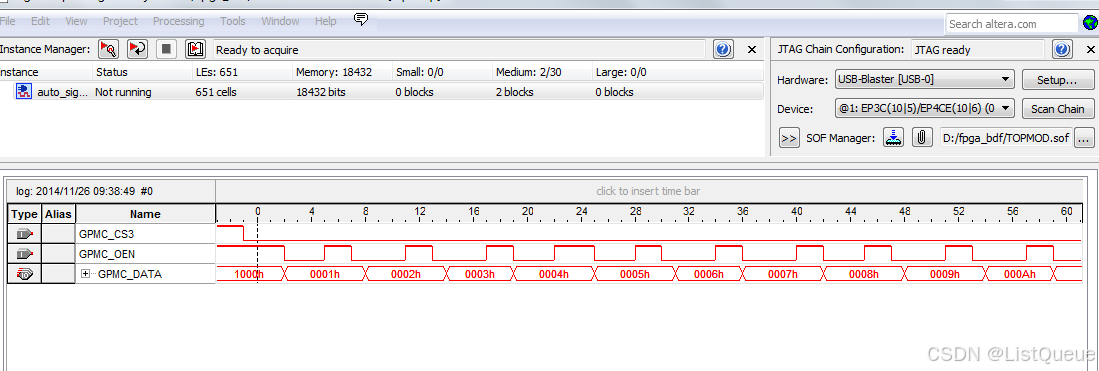

逻辑分析仪:

测试验证:

烧录FPGA程序后,linux端进行测试:

1、对0x20002468读出来数据为0x55aa,然后可以自定义的读写。

2、对0x20004000连续写入几个值,然后从0x20004002再读出几个值,看是否写入和读出是一致的。

root@tda4vm-sk:~# devmem2 0x20004000 h 0x1111;

/dev/mem opened.

Memory mapped at address 0xffff970aa000.

Read at address 0x20004000 (0xffff970aa000): 0x0100

Write at address 0x20004000 (0xffff970aa000): 0x1111, readback 0x1111

root@tda4vm-sk:~# devmem2 0x20004000 h 0x1112;

/dev/mem opened.

Memory mapped at address 0xffffa9546000.

Read at address 0x20004000 (0xffffa9546000): 0x0100

Write at address 0x20004000 (0xffffa9546000): 0x1112, readback 0x1112

root@tda4vm-sk:~# devmem2 0x20004000 h 0x1113;

/dev/mem opened.

Memory mapped at address 0xffff9ac29000.

Read at address 0x20004000 (0xffff9ac29000): 0x0100

Write at address 0x20004000 (0xffff9ac29000): 0x1113, readback 0x1113

root@tda4vm-sk:~# devmem2 0x20004002 h;

/dev/mem opened.

Memory mapped at address 0xffffadbee000.

Read at address 0x20004002 (0xffffadbee002): 0x1111

root@tda4vm-sk:~# devmem2 0x20004002 h;

/dev/mem opened.

Memory mapped at address 0xffffb7ef7000.

Read at address 0x20004002 (0xffffb7ef7002): 0x1112

root@tda4vm-sk:~# devmem2 0x20004002 h;

/dev/mem opened.

Memory mapped at address 0xffff8e6f7000.

Read at address 0x20004002 (0xffff8e6f7002): 0x1113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?