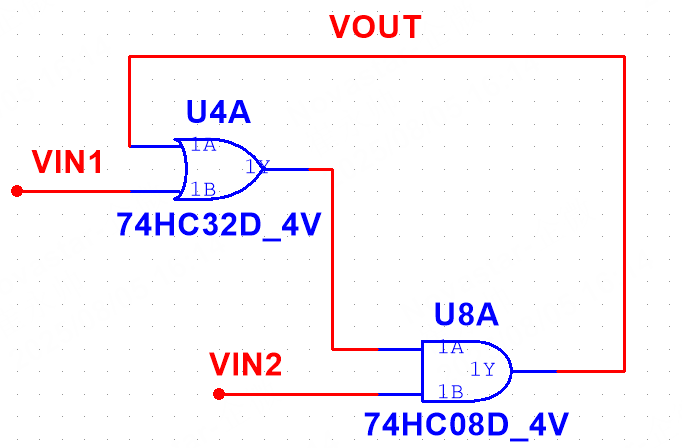

根据提供的连接关系,我们可以整理出以下逻辑电路结构:

-

74HC32(或门):

- 1A:连接到 74HC08(与门) 的 1Y(输出)。

- 1B:输入信号 VIN1。

- 1Y(输出):连接到 74HC08(与门) 的 1A。

-

74HC08(与门):

- 1A:连接到 74HC32(或门) 的 1Y(输出)。

- 1B:输入信号 VIN2。

- 1Y(输出):作为最终输出 VOUT,并反馈到 74HC32 的 1A。

逻辑表达式推导:

-

74HC32(或门) 的输出 1Y:

[

1Y=1A OR 1B=(1YAND) OR VIN11Y = 1A \ \text{OR} \ 1B = (1Y_{AND}) \ \text{OR} \ VIN11Y=1A OR 1B=(1YAND) OR VIN1

]

但这里 1A 是 74HC08 的 1Y,即:

[

1YOR=VOUT OR VIN11Y_{OR} = VOUT \ \text{OR} \ VIN11YOR=VOUT OR VIN1

] -

74HC08(与门) 的输出 1Y(VOUT):

[

VOUT=1A AND 1B=(1YOR) AND VIN2VOUT = 1A \ \text{AND} \ 1B = (1Y_{OR}) \ \text{AND} \ VIN2VOUT=1A AND 1B=(1YOR) AND VIN2

]

代入 1Y_{OR}:

[

VOUT=(VOUT OR VIN1) AND VIN2VOUT = (VOUT \ \text{OR} \ VIN1) \ \text{AND} \ VIN2VOUT=(VOUT OR VIN1) AND VIN2

]

电路行为分析:

这是一个 带有反馈的组合逻辑电路,其行为取决于 VIN1 和 VIN2 的输入状态:

-

当 VIN2 = 0:

- 无论 VOUT OR VIN1 是什么,VOUT = 0(因为与门的特性)。

- 电路输出被强制拉低。

-

当 VIN2 = 1:

- 电路简化为:

[

VOUT=VOUT OR VIN1VOUT = VOUT \ \text{OR} \ VIN1VOUT=VOUT OR VIN1

] - 如果 VIN1 = 1,则 VOUT = 1(无论之前的状态)。

- 如果 VIN1 = 0,则 VOUT 保持之前的值(锁存效应)。

- 电路简化为:

电路功能:

- 当 VIN2 = 1 时:

- VIN1 作为 置位(Set)信号:

- 若 VIN1 = 1,则 VOUT = 1(锁存高电平)。

- 若 VIN1 = 0,VOUT 保持原状态(类似锁存器或 SR 锁存器的 Set 功能)。

- VIN1 作为 置位(Set)信号:

- 当 VIN2 = 0 时:

- VOUT 强制为 0(复位功能)。

可能的用途:

- 简易锁存器:通过 VIN1 设置高电平,通过 VIN2 复位。

- 使能控制:VIN2 作为使能信号,VIN1 作为触发信号。

- 防抖动逻辑:在按键或开关电路中用于稳定输出。

真值表(假设初始 VOUT = 0):

| VIN1 | VIN2 | VOUT |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 0 | 1 | 保持(上次值) |

| 1 | 1 | 1 |

总结:

这是一个 基于或门和与门的简易锁存电路,VIN2 控制输出使能,VIN1 在 VIN2 = 1 时设置输出高电平。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?