一.什么是全加器

1.概念

全加器是能够计算低位进位的二进制加法电路为一位全加器。而半加器电路指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。

一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

2.一位全加器

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci [1]

二.实现

1.新建

启动Quartus-||,新建工程选择芯片EP4CE115F29C7芯片。

2.绘制原理图

如图

3.仿真

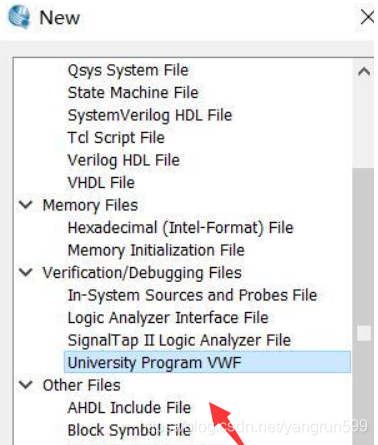

选择VWF

添加有关选项

本文详细介绍了如何使用Quartus-II软件设计一个1位全加器,从全加器的概念到具体实现步骤,包括新建工程、绘制原理图、仿真、保存配置,再到Verilog代码实现和硬件测试,全面展示了设计过程。

本文详细介绍了如何使用Quartus-II软件设计一个1位全加器,从全加器的概念到具体实现步骤,包括新建工程、绘制原理图、仿真、保存配置,再到Verilog代码实现和硬件测试,全面展示了设计过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3348

3348

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?