AR# 56610

Vivado IP Integrator - "ERROR [BD 41-237] Bus Interface property FREQ_HZ does not match between /mig_7series/S_AXI() and interconnect_1/s00_couplers/M_AXI()"

描述

In a simple Vivado IP Integrator system with a mig_7series, the IP connects to an external AXI interface via a AXI Interconnect.

However, during Generate Output Products, an error similar to the following occurs:

ERROR [BD 41-237] Bus Interface property FREQ_HZ does not match between /mig_7series/S_AXI(166250000) and interconnect_1/s00_couplers/M_AXI(10000000)

How can I fix this issue?

解决方案

If an AXI interface is made external, the FREQ_HZ property will default to 100MHz.

As a result, you will have to manually update this in the External Interface Properties for the AXI, and the External Port Properties for the S00_ACLK.

In the example above, you need to change this to 166250000.

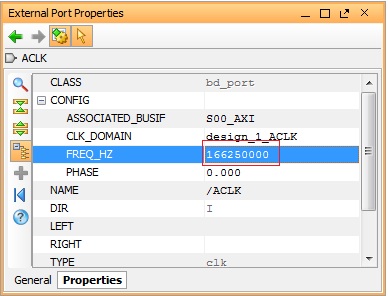

To change the FREQ_HZ property, highlight the external interface port in the block diagram and drop down the CONFIG, then modify the FREQ_HZ to the required Frequency in the External Port Properties GUI:

Repeat this for the External Port Properties too.

Again, highlight the external clock port connected to the ACLK (in this example S00_ACLK).

本文介绍如何解决在Vivado IP Integrator中使用mig_7series时遇到的FREQ_HZ属性不匹配错误。通过手动更新外部接口属性中的FREQ_HZ值,可以避免在生成输出产品时出现错误。

本文介绍如何解决在Vivado IP Integrator中使用mig_7series时遇到的FREQ_HZ属性不匹配错误。通过手动更新外部接口属性中的FREQ_HZ值,可以避免在生成输出产品时出现错误。

8020

8020

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?